IEDM 2016

Speicher: Evolution und Revolution

Fortsetzung des Artikels von Teil 1

DRAM-Technologie

Bis zu Prozessstrukturen von 2x nm konnten die DRAM-Hersteller mithilfe der Skalierung die Performance steigern und die Kosten senken. Mit Strukturgrößen von unter 1x nm geht das aber nicht mehr, hier fordert Lee vielmehr eine Co-Optimierung von Prozess, Baustein, Schaltung und System, denn nur dann könnten die technischen sowie kommerziellen Probleme dieser fortschreitenden Skalierung überwunden werden.

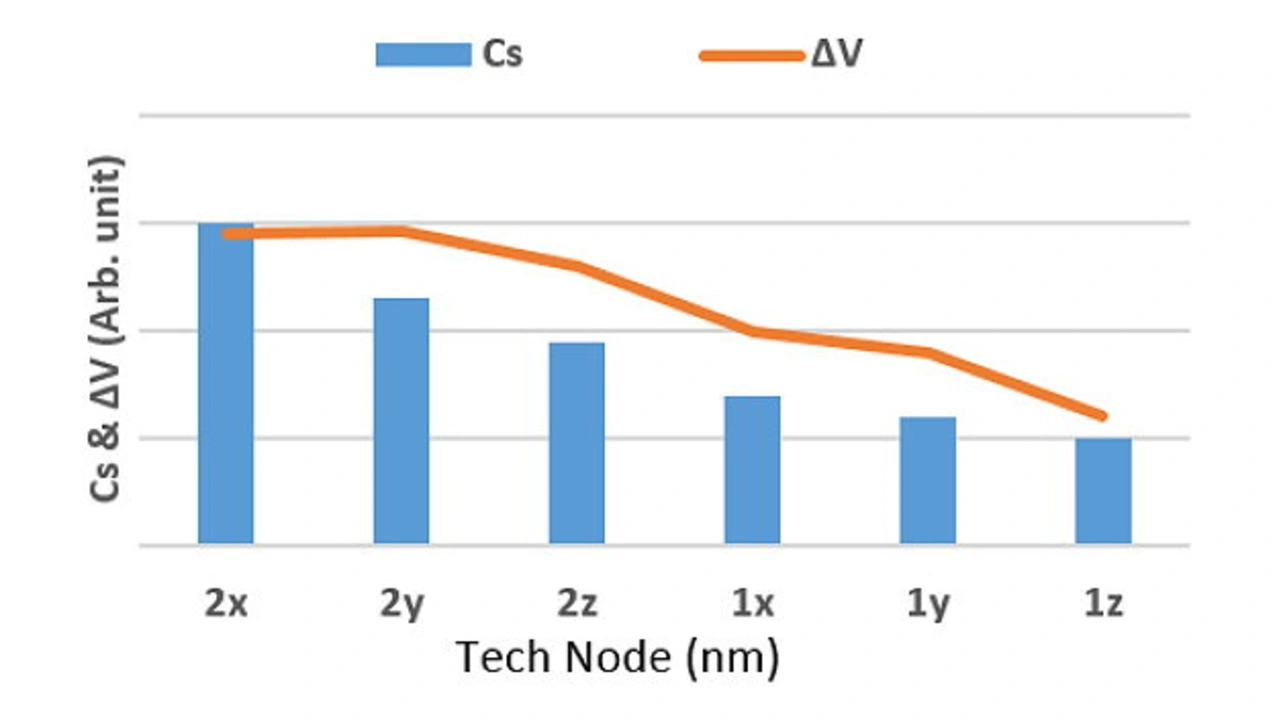

Und gerade auf der technischen Seite sieht Lee doch einige Schwierigkeiten, die überwunden werden müssen, um auf der evolutionären Schiene weiterfahren zu können. Beispielsweise sind die kürzere Retention-Zeit und die verringerte Zellkapazität (Cs) ein Problem. Denn mit kleineren Strukturen werden die Kondensatoren und damit die Kapazitäten kleiner, was wiederum die Retention-Zeit verkürzt. Hinzu kommt noch, dass mit der verringerten Kapazität auch der Signalhub (ΔV) immer geringer ausfällt. Außerdem führt das hohe Seitenverhältnis (aspect ratio) zu immer mehr Problemen auf der Fertigungsseite. Lee glaubt, dass mit neuen Kondensatorformen (Pillar-Typ) eine gewisse Erleichterung eintritt, aber um auch in Zukunft mit noch kleineren Geometrien noch vernünftige Kapazitätswerte hinzubekommen, bleibt ein Riesenproblem.

Jobangebote+ passend zum Thema

Um dem Problem mit der verkürzten Retention-Zeit zu begegnen, werden beispielsweise kürzere Refresh-Zyklen (unterhalb der typischen 64 ms) genutzt. Außerdem wurden teilweise PPR-Ansätze (PPR: Post Package Repair) genutzt, um Bit-Fehler nach dem Packaging-Prozess zu beheben. Lee glaubt, dass in Zukunft aber neue Design-Ansätze wie On-Die-ECC genutzt werden müssen, um mögliche Bit-Fehler aufgrund variierender Retention-Zeiten (VRT) zu kompensieren. Lee: »Solche Hilfsschaltungen würden die Zuverlässigkeit der Produkte deutlich erhöhen.«

Dadurch, dass die Skalierung des Gate-Oxids verlangsamt wurde, hat sich auch die Performance-Steigerung der Peripherie-Transistoren verlangsamt. Um aber die Anforderungen zukünftiger Speicherschnittstellen und Low-Voltage-Betrieb erfüllen zu können, müsse die Leistungsfähigkeit der Peripherie-Transistoren verbessert werden, so Lee. Deshalb denken auch die DRAM-Hersteller über HKMG nach. Allerdings sei es aufgrund der höheren Prozesstemperaturen in der DRAM-Fertigung nicht möglich, die bereits entwickelten HKMG-Prozesse aus der Logikwelt direkt nutzen. Lee mahnt außerdem: die Speicherindustrie ist von Natur aus sehr kostensensitiv, also müssen wir einen kostengünstigen Weg finden, solche Prozesse zu implementieren.«

Kosten sind in der Speicherwelt sowieso ein sehr heikles Thema. Und die Skalierung ermöglicht bekanntermaßen kaum noch die Möglichkeit, die Kosten zu senken. Denn im Speicherbereich werden die Kosten zum Großteil durch die Kosten für die Prozessierung des Wafers und durch die Anzahl an Bits pro Wafer festgelegt. Dementsprechend hart trifft es natürlich auch die DRAM-Hersteller, dass die Prozessierung der Wafer mit immer kleineren Strukturen deutlich teurer wird, denn bekanntermaßen sind Prozessschritte wie Double-Patterning etc. extrem kostspielig. Lee glaubt zwar, dass EUV hier theoretisch weiterhelfen könnte, doch die Technologie ist bei weitem noch nicht so weit in einer hochvolumigen Fertigung zum Einsatz zu kommen. Deshalb setzt Lee größere Hoffnungen auf neue Zellanordnungen und -architekturen, allerdings unter der Voraussetzung, dass sie bei einer weiteren Skalierung die Prozesskosten nur geringfügig erhöhen. Diese Voraussetzungen könnten VG-Zellstrukturen (VG: vertikales Gate) erfüllen und VG-Transistoren zeichnen sich durch ein großen Hub zwischen 0 und 1 und geringe parasitäre Bitleitungs-Kapazitäten aus. Aber Lee betont abermals: »Es ist wichtig eine technische Lösung zu finden, die ökonomisch sinnvoll ist. VG scheint ein guter Ansatz zu sein, allerdings gibt es hier noch viele Unbekannte.«