Für eine nachhaltige Leistungselektronik

SiC und die unterschiedlichen Zellstrukturen

Fortsetzung des Artikels von Teil 1

SiC-Dioden versus Si-Dioden

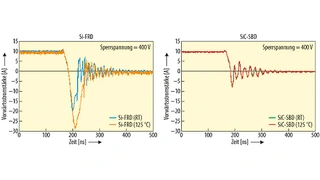

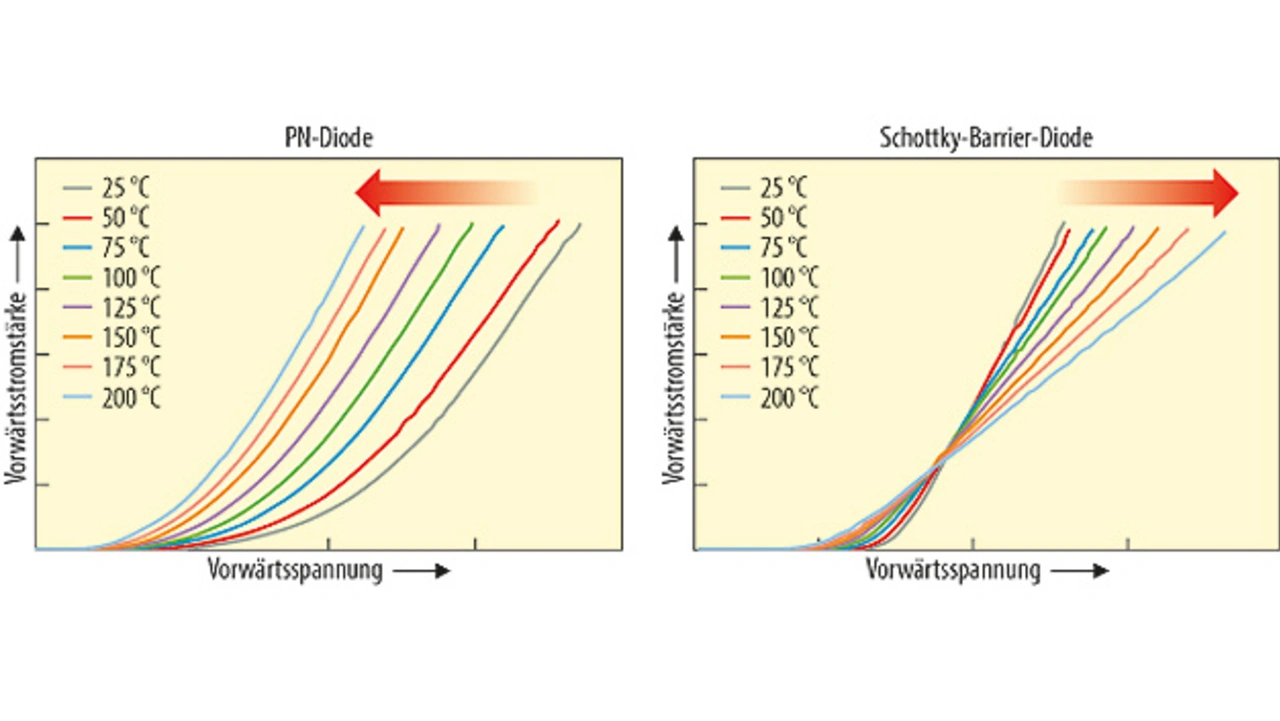

Im Vergleich zu den Si-Dioden sind die SiC-Schottky-Barrier-Dioden (SiC-SBD) sehr viel attraktivere Bauteile für Leistungselektronikanwendungen, vor allem ab einer Spannung von 600 V. Diese sind nämlich aufgrund der niedrigeren Schaltverluste und des Wegfalls der sogenannten Rückstromspitze beim Ausschalten der Diode wesentlich effizienter (Bild 5). Demzufolge werden die Störaussendungen entsprechend reduziert. Dies verbessert das EMI-Verhalten des gesamten Systems.

Jobangebote+ passend zum Thema

SiC-Dioden versus Si-Dioden Bilder 5-7

Die SiC-SBDs zeichnen sich durch erheblich niedrigere Sperrverzögerungsströme und kürzere Sperrverzögerungszeiten aus, was die damit verbundenen Energieverluste stark reduziert. Jedoch weisen SiC-Schottky-Dioden im Vergleich zu Silizium-PN-Dioden einen höheren Durchlassspannungsabfall auf. Der Grund dafür ist, dass die SiC-Schottky-Dioden hohe Barrierehöhen benötigen, um die Leckströme zu reduzieren. Deshalb ist die Reduzierung der elektrischen Felder an der Schottky-Schnittstelle entscheidend für die Struktur von SiC-Schottky-Dioden.

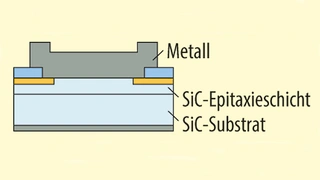

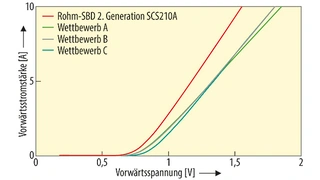

Rohm hat mit seiner zweiten Generation von SiC-SBDs technologische Fortschritte auf den Markt gebracht. Bild 6 zeigt den schematischen Querschnitt einer SiC-Schottky-Barrier-Diode. Rohm-Dioden zeichnen sich nach Unternehmensangaben durch die weltweit niedrigste Vorwärtsspannung aus (Bild 7). Gleichzeitig werden durch die präzisen Fertigungsprozesse die Leckströme der Dioden niedrig gehalten.

Das Angebot von Rohm bei der zweiten Generation der SiC-SBDs umfasst derzeit Produkte für 650 V von 5 bis 100 A sowie für 1200 und 1700 V mit Stromtragfähigkeiten bis 50 A.

SiC-Dioden der dritten Generation

Was war nun die Motivation für die Entwicklung der dritten SiC-Dioden-Generation?

Mittlerweile sind SiC-SBDs für Anwendungen wie Schaltnetzteile als die bessere Alternative zu Si-basierten schnellen Recovery-Dioden (Si-FRDs) in Leistungsfaktorkorrekturschaltungen (PFC-Schaltungen) bekannt.

Bei dieser Anwendung tritt im Anschaltmoment ein großer Stoßstrom auf, da der Zwischenkreis-Kondensator vor dem Einschalten nicht aufgeladen ist. Die zweite Generation der Rohm-SiC-SBDs verfügt über einen niedrigeren Wert der Stoßstromfähigkeit (IFSM) im Vergleich zu Si-basierten schnellen Recovery-Dioden. Deshalb wird empfohlen, Bypass-Dioden für Schaltnetzteil-Applikationen zu verwenden. Nachteil der Bypass-Dioden sind der erforderliche Platzbedarf sowie die hohen Kosten. Aus diesem Grund hat Rohm die dritte Generation von SiC-SBDs marktgerecht entwickelt (Bild 8). Erste Produkte sind bereits erhältlich.

Vorgabe bei der Entwicklung der dritten Generation war, die besonders niedrige Vorwärtsspannung, durch die sich die zweite Generation im Wettbewerb auszeichnet, beizubehalten.

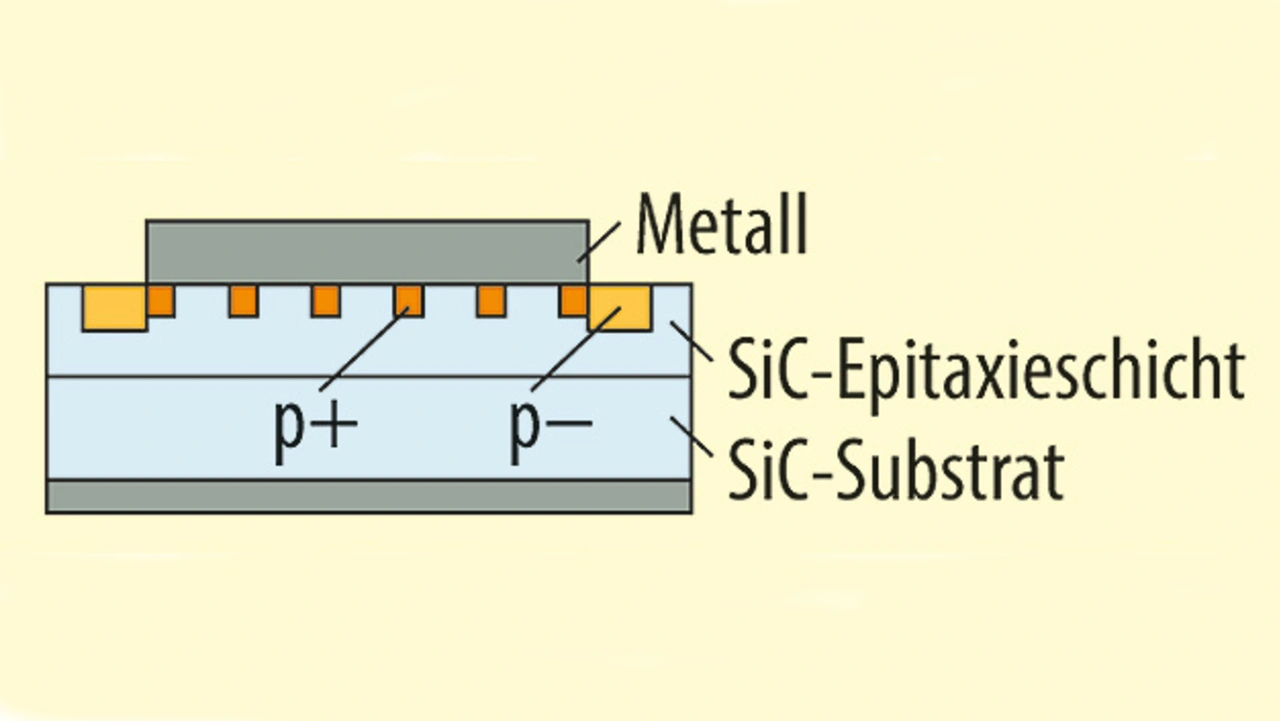

Mit der Entwicklung der Junction-Barrier-Schottky-Struktur, kurz JBS, hat Rohm alle Vorteile von SiC-Dioden in einem Bauteil vereint. Bei diesem Ansatz wurden unter der Schottky-Barriere in optimierten Abständen P+- und P--Senken eingebettet, um die Robustheit der Diode zu erhöhen.

Bei der PN-Struktur innerhalb der Diode und durch die Injektion von Minoritätsladungsträgern, nimmt der Widerstand der Epitaxie-Schicht mit der Temperatur ab. Im Gegenzug erhöht sich der Widerstand der Epitaxie-Schicht bei Erhöhung der Sperrschicht-Temperatur der SBD-Struktur (Bild 9).

SiC-MOS-Strukturen

Planarstruktur der zweiten Generation

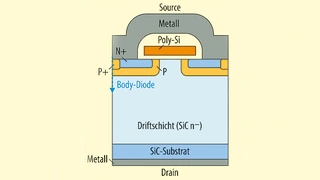

Eine der bekanntesten Strukturen in der Halbleiterindustrie ist die Planarstruktur. Diese Struktur eignet sich ebenfalls für SiC-MOS für Hochspannungsanwendungen. Auf dem Markt gibt es neben Rohm wenige Anbieter, die die Planarstruktur in ihren Produkten implementiert haben. Bekanntermaßen bildet sich bei den MOSFETs zwischen der P-Schicht und der N-Driftschicht intern eine parasitäre Diode, die als Body-Diode bezeichnet wird (Bild 10). Der On-Widerstand des Bauteils erhöht sich, wenn ein Strom durch die Body-Diode fließt. Deshalb ist ein stabiles Verhalten der Body-Diode entscheidend für die Zuverlässigkeit des SiC-MOSFET im Rahmen der Endanwendung. Leistungselektronik-Ingenieure erwarten beim Verhalten der Body-Diode, dass keine Degradierung auftritt, um die Zuverlässigkeit ihrer Systeme sicherzustellen.

SiC-MOS-Strukturen Bilder 10 - 14

Aber was beeinflusst die Degradierung der Body Diode?

Der Herstellungsprozess des Planar-MOSFETs hat einen großen Einfluss auf die Stabilität der Body-Diode. Fehler wie Versetzung im SiC-Substrat oder beim Wachstum der SiC-Epitaxieschichten können dazu führen, dass sich der On-Widerstand der Body-Diode sowie des MOSFET verschlechtert (sogenanntes Degradieren). Rohm hat es – durch die Expertise bei den verschiedenen Herstellungsprozessen (vom Substrat über das Epitaxiewachstum zum Bauteil) geschafft, die Degradierung der Body-Diode zu verhindern.

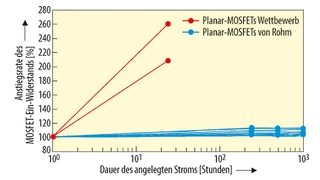

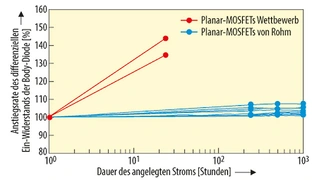

Bild 11 und Bild 12 zeigen Ergebnisse von Vergleichsmessungen zwischen Rohm-MOSFETs und Planar-SiC-MOSFETs anderer Anbieter. Hier wird zwischen zwei Planar-MOSFETs zweier Anbieter des Wettbewerbs und 22 Planar-MOSFETs von Rohm verglichen. Die Sperrspannung der evaluierten MOSFETs beträgt 1200 V. Der On-Widerstand beträgt typischerweise 0,09 Ω (entspricht 100 % in Bild 11); der Drain-Strom beträgt 8 A.

Nach 24 Stunden Dauerstrom wurde festgestellt, dass sich der On-Widerstand der Planar-MOSFETs aus dem Wettbewerb sowohl bei den MOSFETs als auch beim differenziellen Einschaltwiderstand der Body-Dioden drastisch erhöht. Im Gegenzug zeigen die Planar-SiC-MOSFETs von Rohm keine Degradierung über 1000 Stunden.

Trench-Struktur der dritten Generation

Die Trench-Struktur hat sich seit Jahrzehnten bei den Si-IGBTs bewährt. Diese Technologie erwies sich als vorteilhaft für viele Leistungselektronikanwendungen. Hierbei wird die Gate-Elektrode im Drift Layer eingebettet; deshalb nennt sich diese Technologie Trench-Gate-Technologie. Die Entwickler von Rohm haben die konventionelle Trench-Gate-Technologie für SiC-MOSFETs untersucht. Dabei stießen sie auf interessante Erkenntnisse.

Da die elektrische Feldstärke bei SiC höher ist als bei Si-IGBTs, würde die Verwendung der herkömmlichen Trench-Gate-Technologie zu folgendem Problem führen: Während des Sperrzustandes von SiC entsteht ein starkes elektrisches Feld in der Größenordnung von 2,66 MV/cm am Gate Trench. Durch eine übermäßige Belastung, die auf das Gate-Oxid ausgeübt wird, würden die Zuverlässigkeit und die Lebensdauer der Bauteile stark beeinträchtigt werden. Um diese starke elektrische Feldbelastung zu unterdrücken, wurde die Double-Trench-SiC-MOSFET-Struktur von Rohm entwickelt. Bei dieser Technologie sind die Source- und Gate-Elektroden im Drift Layer eingebettet, wobei die Source-Elektrode tiefer eingeschnitten ist als die Gate-Elektrode. Diese Konfiguration reduziert die effektive elektrische Feldbelastung auf das Gate-Oxid auf unter 1,66 MV/cm (Bild 13). Tiefere Source-Elektroden verhindern somit die Konzentration von elektrischen Feldern an den Tiefpunkten des Gate.

Weitere Vorteile der Double-Trench-Struktur sind, dass dabei der Durchlasswiderstand (Rdson) für die gleiche Chipgröße um 50 % reduziert wird, was zur wesentlichen Verringerung der Leitungsverluste beiträgt (Bild 14). Außerdem wird die Eingangskapazität um 35 % verringert. Dies bedeutet niedrigere Schaltverluste und insgesamt eine beträchtliche Reduzierung der totalen Energieverluste. Diese Struktur ist ein wichtiger Schritt auf dem Weg zu noch effizienteren Modulen mit höherer Leistungsdichte. Des Weiteren führt die reduzierte elektrische Feldbelastung zu einer höheren Zuverlässigkeit des Gate-Oxids.

Rohm startet die Massenproduktion der dritten SiC-MOS-Generation bei diskreten Bauteilen sowie bei Voll-SiC-Modulen mit seiner selbst entwickelten Double-Trench-Technologie, die die bestehende MOSFET-Produktfamilie erweitert und einen Beitrag zur Weiterentwicklung der hocheffizienten und zuverlässigen Leistungselektronik leistet.

- SiC und die unterschiedlichen Zellstrukturen

- SiC-Dioden versus Si-Dioden

- Sicherstellen der Qualität von SiC-Bauteilen