CoolSiC-MOSFETs

Schritt für Schritt SiC-Designs etablieren

Fortsetzung des Artikels von Teil 1

Das Schaltverhalten

Das Schaltverhalten wurde mit einem 45-mΩ-CoolSiC-MOSFET in einem TO-247-Gehäuse mit 4 Pins und Treiberspannungen von –5 V/15 V getestet. Das Bauteil zeigt ein sauberes Schaltverhalten mit einem geringfügigen Auftreten von Schwingungen beim Einschalten.

Jobangebote+ passend zum Thema

Zur Evaluierung des Schaltverhaltens auf Systemebene wurden ein DC/DC-Umrichter mit einem CoolSiC-Halbbrückenmodul (FF23MR12W1M1_B11) mit einem Durchlasswiderstand (RDSon) von 23 mΩ bei Raumtemperatur und der Treiber EiceDRIVER Compact mit 6-A-Ausgang (1EDI60H12AH) benutzt. Das Modul wurde innerhalb einer bidirektionalen Buck-Boost-Topologie angesteuert.

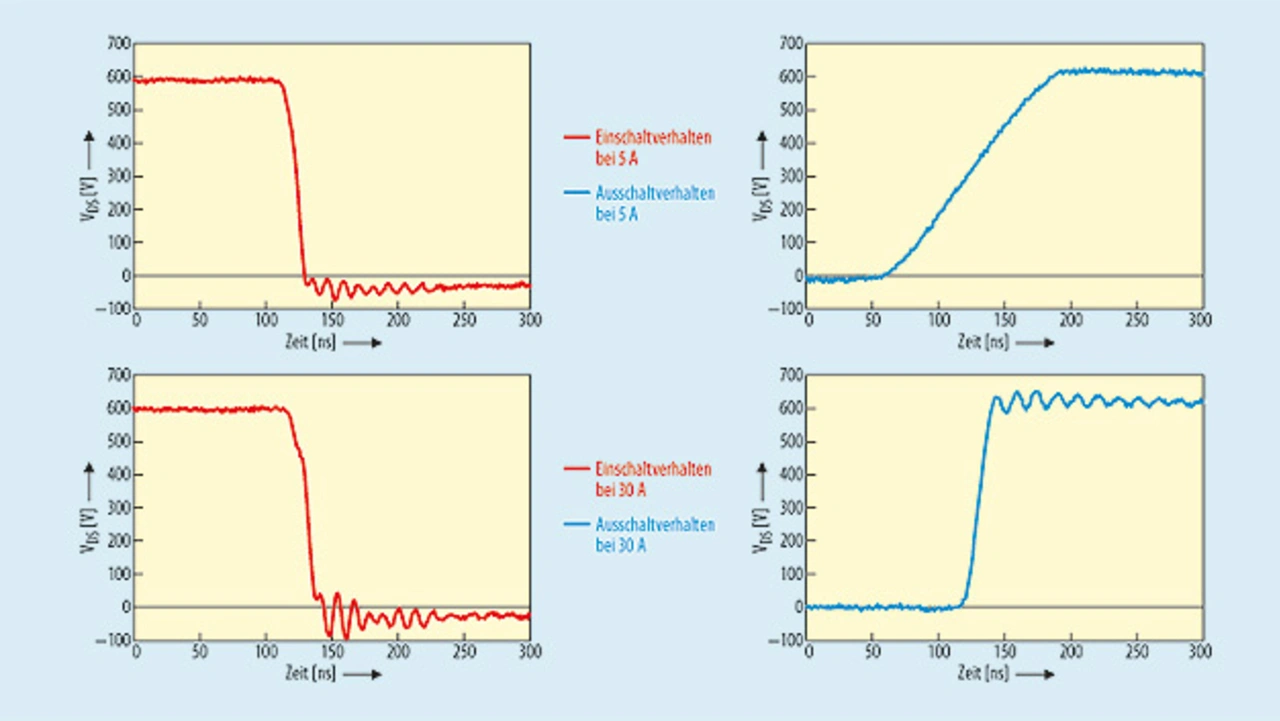

Doppelpulsmessungen innerhalb des Umrichters wurden durchgeführt, um dU/dt bei einem Gate-Widerstand von 1 Ω und unterschiedlichen Drain-Strömen zu messen. Der obere Teil von Bild 3 zeigt das Schaltverhalten bei 5 A. Sowohl das Einschalt- wie auch das Ausschaltverhalten weisen nur geringfügige Schwingungen auf. Beim Abschalten kommt dU/dt auf einen relativ geringen Wert von 5 kV/µs. Im Vergleich hierzu zeigt der untere Teil von Bild 3 das Schaltverhalten des CoolSiC-MOSFET-Moduls bei 30 A.

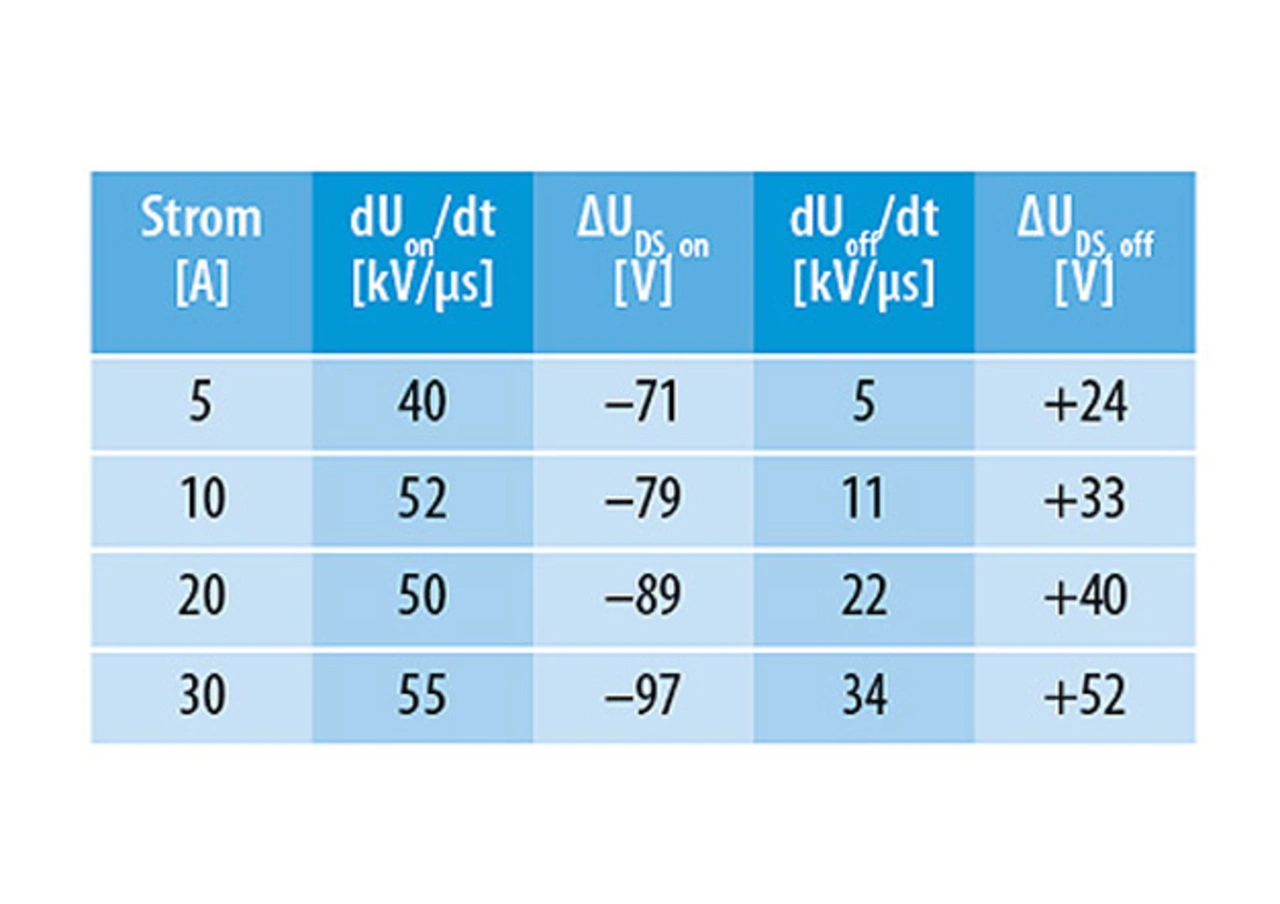

Das dU/dt beim Ausschalten ist mit einem Wert von 34 kV/µs viel höher als bei einem 5-A-Drain-Strom. Die starke Abhängigkeit des Schaltverhaltens vom Drain-Strom wird durch die hohe Ausgangskapazität des SiC-MOSFET verursacht. Hohe Verschiebungsströme am Ausgangskondensator des Bauteils beschleunigen das Ausschalten durch einen dynamischen Anstieg der Ausschaltspannung am Gate. Die Schwingungen sind im Vergleich zum vorher behandelten Fall mit niedrigeren Drain-Strömen etwas höher. Zur Evaluierung wurden weitere Messungen von dU/dt und der Spitzenspannung durchgeführt, die in Tabelle 2 dargestellt sind.

Kontrollierbarkeit des MOSFET

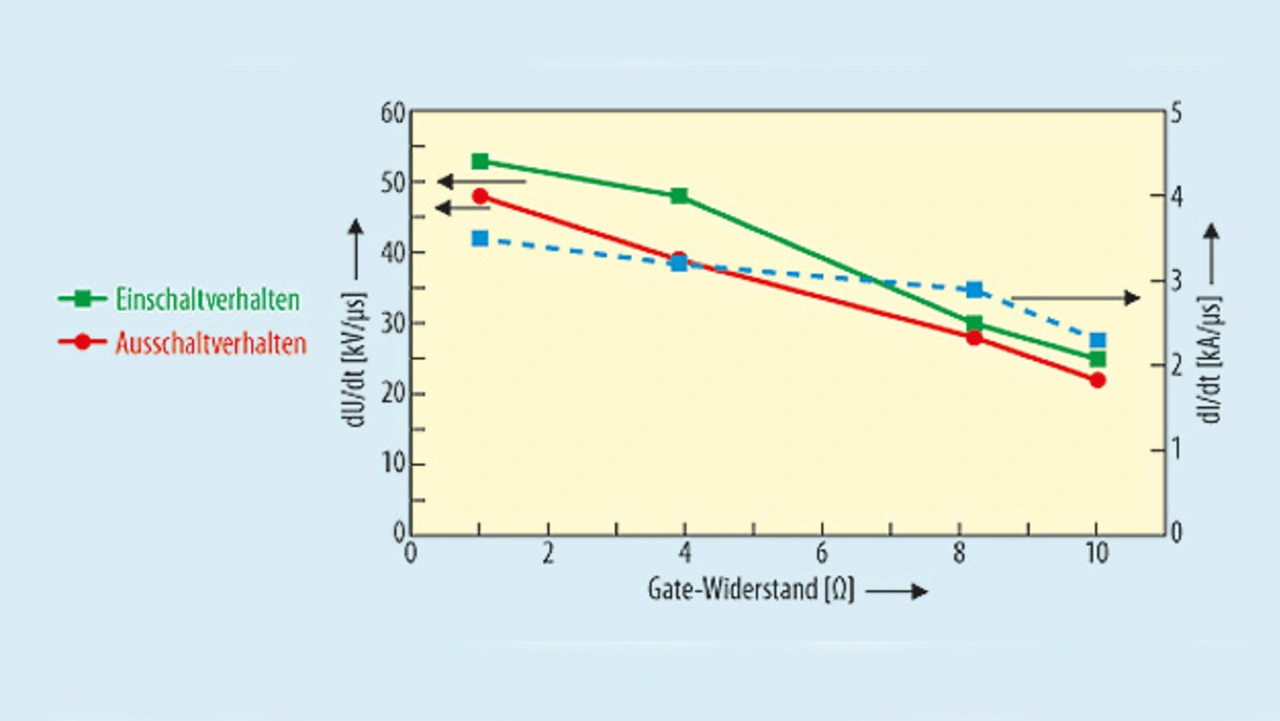

Bei den CoolSiC-MOSFETs lässt sich dU/dt und dI/dt mit Hilfe von externen Gate-Widerständen regeln. Die Messungen, die das belegen, wurden mit einem Halbbrückenmodul des Typs FF23mR12W1M1_B11 CoolSiC Easy1B durchgeführt. Die Ergebnisse werden in Bild 4 dargestellt.

Das dU/dt und dI/dt des untersuchten MOSFET lassen sich durch die Implementierung von höheren externen Gate-Widerständen verringern. Auf diese einfache Art kann das elektromagnetische Rauschen – falls erforderlich – verringert werden, um anwendungsspezifische Anforderungen zu erfüllen.

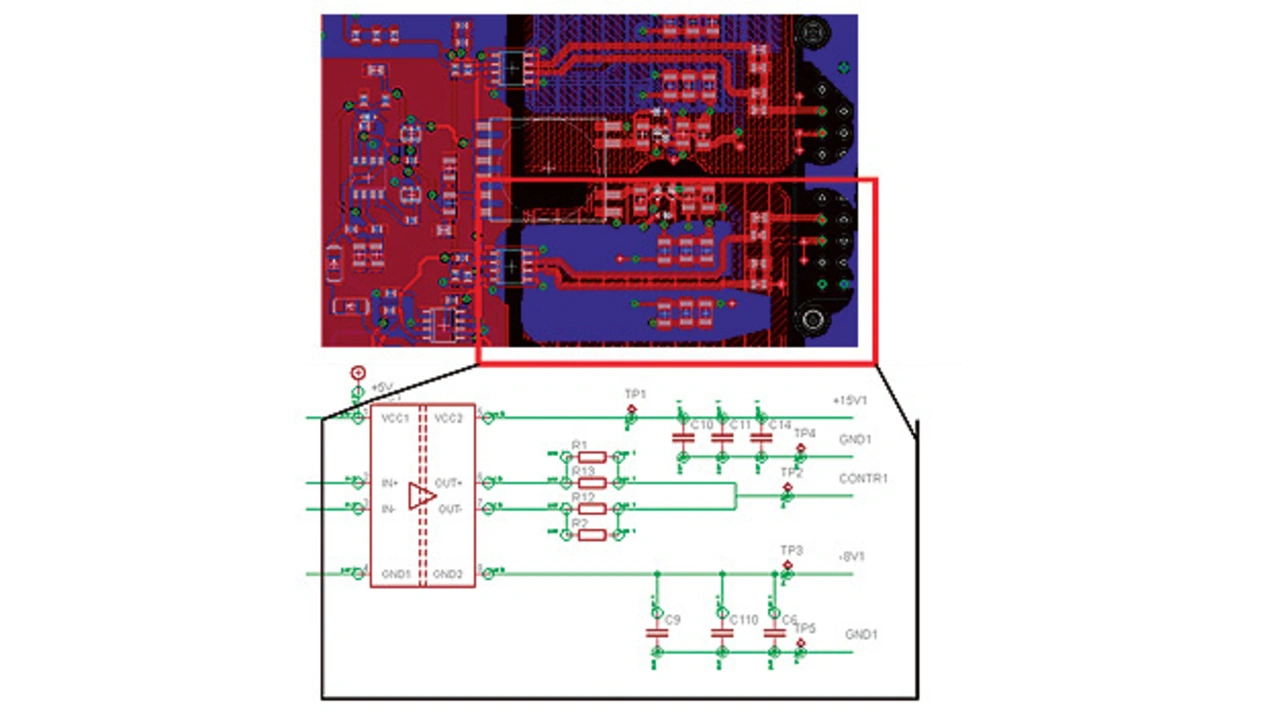

Ein klassisches Beispiel für die Anpassung an anwendungsspezifische Anforderungen ist die Beschränkung hinsichtlich dU/dt für Antriebe (z.B. 5 kV/µs). Durch die Wahl des richtigen externen Gate-Widerstands kann diese Randbedingung in Kombination mit dem CoolSiC-MOSFET erfüllt werden. Die einfache Möglichkeit zur Treiberrealisierung mit Hilfe des CoolSiC-MOSFET führt zu einfachen Treiberschaltungen. Bild 5 zeigt das Beispiel eines Treiberschaltkreises auf der Grundlage des EiceDRIVER Compact.

Beim Layout des Treibers wurde besonderes Augenmerk auf die geringe Induktivität der Verbindung zwischen Treiberausgang und den Gate- und Source-Pins des CoolSiC-MOSFET-Moduls gelegt. Deshalb wird eine Streifenleiterverbindung verwendet, die durch Kupferschicht¬ebenen für die ¬Source-Anschlüsse und breite Leitungen für die Gate-Anschlüsse ermöglicht wird. Das führt zu einer erheblichen Reduzierung des elektromagnetischen Rauschens insbesondere beim harten Schalten mit Rg = 1 Ω.

Um die volle Leistungsfähigkeit von CoolSiC-MOSFETs ausnutzen zu können, sollte auf ein Platinenlayout mit niedriger Induktivität geachtet werden. Der vorgestellte Treiberschaltkreis ist Teil eines Evaluierungssystems, das zur Charakterisierung der Leistung des CoolSiC-Moduls entwickelt wurde. Dieser wurde im Rahmen der Evaluierung bis 500 kHz betrieben.

Die Autoren

| Dr. Maximilian Slawinski |

|---|

| hat an der RWTH Aachen Elektrotechnik und Wirtschaftsingenieurwesen studiert und anschließend im Bereich der Halbleiterphysik promoviert. Seit 2015 ist er für die Applikationen Solar und USV bei Infineon in Warstein zuständig. Dort beschäftigt er sich unter anderem mit dem Nutzen des CoolSiC-MOSFET für Solar- und USV-Systeme. |

| Marc Buschkühle |

|---|

| ist seit 2006 bei Infineon beschäftigt, wo er seit 2015 im Produktsegment Low und Medium Power die Markteinführung der CoolSiC-Technologie betreut. Zuvor arbeitete er im Technischen Marketing für den Bereich Low-Power-IGBT-Module. Buschkühle hat Elektrotechnik mit Fokus auf elektrische Energietechnik an der Fachhochschule Südwestfalen studiert |

- Schritt für Schritt SiC-Designs etablieren

- Das Schaltverhalten