Smarte Gate-Treiber mit UL-Zertifikat

Leistungswandlung de luxe

Durch den Umstieg von Silizium- auf SiC-basierte Leistungsschalter steigen auch die Herausforderungen im Schaltungsdesign. Der Einsatz von integrierten Smart-Gate-Treibern mit UL/cUL-Zertifizierung kann die Entwicklungszeit maßgeblich verkürzen.

Setzen Entwickler von Leistungselektronik verbesserte Leistungsschalter und Mikrocontroller ein, können sie den Wirkungsgrad mit jeder neuen Produktgeneration um bis zu einem weiteren Prozentpunkt erhöhen. Die Anwendungen, die von diesen Fortschritten profitieren, sind dabei vielfältig: von Elektrofahrzeugen (EV) mit ihren Motorwechselrichtern und Batterieladegeräten bis hin zu unterbrechungsfreien Stromversorgungen (USV), Servoantrieben und Solarwechselrichtern. Um diese Verbesserungen zu erreichen, ist es jedoch häufig nötig, die Schaltgeschwindigkeiten zu erhöhen und von siliziumbasierten IGBTs oder MOSFETs zu Siliziumkarbid-Bauelementen (SiC) zu wechseln.

Höhere Werte für das du/dt und di/dt bringen stets auch neue Herausforderungen im Schaltungsdesign mit sich, für die jeweils optimale Lösungen gefunden werden müssen. Diese reichen von den Auswirkungen unerwünschten Einschaltens (Parasitic Turn-on), das durch die nichtlineare Miller-Kapazität zwischen Kollektor/Drain und Gate verursacht wird, bis hin zur Reaktion auf Kurzschlüsse oder Überlastungen der Schalter. Geeignete Lösungen dafür zu finden, braucht Zeit. Vorteilhafter ist es daher oft, einen integrierten Smart-Gate-Treiber zu wählen, der bereits über eine UL/cUL-Zertifizierung verfügt.

Jobangebote+ passend zum Thema

Miller-Kapazität handhaben

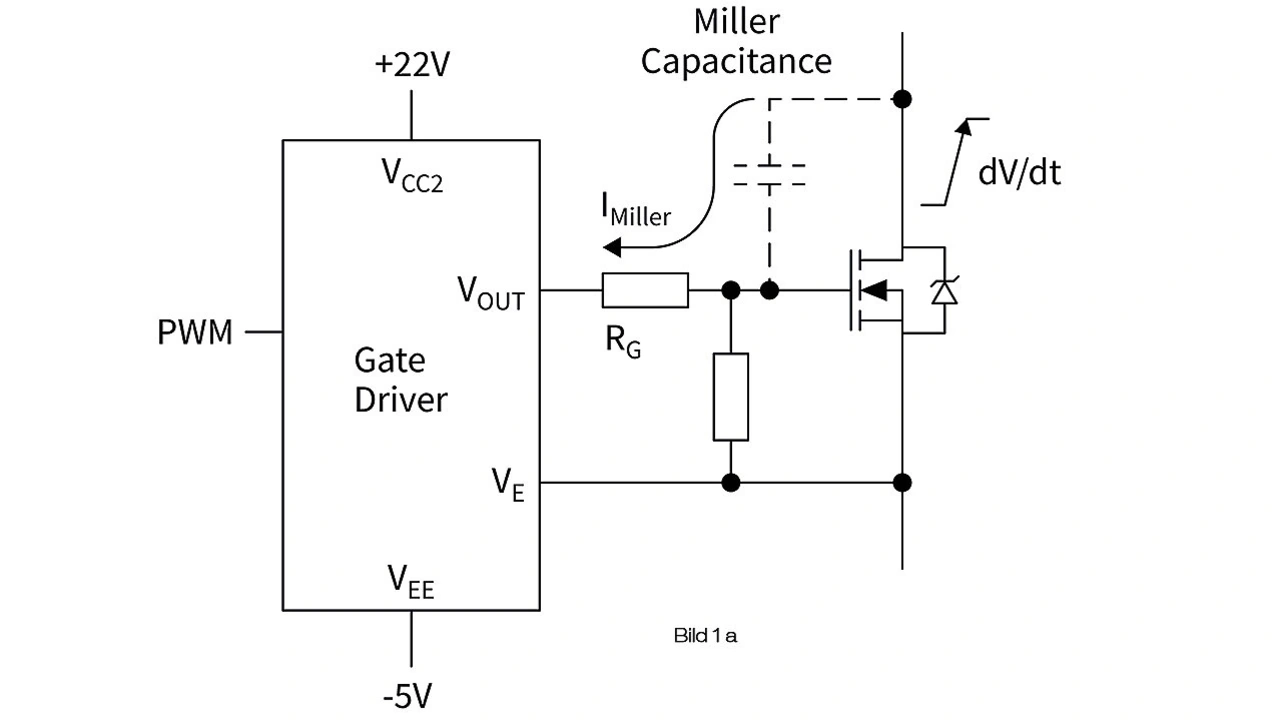

Wird beispielsweise in einer Halbbrücke der untere Transistor ausgeschaltet und der obere eingeschaltet, injiziert die Miller-Kapazität des unteren Schalters zwischen dem Kollektor/Drain und dem Gate einen Strom in dessen Gate. Jeder Serienwiderstand zwischen dem Gate und der Treiberschaltung führt zu einer Spannung, die im schlimmsten Fall dazu führen kann, dass der Schalter wieder einschaltet. Obwohl IGBTs und MOSFETs selbstsperrend sind, also bei einer Gate-Source- bzw. Gate-Emitter-Spannung von 0 V nominell ausgeschaltet sind, verwenden Gate-Treiber-Schaltungen häufig eine negative Spannung, um sicher auszuschalten (Bild 1a). Diese reicht von −5 V für MOSFETs bis zu −7 V für IGBTs, um dem durch den Gate-Widerstand verursachten Spannungsanstieg entgegenzuwirken.

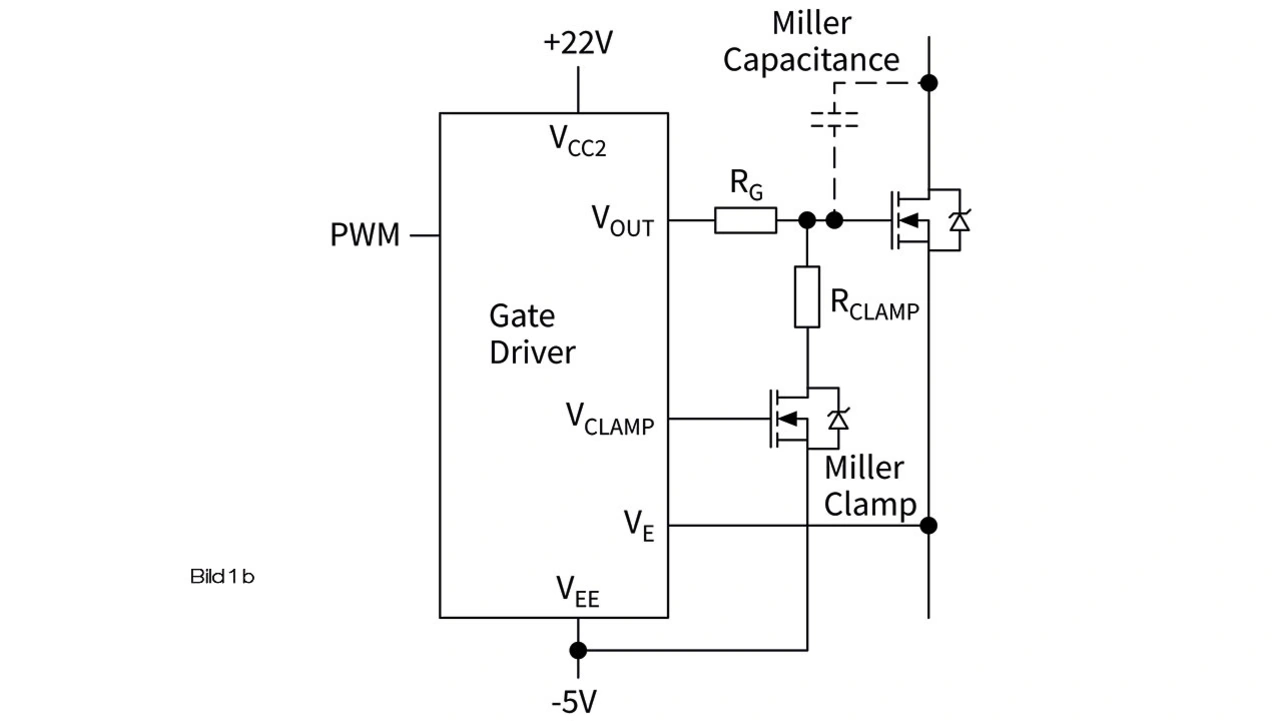

Diese Lösung ist praktikabel, erfordert jedoch eine zusätzliche Versorgungsspannung, die im übrigen Design möglicherweise nicht benötigt wird. Um dies zu vermeiden, eignet sich eine Miller-Clamp-Schaltung. Durch die Einführung eines zusätzlichen MOSFETs zwischen Gate und Emitter bzw. Source wird die Gate-Spannung des Leistungsschalters geklemmt, nachdem das Ansteuersignal unter einen bestimmten Wert gesunken ist (Bild 1b). Nachdem sich die Kollektor- bzw. Drain-Spannung auf ihrem Aus-Zustand stabilisiert hat, kann dieser Klemmschalter wieder deaktiviert werden. Dieser Zeitpunkt ist nicht besonders kritisch, muss aber vor dem nächsten Einschalten des Leistungstransistors abgeschlossen sein.

Schutz vor Überlastbedingungen

Bei einem Kurzschluss oder wenn die angelegte Gate-Treiber-Spannung nicht hoch genug ist, um den Leistungsschalter vollständig in den Sättigungsbereich zu bringen, kann der Transistor zerstört werden. Über eine Entsättigungserkennung (DESAT), die die Kollektor- bzw. Drain-Spannung während des eingeschalteten Zustands überwacht, kann die Treiberschaltung den Schalter wieder ausschalten, sollte eine vordefinierte Schwellenspannung überschritten werden. Da die Kurzschlussfestigkeit bestenfalls bei einigen Millisekunden liegt, muss dieser Mechanismus sehr schnell reagieren. Bei Bauelementen, die mit vielen Kilohertz und in einer elektrisch störbehafteten Umgebung arbeiten, ist dies jedoch eine große Herausforderung.

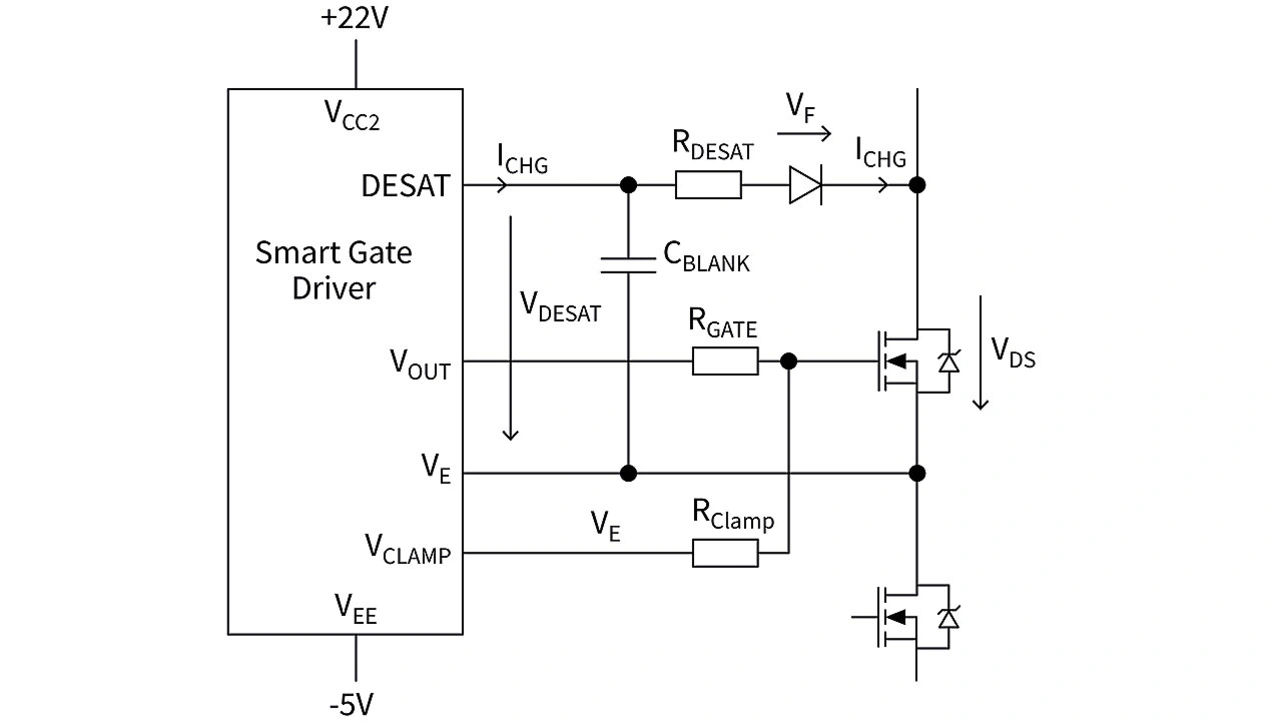

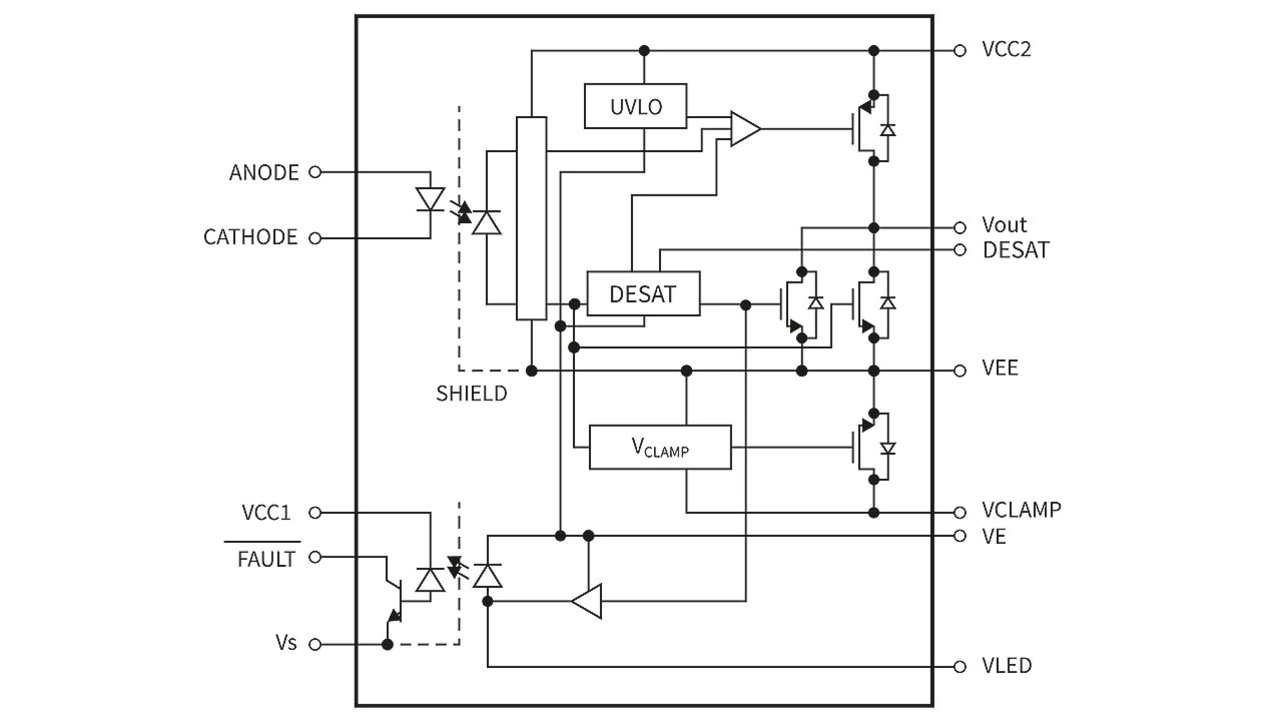

Gate-Treiber mit integrierter DESAT-Funktion benötigen nur eine minimale Anzahl zusätzlicher Bauelemente, um vor solchen Überlastbedingungen zu schützen. Zusammen mit einem RC-Netzwerk wird eine Diode auf der einen Seite mit dem Kollektor bzw. Drain und auf der anderen Seite mit dem DESAT-Pin des Gate-Treibers verbunden (Bild 2). Ist das Leistungsbauelement gesättigt, ist die Diode in Durchlassrichtung vorgespannt und zieht den DESAT-Pin auf Low. Durch Vergleich dieser Spannung mit der Einstellung UDESAT,max des Gate-Treibers und dem Treiberzustand kann der Gate-Treiber feststellen, ob ein Fehlerzustand aufgetreten ist.

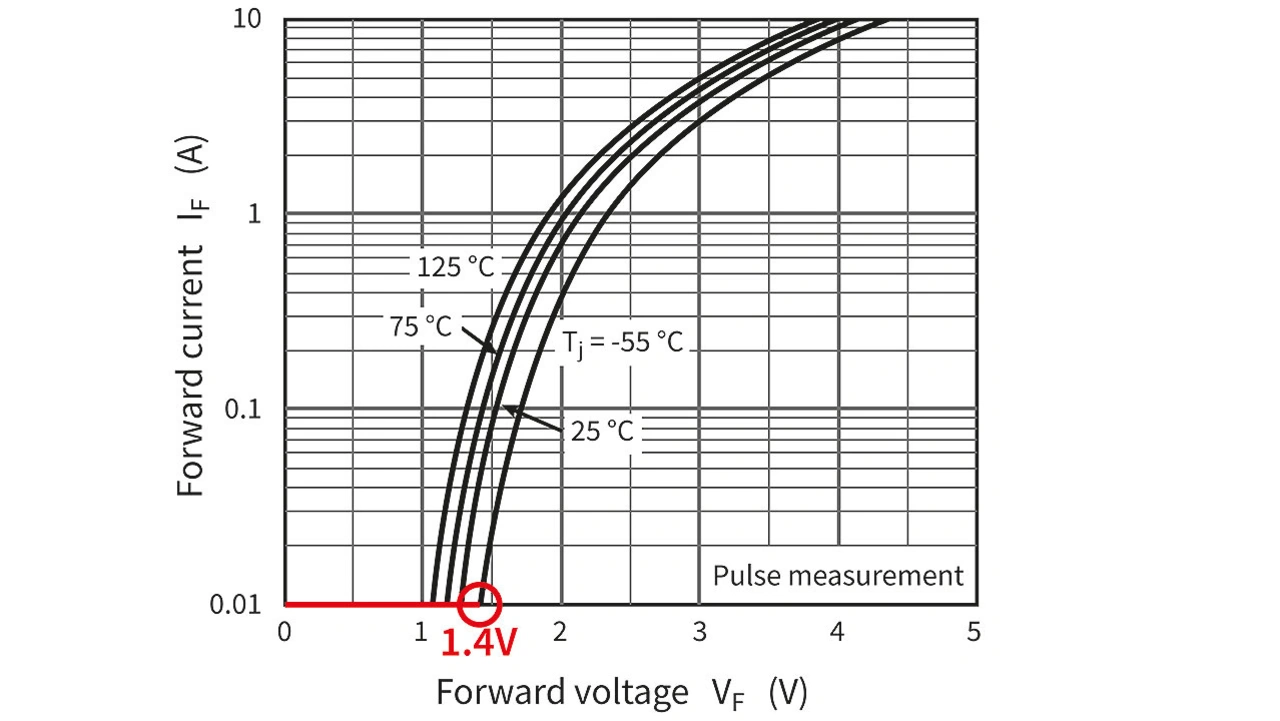

Die Diode muss für die gesamte DC-Busspannung plus einer gewissen Marge ausgelegt sein, die in einigen Anwendungen insgesamt leicht 1000 V oder mehr betragen kann, obwohl der Durchlassstrom niedrig sein kann. Zudem sollte das Bauelement schnell reagieren und eine sehr niedrige Kapazität sowie Rückwärtserholungsladung aufweisen. Da diese Eigenschaften in einer einzelnen Diode nur schwer zu finden sind, werden oft mehrere Bauelemente in Reihe geschaltet. Damit lässt sich die Nennspannung erhöhen und gleichzeitig die Kapazität verringern, aber gleichzeitig erhöhen sich der Spannungsabfall in Durchlassrichtung und damit der DESAT-Schwellenwert. SiC-Dioden sind ebenfalls eine Option, bei der man aber bedenken sollte, dass sie eine höhere Durchlassspannung als herkömmliche Siliziumdioden aufweisen.

Eine Zener-Diode schützt den DESAT-Pin, indem sie die Spannung auf ein für den Gate-Treiber sicheres Niveau absenkt, während eine Schottky-Diode das Signal unter das Massepotenzial absenken kann.

DESAT-Schaltung dimensionieren

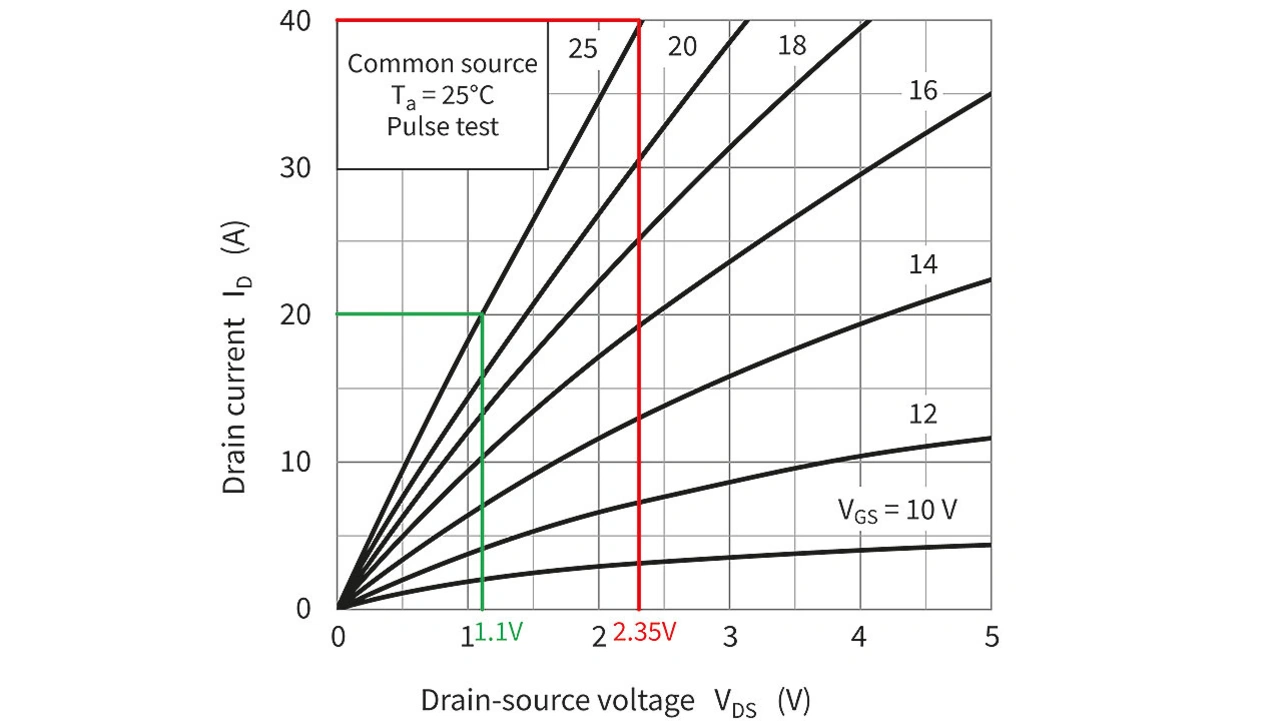

Um die DESAT-Schaltung zu dimensionieren, muss aus der Übertragungskennlinie des MOSFETs die Drain-Source Spannung UDS, bei der abgeschaltet werden soll, ermittelt werden. Damit lassen sich der Widerstand und der Kondensator für die DESAT-Schaltung berechnen.

Bild 3a zeigt die Ausgangkennlinie für den SiC-MOSFET TW070J120B von Toshiba. Bei einer Gate-Source-Spannung UGS von 25 V und dem normalen Drain-Strom ID von 20 A beträgt die Drain-Source-Spannung UDS 1,1 V (grün), beim maximalen ID von 40 A liegt der Wert bei 2,35 V (rot). Der nächste Schritt besteht darin, die Vorwärtsspannung UF für die ausgewählten Dioden zu ermitteln. Für zwei Fast-Recovery-Dioden des Typs CRF03A von Toshiba ergeben sich 2 × 1,4 V (Bild 3b).

Der letzte Schritt besteht darin, UDESAT,max und ICHG aus dem Datenblatt des gewählten Smart-Gate-Treibers zu bestimmen. Für den TLP5214A von Toshiba sind dies 6,5 V für UDESAT,max bzw. 250 µA für ICHG. Daraus lässt sich RDESAT folgendermaßen berechnen:

Nun ist nur noch der Kondensator CBLANK zu berechnen. Anhand der Kurzschlussfestigkeit des ausgewählten SiC-MOSFETs, die zwischen 2 und 4 µs liegt, wird dieser wie folgt ermittelt:

Damit ergibt sich CBLANK zu 74 pF für 2 µs oder zu 146 pF für 4 µs Kurzschlussfestigkeit.

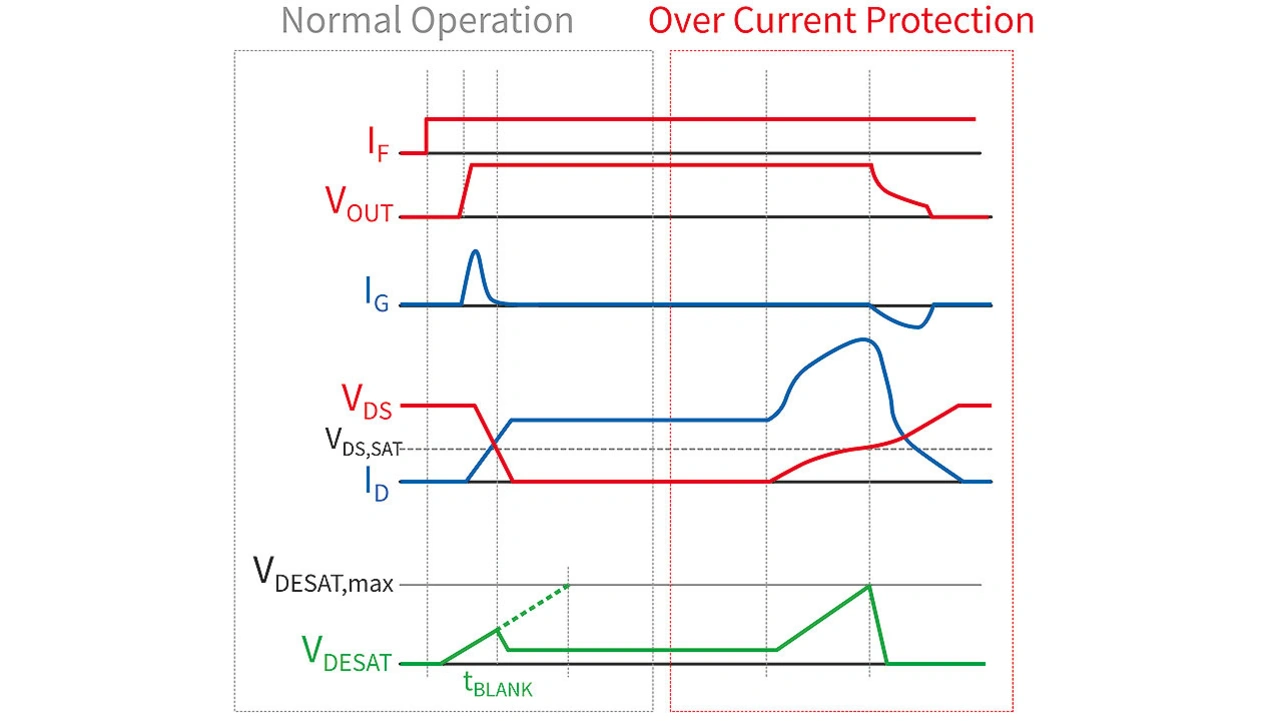

Bild 4 zeigt die qualitativen Verläufe von Spannung und Strom für den normalen Betrieb sowie den Kurzschluss- und/oder Überstromfall.

Smarte Gate-Treiber mit Sicherheitsfunktionen

Smart-Gate-Treiber wie der TLP5214A erzeugen über einen Fehlerausgangspin ein isoliertes Signal, das den Steuerschaltkreis auf das Problem hinweist, während das sanfte Ausschalten im Fehlerfall (Soft Shutdown) automatisch aktiviert wird (Bild 5).

Der Controller kann dann die beste Vorgehensweise festlegen. So kann er den Leistungsschalter beispielsweise nach einer programmierten Verzögerung wieder einschalten, um sicherzustellen, dass die durchschnittliche Verlustleistung nicht zu hoch ist. Sollten die Timings für DESAT-Blanking und Soft-Shutdown für die Anwendung zu lang sein, etwa weil die Spitzenlast und das Rauschen geringer sind, können Entwickler den TLP5214 in Betracht ziehen, der im Wesentlichen die gleichen Eigenschaften bietet, aber kürzere Timings für diese beiden Parameter ermöglicht.

Beide Bausteine liefern maximale Ausgangsströme von ±4 A und haben einen Rail-to-Rail-Ausgangshub. Für Anwendungen mit geringeren Anforderungen an den Gate-Treiber-Spitzenstrom oder für den Fall, dass Abwärtskompatibilität zu früheren Gate-Treibern erforderlich ist, steht der TLP5212 zur Verfügung, der einen maximalen Ausgangsstrom von ±2,5 A und keinen Rail-to-Rail-Hub bietet.

Beide Chips werden im SO-16L-Gehäuse mit einer Kriech- und Luftstrecke von 8 mm ausgeliefert. Mit einer minimalen Isolationsspannung von 5000 V (eff.) eignen sich diese Smart-Gate-Treiber für Systemspannungen von 600 V (AC) und erfüllen die Sicherheitsstandards UL 1577 und EN 60747. Für IGBTs unterstützen sie Schaltfrequenzen von bis zu 50 kHz, bei SiC-MOSFETs bis zu 650 kHz. Die Verzögerung liegt bei ±150 ns für den TLP5212 bzw. ±80 ns für den TPL5214 und TLP5214A. Um höhere Gate-Ströme zu unterstützen, ist der TLP5231 ein intelligenter Gate-Pre-Driver. Mit diesem können Entwickler ihre Gate-Treiber-MOSFETs so spezifizieren, dass sie den Anforderungen der Anwendung entsprechen.

Leistungselektronik vereinfachen

Zwar lassen sich die Fehlererkennung und die Auswirkungen der Miller-Kapazität in Leistungselektronikdesigns auch mit diskreten Bauelementen implementieren. Ein solcher Ansatz erfordert jedoch mehr Platz auf der Leiterplatte und viele Komponenten sowie Zeit, um das Design zu testen und zu optimieren. Außerdem ist eine Sicherheitszertifizierung für das Design erforderlich.

Intelligente Gate-Treiber enthalten alle notwendigen Schaltungen, die für die Fehlerbehandlung und -erkennung bei Entsättigung erforderlich sind, und vermeiden dank der Miller-Klemmfunktion die Notwendigkeit einer negativen Versorgung. Die hier vorgestellten sicherheitszertifizierten Gate-Treiber unterstützen eine Vielzahl von Leistungsanforderungen für herkömmliche Designs mit IGBTs und Silizium-MOSFETs als auch solche, die auf Hochgeschwindigkeitsschaltungen mit SiC-MOSFETs umgestellt werden.

Der Autor

Dr. Matthias Ortmann

ist Chief Engineer bei Toshiba Electronics Europe.