Packaging

Leistungselektronik in Leiterplatten einbetten

Fortsetzung des Artikels von Teil 1

Einbetten von Leistungshalbleitern

Gehäuse für Leistungshalbleiter, hergestellt mit den laminatbasierten Chip-Einbetttechniken, bieten eine Vielzahl von Vorteilen im Vergleich zu konventionellen Gehäusen. Neben der Möglichkeit von 3D-Aufbauten, die auch Multi-Chip/Multi-Komponenten-Aufbauten ermöglichen, können eine niedrige Induktivität der elektrischen Verbindungen realisiert und Abschirmlagen integriert werden.

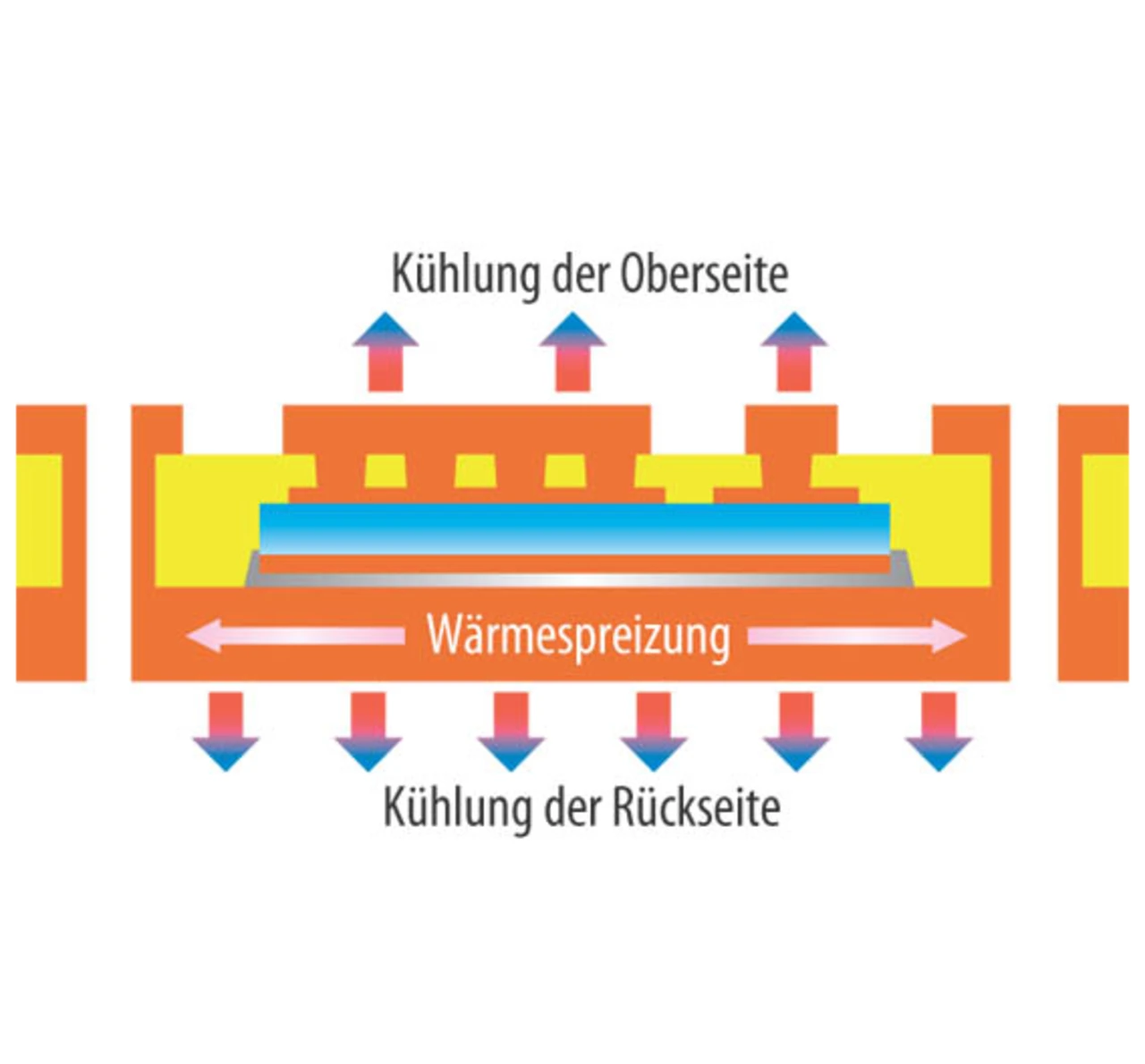

Außerdem ist ein sehr guter Wärmetransfer zur Gehäusevorder- und Rückseite möglich (Bild 3). Die Ergebnisse der Entwicklungen und die Tests der in Einbetttechnik aufgebauten Prototypen bestätigen diesen Gehäusen eine außerordentlich hohe Zuverlässigkeit.

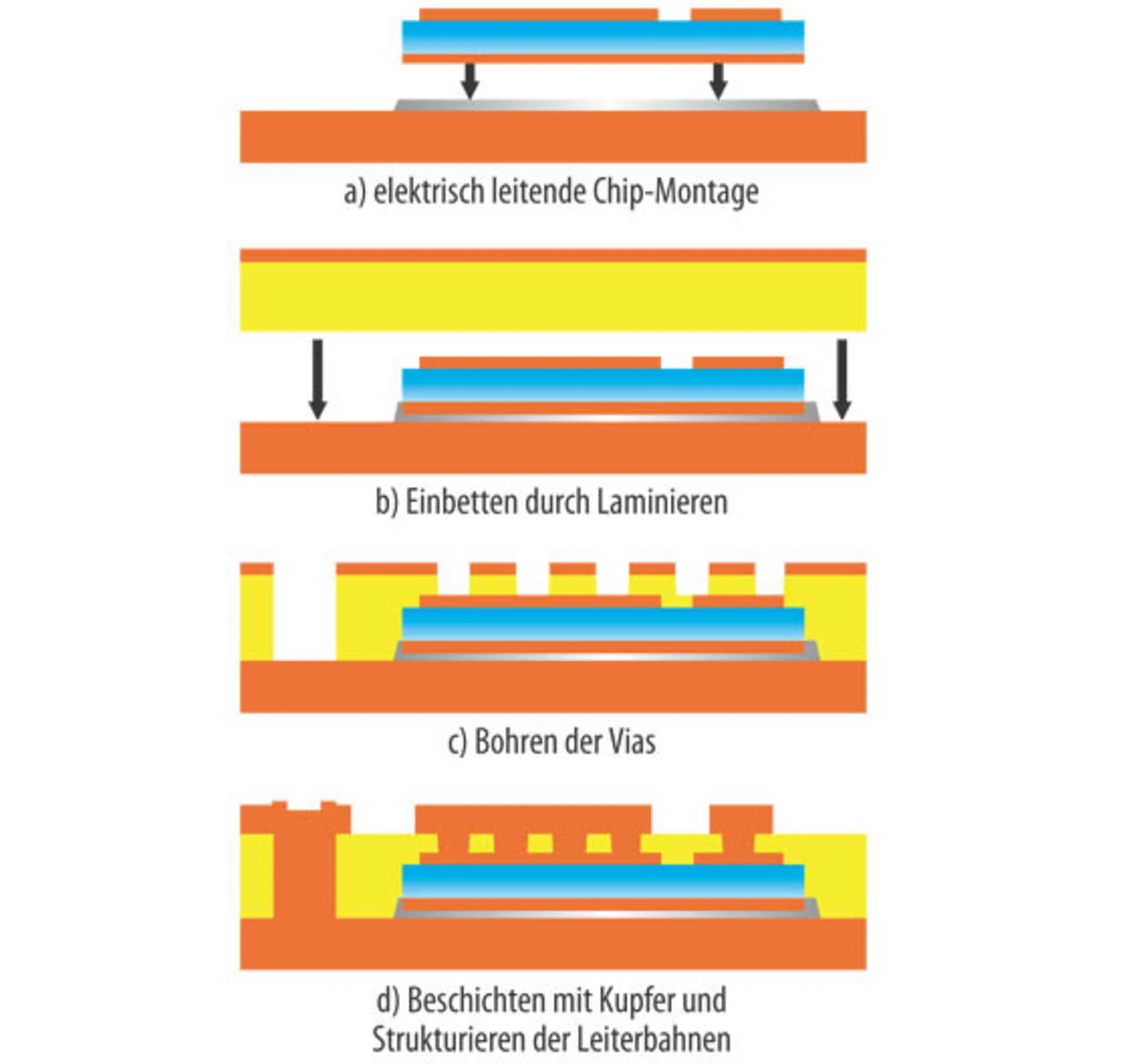

Die Prozessschritte für die Einbettung von Leitungshalbleitern sind in Bild 4 dargestellt. Leistungshalbleiter sind aufgrund des Widerstandes des Siliziums, welcher nur einen Fluss von hohen Strömen vertikal durch das Silizium erlaubt, vertikale Bauelemente. Daher haben sie sowohl auf der Vorderseite als auch auf der Rückseite Kontakte.

Jobangebote+ passend zum Thema

Die Kontakte auf der Vorderseite können unterschiedliche Metallisierungen aufweisen. Am weitesten verbreitet ist Aluminium, welches der Standard für eine Kontaktierung durch Drahtbonden ist. Diese Al-Metallisierung eignet sich allerdings nicht für die Einbetttechnik, da sie nicht mit den nachfolgenden, auf Kupfer basierenden Leiterplatten-Prozessschritten zur Ankontaktierung kompatibel ist. Daher ist hier eine zusätzliche Metallisierungsschicht auf den Anschlussflächen erforderlich.

Eine Silber- oder Nickel/Palladiummetallisierung haben hauptsächlich Chips, die zur Kontaktierung großflächig gelötet werden. Diese Metallisierung wurde bereits untersucht und eignet sich generell für die Einbetttechnik. Mittlerweile weisen Leistungshalbleiter zunehmend auch eine Kupfermetallisierung auf den Pads auf, die direkt vom Halbleiterhersteller erzeugt wird. Diese Metallisierung wird für die Kontaktierung durch Kupferdrahtbonden benötigt und eignet sich am besten für die Einbetttechnik.

Wie bereits erwähnt, benötigen Bauteile mit Aluminiummetallisierung eine zusätzliche Metallschicht für die Ankontaktierung. Idealerweise wird Kupfer für diese zusätzliche Metallisierungsschicht verwendet. Aber auch kostengünstige, stromlos abgeschiedene Nickel/Palladium-Schichten sind möglich. Ihre Eignung für den Einbettprozess wird noch untersucht.

Die typische Rückseitenmetallisierung von Leistungshalbleitern ist Silber. Auch Kupfer ist bereits teilweise verfügbar. Beide Metallisierungen sind vollkommen geeignet für die Chipmontage in „Face up“-Technik. Als Substrat wird typischerweise eine Kupferfolie oder ein dickeres Kupfersubstrat verwendet. Um die bestmögliche elektrische und thermische Kontaktierung des Leistungshalbleiters zu gewährleisten, wurden verschiedene Kontaktmaterialien untersucht. Mit elektrisch leitfähigem Klebstoff, der durch Schablonendruck oder Dispensen aufgebracht werden kann, lassen sich gleichmäßige und blasenfreie Kleberschichten aufbringen. Allerdings haben elektrisch leitende Klebstoffe eine niedrigere elektrische und thermische Leitfähigkeit als Lot- oder Sinter-Verbindungen.

Das Löten des Chips ermöglicht eine Verbindung mit hoher elektrischer und thermischer Leitfähigkeit. Allerdings ist beim Lötprozess die maximal mögliche Bauteilgröße limitiert, da es mit größer werdendem Chip schwieriger wird, nach dem Umschmelzen des Lotes eine blasenfreie Lotschicht herzustellen.

Als eine neue Methode bietet sich ein druckloser Sinterprozess bei niedrigen Temperaturen an. Diese Technik wird gerade weiterentwickelt und zeigt bereits vielversprechende Ergebnisse.

Nach der Montage des Chips findet die eigentliche Einbettung in das Laminatmaterial statt (Bild 4b). Dabei wird in Abhängigkeit von der Dicke des Chips geeignetes Laminatmaterial (RCC oder Prepreg) aufgelegt und anschließend in einer Mehrlagen-Vakuumlaminierpresse verpresst. Der Vorteil des RCC-Materials ist, dass Kupferfolie und vorvernetztes Epo-xidharz als eine Einheit zur Verfügung stehen und die Folien keine Vorbereitung durch Tiefenfräsen o.ä. erfordern.

Dies macht die Handhabung solcher Folien sehr einfach. Allerdings ist hier, bedingt durch den Herstellungsprozess des RCC, die maximale Schichtdicke des Harzes bei etwa 120 µm begrenzt. Dadurch können auch nur dünne Chips bis maximal 60 µm oder 80 µm Dicke mit RCC eingebettet werden.

Wenn aufgrund der elektrischen Eigenschaften des Halbleiters kein Dünnen des Siliziums in diesen Dickenbereich möglich ist, muss für das Einbetten Prepreg verwendet werden. Dazu werden entsprechend der Bauteildicke Prepreg-Schichten vorbereitet, um Kavitäten zur Bauteilaufnahme einzuarbeiten. Diese Kavitäten können durch Laserschneiden, Fräsen oder Stanzen hergestellt werden. Als oberste Lage werden ein unbearbeitetes Prepreg sowie eine Kupferfolie aufgelegt. Während des Laminationsprozesses schmilzt das vorvernetzte Harz auf und umfließt das einzubettende Bauteil vollständig und blasenfrei.

Nach der Lamination erfolgt die Herstellung von Mikrovias zu den Kontaktflächen auf der Vorderseite des jetzt „versteckten“ Bauteils durch Laserbohren (Bild 4c). Typischerweise wird eine hohe Viadichte erzeugt, um einen möglichst geringen elektrischen Widerstand zu realisieren. Um eine möglichst kleine Gehäusegröße zu erreichen, werden typischerweise die Kupferflächen direkt über dem Chip für die Gehäusekontakte verwendet.

Daher ist es notwendig, eine bestmögliche Füllung der Mikro-vias mit Kupfer im nachfolgenden Galvanikprozess zu erreichen. Dadurch wird eine möglichst geringe Fehlerquelle bei der Montage des fertigen Gehäuses gewährleistet. Der letzte Schritt ist die Strukturierung der äußeren Kupferschicht, um die benötigten Leiterbahnen und Anschlussflächen des Gehäuses herzustellen (Bild 4d).

- Leistungselektronik in Leiterplatten einbetten

- Einbetten von Leistungshalbleitern

- Leistungshalbleiter-Gehäuse

- Literatur & Autor