Verifikation effizient automatisieren

ESD-Schutz für 2,5D-/3D-ICs

Fortsetzung des Artikels von Teil 1

Gibt es eine eigene Methode zur automatisierten ESD-Verifizierung in 2,5D- und 3D-ICs?

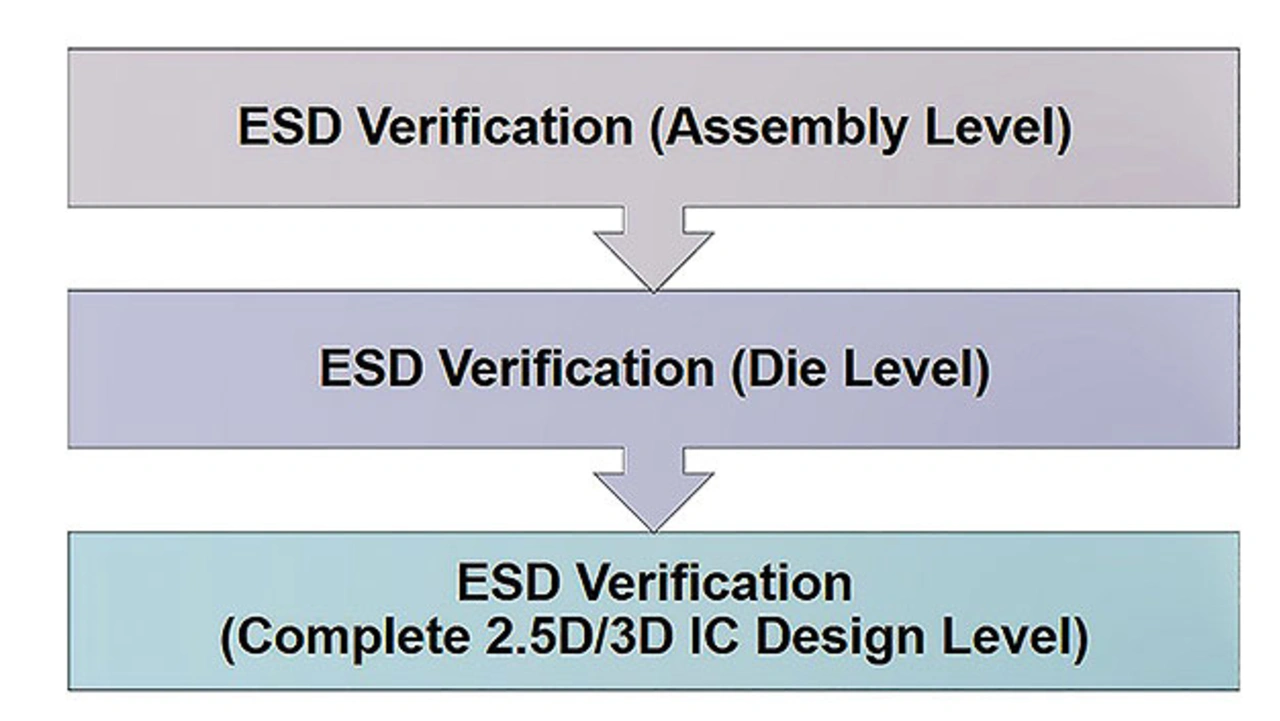

! Medhat: Zur Verifizierung der ESD-Festigkeit von 2,5D- und 3D-ICs auf Baugruppenebene, Die-Ebene und für die komplette 2,5D-/3D-IC-Entwicklung [5] wurde eine systematische Methodik entwickelt (Bild 3). Diese Methodik verlangt folgende Elemente: ESD-Beschränkungen, Baugruppen-Layout, Die-Layouts, Rule Decks für parasitäre Widerstände sowie Rule Decks zum Prüfen des Layouts gegen den Schaltplan (LVS, Layout Versus Schematic). Bei Siemens wurde zum Beispiel diese Methodik unter Verwendung der Zuverlässigkeitsplattform Calibre PERC [6] implementiert. In der ersten Stufe werden die betreffenden ESD-Daten aus dem Baugruppenlayout extrahiert, die zur Erfassung der Auswirkungen der Interposer/Schnittstellen erforderlich sind. Diese Stufe umfasst die folgenden Schritte:

- Erzeugung der Systembaugruppen-Netzliste.

- Identifikation der gegenseitigen Verbindungen zwischen den Dies sowie zwischen Dies und externen Pads.

- Berechnung des parasitären Punkt-zu-Punkt-Widerstands (P2P) und der Stromdichte (Current Density, CD) für die Geometrien aller internen und externen E/As.

- Speicherung der P2P- und CD-Werte.

In der zweiten Stufe werden die betreffenden ESD-Daten aus den Die-Layouts extrahiert. Dieser Vorgang muss für jedes Die wiederholt werden, weil die Dies für die Fertigung mit unterschiedlichen Prozesstechniken und unterschiedlichen Foundries entwickelt sein können. Zu dieser Stufe gehören folgende Schritte:

- Extraktion der Layout-Netzliste.

- Identifikation der Verbindungen von ESD-Schaltungen zu den Die-Anschlüssen.

- Berechnung des parasitären P2P-Widerstands und der Stromdichte für die Geometrien aller identifizierten Verbindungen von ESD-Schaltungen zu den E/As.

- Speicherung der P2P- und CD-Werte.

Jobangebote+ passend zum Thema

Während der dritten Stufe wird die ESD-Verifizierung auf der kompletten 2,5D-/3D-IC-Entwurfsebene durchgeführt. Dazu werden die Daten aus den vorherigen Phasen zusammengeführt, strukturelle ESD-Prüfungen des gesamten Entwurfs durchgeführt, um Berichte über fehlende oder inkorrekte ESD-Schutzschaltungen zu erhalten, und die Gesamt-P2P-Werte für alle korrekten Schutzschaltungen berechnet, um festzustellen, ob diese ausreichend sind.

? Wie wird bei dieser Methode eine Prüfung auf geeignete ESD-Schutzkonzepte durchgeführt?

! Medhat: Layout-Netzlisten für die Baugruppenebene, d.h. Interposer, Schnittstellen und alle Dies, sind aus der Layout-Extraktion verfügbar, die in den Analysen auf Baugruppen- bzw. Die-Ebene durchgeführt wurde. Die komplette 2,5D-/3D-IC-Netzliste wird durch Zusammenführen all dieser Netzlisten zu einer einheitlichen Netzliste erzeugt. Sie ermöglicht es, strukturelle ESD-Prüfungen auf der kompletten 2,5D-/3D-IC-Entwurfsebene durchzuführen.

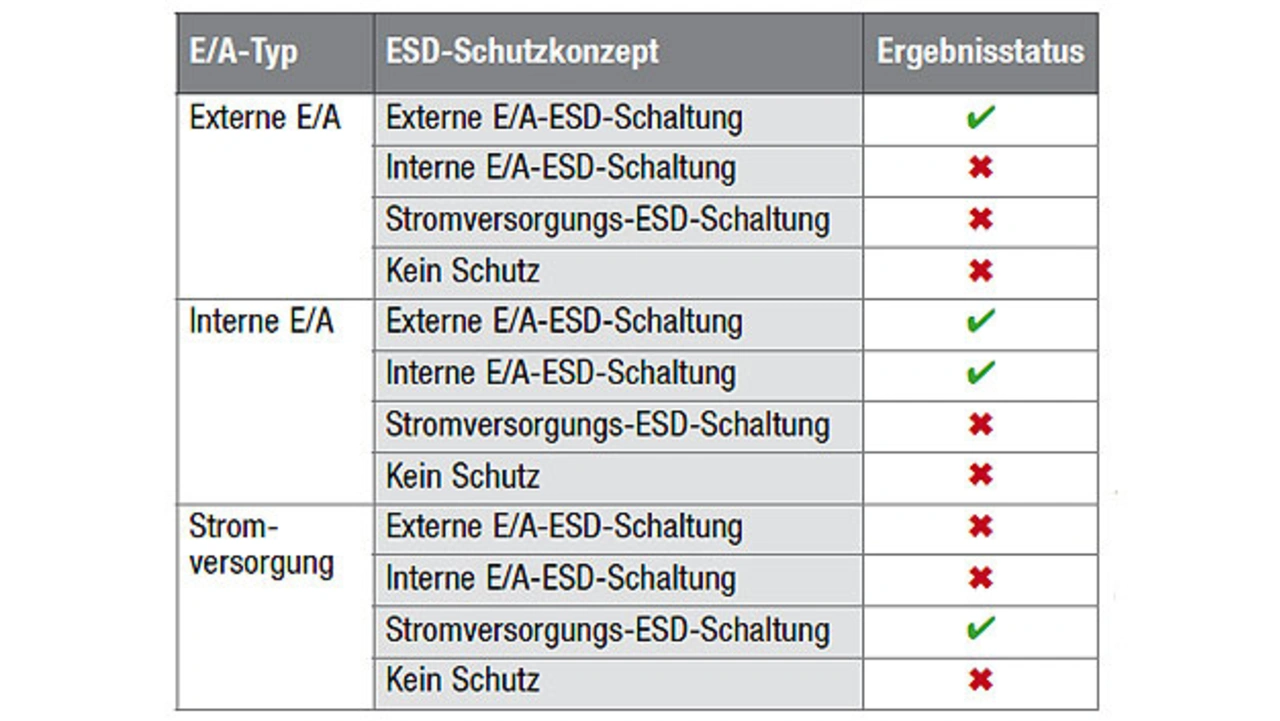

Bei den Schutzkonzepten gibt es drei Kategorien: ESD für externe E/As, ESD für interne E/As und ESD für Stromversorgungsanschlüsse. Der Zweck all dieser ESD-Prüfungen besteht darin, fehlende, falsche und korrekte Schutzkonzepte anhand einer benutzerdefinierten Struktur für jede Kategorie zu identifizieren (Tabelle).

Ein Ergebnis, das bei den Entwicklern Beachtung finden sollte, ist die Verwendung einer externen E/A-ESD-Schaltung für eine interne E/A. Obwohl das externe E/A-Schutzkonzept eine korrekte ESD-Schutzmethode ist, führt es zu einem unnötigen ESD-Schutz. Da interne E/As in der Regel seltener ESD-Ereignissen ausgesetzt sind als externe E/As, können sie normalerweise durch ESD-Schaltungen angemessen geschützt werden, die kleiner als die für externe E/As benötigten sind, was letztlich Platz auf dem Die einspart.

Bei fehlenden/falschen ESD-Schutzkonzepten werden problematische externe E/As und interne E/As als Verstöße gemeldet, die sich debuggen lassen. Für korrekte ESD-Schutzkonzepte werden die jeweiligen externen und internen E/As nur zur Information gemeldet, um das Debugging zu unterstützen. Im Falle von korrekten ESD-Schutzkonzepten wird das Routing validiert, um zu überprüfen, ob dieses Konzept das ESD-Ereignis bewältigen kann, indem der parasitäre P2P-Gesamtwiderstand für jeden korrekten Schutzpfad berechnet und die Stromdichte überprüft werden.

? Was bringt diese ESD-Verifizierung dem IC-Entwickler in der Praxis?

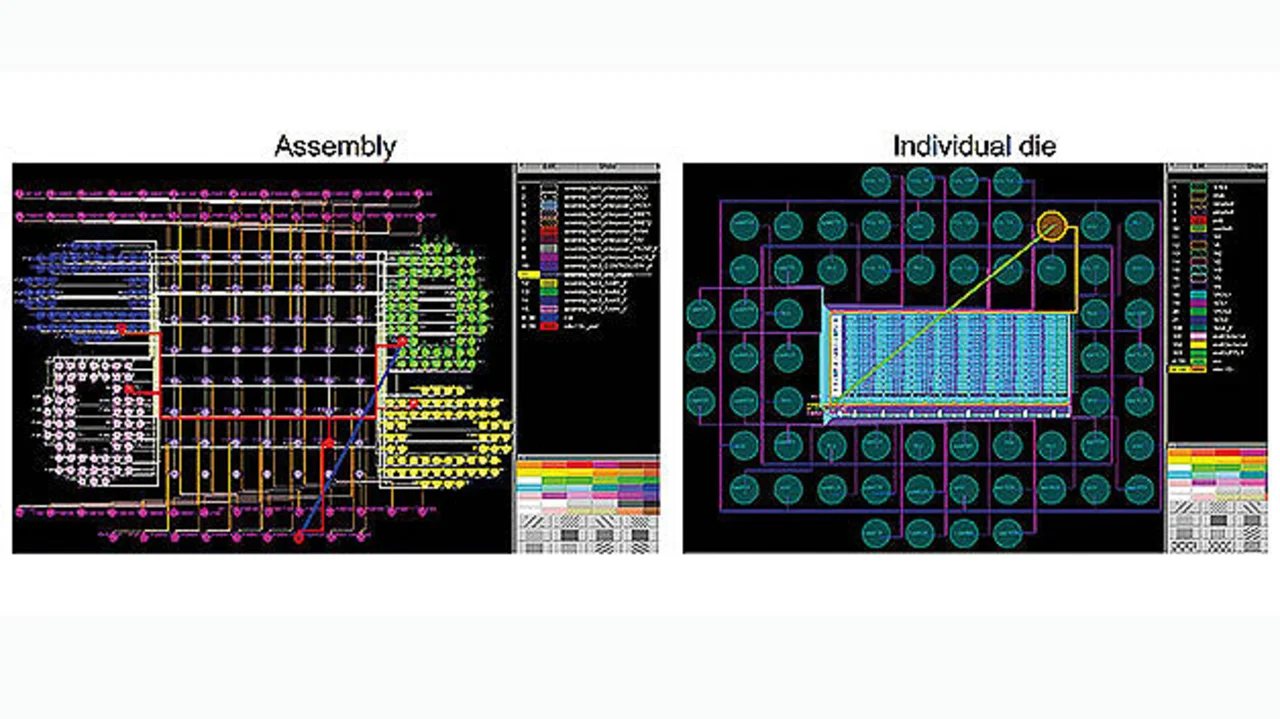

! Medhat: Diese Verifizierungsmethode wurde bei Siemens an einem IC-Entwurf mit insgesamt fünf Dies getestet: vier RAM-Dies (Random Access Memory) und einem Controller-Die (Bild 4).

Die externen und internen E/As wurden bewusst mit fehlenden, falschen oder korrekten ESD-Schutzstrukturen konzipiert. Die Methode identifizierte korrekt alle erwarteten Verstöße und versetzte die Entwickler in die Lage, schnell die richtigen Korrekturen zu identifizieren und anzuwenden.

Aus der Perspektive der ESD-Verifizierung sollten 2,5D-/3D-ICs nicht wie eine Gruppe unabhängiger 2D-ICs behandelt werden, die miteinander verbunden sind. In diesen Entwürfen können die ESD-Schutzschaltungen mehrere Dies umfassen und müssen für eine korrekte Bewertung kombiniert werden. Außerdem sollten ESD-Ereignisse nach den verschiedenen E/A-Typen klassifiziert werden – interne E/As sind weniger ESD-Ereignissen ausgesetzt als externe E/As.

Eine Identifikation der Stellen in den 2,5D-/3D-ICs, an denen sich diese internen E/As befinden, ermöglicht es also, kleinere ESD-Schutzschaltungen vorzusehen, um eine Verschwendung von Platz auf der Chipfläche zu vermeiden. Obwohl die Gewähr-leistung eines angemessenen ESD-Schutzes für einen 2,5D-/3D-IC zahlreiche Aufgaben umfasst, die sorgfältig gehandhabt werden müssen, kann die Implementierung einer Methode zur automatisierten ESD-Verifizierung, wie hier vorgestellt, die Gewährleistung eines genauen und konsistenten ESD-Schutzes erheblich erleichtern.

Dina Medhat

ist technische Leiterin und Senior Technologist für Calibre Design Solutions bei Siemens EDA, einem Unternehmensteil von Siemens Digital Industries Software. Sie hatte mehrere Positionen im Produktmarketing und technischen Marketing von Siemens EDA inne.

Medhat hat einen BS- und MS-Abschluss und promoviert derzeit an der Ain Shams University in Kairo, Ägypten. Zu ihren Forschungsinteressen gehören Zuverlässigkeitsverifizierungen, elektrostatische Entladungen, neue Technologien, integrierte 3D-Schaltungen und physikalische Verifizierungsprozesse.

dina_medhat@siemens.com

- ESD-Schutz für 2,5D-/3D-ICs

- Gibt es eine eigene Methode zur automatisierten ESD-Verifizierung in 2,5D- und 3D-ICs?

- Literatur