Verifikation effizient automatisieren

ESD-Schutz für 2,5D-/3D-ICs

Der Schutz vor elektrostatischer Entladung – auch als ESD-Festigkeit bezeichnet – ist ein wichtiger Aspekt bei der IC-Entwicklung und -Verifikation, auch bei modernen 2,5D-/3D-ICs. Welche Konzepte sich hierfür anbieten, verrät Dina Medhat von Siemens Digital Industries Software im Interview.

ESD-Ereignisse verursachen aufgrund eines plötzlichen und unerwarteten Stromflusses zwischen zwei elektrisch geladenen Gegenständen schwere Beschädigungen an ICs. Solch ein Strom kann durch Kontaktgabe, Kurzschluss oder dielektrischen Ausfall verursacht werden. Zur Unterscheidung wurden drei grundlegenden Ereignismodelle definiert:

- Human Body Model (HBM) – Ein solches ESD-Ereignis lässt sich mit dem Laufen über einen Teppich und der anschließenden Berührung eines metallischen Türknaufs vergleichen.

- Charged Device Model (CDM) – Ähnlich wie das HBM, aber das ESD-Ereignis wird hierbei von externen, nicht mit dem Menschen zusammenhängenden Ereignissen verursacht, z. B. in der Fertigung durch das Herabrutschen eines Bauelements in der Zuführung zum Bestückungsautomaten.

- Maschinenmodell (MM) – Diese ESD-Ereignisse finden im Allgemeinen innerhalb der Schaltkreise eines Bauelements statt.

Jobangebote+ passend zum Thema

Unabhängig von der Ursache können alle ESD-Ereignisse zum Schmelzen von Metallen, zum Ausfall von Verbindungsstellen oder zu einem Durchbruch von Oxidschichten führen. ESD-Ereignisse können ein elektronisches Bauteil in jeder Phase seiner Herstellung oder Verwendung beschädigen, wenn keine geeigneten Schutzmaßnahmen ergriffen werden. Die Folgen von ESD-Ereignissen sind normalerweise vorzeitige Ausfälle von ICs oder eine eingeschränkte Funktion – und keine dieser Folgen wirkt sich günstig auf einen Hersteller aus.

? Wie lassen sich ICs vor ESD-Ereignissen schützen?

! Dina Medhat: Zur Verhinderung oder Minderung von ESD-Schäden an ICs werden mehrere Schutzkonzepte eingesetzt [1, 2]. Dabei müssen die Entwickler bezüglich des Schaltplans – also in der Frühphase des Entwicklungsprozesses – und des Layouts geeignete zusätzliche ESD-Schutzkonzepte integrieren. Die Überprüfung dieser ESD-Schutzschaltungen vor der Fertigung ist entscheidend für einen zuverlässigen IC-Entwurf. In den Handbüchern zu Designregeln sind auch Regeln für den Entwurf von ESD-Schutzschaltungen enthalten, um aus Schaltungssicht das Vorhandensein angemessener ESD-Schutzmaßnahmen zu überprüfen.

? Gibt es tatsächlich einen Unterschied zwischen dem ESD-Schutz für 2,5D-/3D-ICs und dem für 2D-ICs?

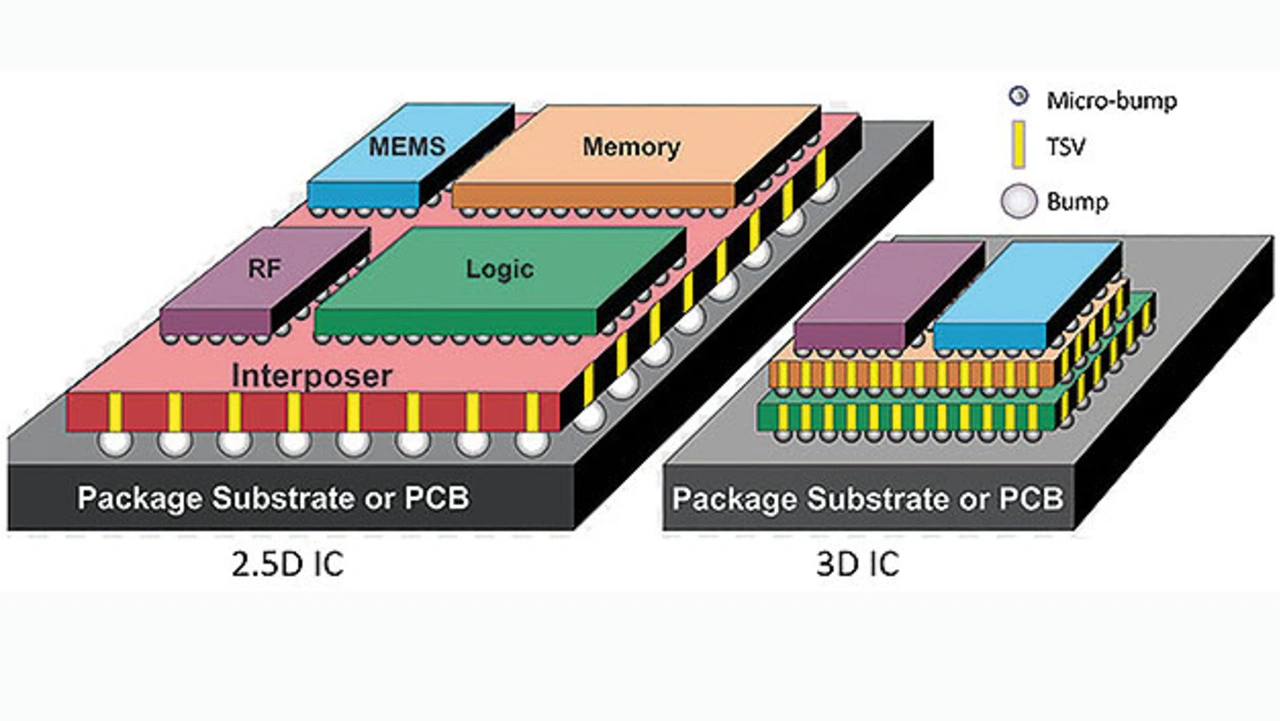

! Medhat: Ja und Nein. Schauen wir uns zunächst den Aufbau der 2,5D-/3D-ICs genauer an: 2,5D-/3D-ICs haben sich für viele herausfordernde Integrationsaufgaben bewährt. 2,5D-ICs bestehen aus mehreren Dies, die nebeneinander auf einem passiven Silizium-Interposer angeordnet sind (Bild 1). Der Interposer wird auf einem organischen BGA-Substrat (Ball Grid Array) platziert. Mikro-Bumps verbinden jeden Die mit dem Interposer, und Flip-Chip-Bumps (C4) verbinden den Interposer mit dem BGA-Substrat. In 3D-ICs werden die Dies übereinander montiert. Zur Verbindung zwischen den Dies und zur Verbindung mit dem Substrat werden Through-Silicon Vias (TSV) verwendet.

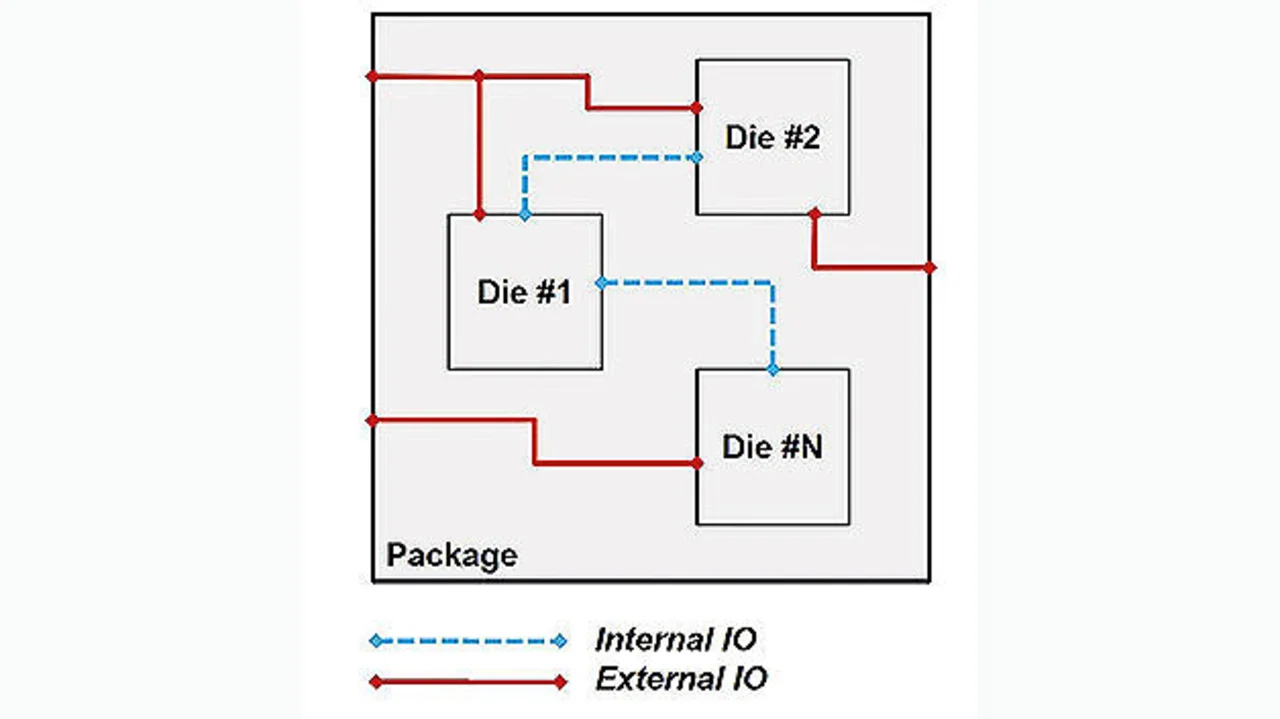

In 2D-ICs fungieren alle Pads als E/A-Schnittstellen, die über die Gehäuse-Pins mit der Außenwelt verbunden sind. Da es in 2,5D- und 3D-Integrationen mehrere Dies gibt, werden einige Pads zur Signalverbindung zwischen den Dies über Mikro-Bumps, TSV und den Interposer verwendet, und haben überhaupt keine Verbindung zur Außenwelt (Bild 2).

Dieser wichtige Unterschied bei 2,5D-/3D-ICs verlangt, dass eine Unterscheidung zwischen diesen beiden Kategorien von Pads getroffen wird. Entweder indem Pads als externe E/A-Anschlüsse, die eine Verbindung zur Außenwelt herstellen, oder als interne E/A-Anschlüsse klassifiziert werden, die nur für Verbindungen innerhalb des 2,5-/3D-IC-Gehäuses sorgen.

Diese Klassifizierung ist für den ESD-Schutz entscheidend, weil externe E/As mit den Gehäuse-Pins verbunden sind und mehr ESD-Ereignissen ausgesetzt sind als interne E/As [3]. Ähnlich wie bei 2D-ICs sind externe und auch interne E/As von HBM- und CDM-ESD-Ereignissen betroffen. Die internen E/As werden jedoch weniger stark von diesen Ereignissen beeinflusst. Aufgrund dieses Unterschieds können die Entwickler für interne E/As kleinere ESD-Schutzschaltungen verwenden. Dies führt wiederum zu entscheidenden Einsparungen bei den Dies und im Kostenbereich ohne Kompromisse an die ESD-Festigkeit. Kurz gesagt: Die ESD-Schutzschaltungen unterscheiden sich nicht, doch wie sie auf einen 2,5-/3D-IC angewendet werden, ist für das Endergebnis von großer Bedeutung.

? Wenn dieselben Schutzschaltungen verwendet werden, worin bestehen dann die Herausforderungen für die Automatisierung der ESD-Verifizierung bei 2,5D-/3D-ICs?

! Medhat: Für die Integration einer automatisierten ESD-Verifizierung in 2,5D-/3D-ICs gibt es eine ganze Reihe von Herausforderungen. Die Anbieter von EDA-Tools (Electronic Design Automation) müssen mit ihren Tools die folgenden Probleme lösen [4]:

- Unterscheidung zwischen dem ESD-Schutz für externe E/As und dem ESD-Schutz für interne E/As.

- Korrekte Berücksichtigung der CDM- und HBM-Beschränkungen für die Verbindungen zwischen den Dies (interne E/As).

- Bestimmung des erforderlichen ESD-Mindestschutzes zur Verhinderung eines Ausfalls des fertigen 2,5D-/3D-ICs.

- Entwicklung eines Tools, das den Einsatz unterschiedlicher Fertigungsknoten und unterschiedlicher Foundries für die im 2,5D-/3D-IC verwendeten Dies ermöglicht und mit den entsprechenden Schnittstellen umgehen kann.

- Bestimmung der Art und Weise der Beschaffung von Dies von unterschiedlichen Herstellern bei gleichzeitiger Gewährleistung eines konsistenten und angemessenen ESD-Schutzes durch den 2,5D-/3D-IC-Entwickler.

- Umgang mit unterschiedlichen ESD-Entwicklungsmethoden.

- ESD-Schutz für 2,5D-/3D-ICs

- Gibt es eine eigene Methode zur automatisierten ESD-Verifizierung in 2,5D- und 3D-ICs?

- Literatur