Quarzoszillatoren

FPGA-basierte Systeme benötigen spezielle Taktgeber

Fortsetzung des Artikels von Teil 3

DSPLL-basierte Oszillatoren

Im Gegensatz dazu verwendet ein DSPLL-basierter Ansatz digitale Verarbeitungsfunktionen, um eine PLL zu implementieren, mit der die Quarz-Referenzfrequenz auf eine höhere Frequenz multipliziert wird. Die gesamte Frequenzsteuerung und das Trimming erfolgen also über digitale Befehle. Das Kompensationsfilter basiert auf einem digitalen Signalprozessor ohne weitere passive Bauelemente.

Der VCO wird ohne Analogschaltkreise digital geregelt. Um eine zusätzliche UDD-Isolation bereitzustellen, kommen ein integrierter Linearregler und ein Entkopplungskondensator zum Einsatz; zugleich erhöht sich die Rauschunterdrückung. Aufgrund dieser Funktionen kann jeder DSPLL-basierte XO/VCXO von Silicon Labs in störbehafteten Umgebungen hochfrequente Taktsignale mit einer Jitter Performance im Sub-ps-Bereich erzeugen.

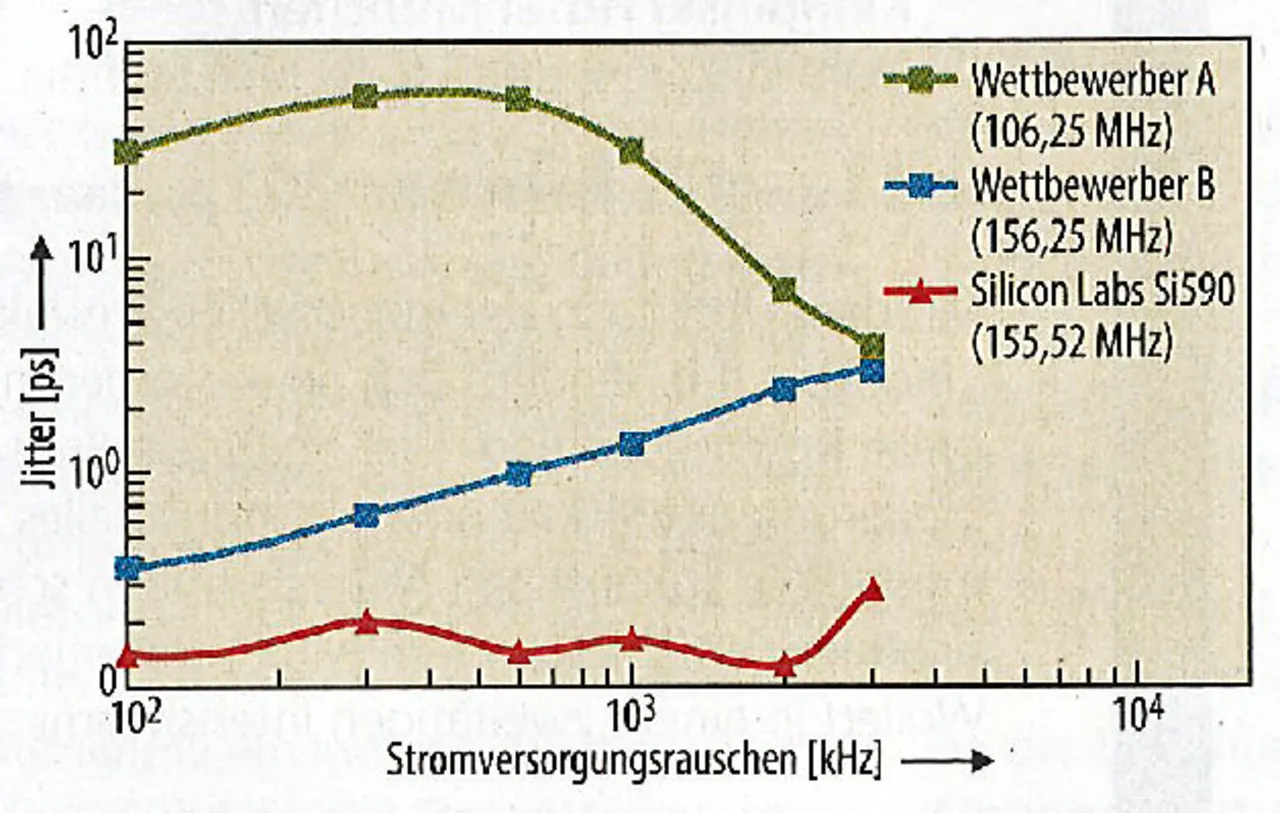

Bild 3 zeigt die Störspannungsunterdrückung eines Fractional-N-PLL-basierten Quarzoszillators (XO) im Vergleich zu DSPLL-basierten XOs. Obwohl der Fractional-N-PLL-XO mit maximal 0,9 ps Jitter ausgewiesen ist, was für ein FPGA-SERDES mit hoher Datenrate ausreicht, bezieht sich dieser Nennwert nur auf ideale Umgebungen. Mit 100 mV Stromversorgungs-Rauschen erzeugen andere Lösungen bis zu 40 ps zusätzlichen Jitter, was schnelle serielle Verbindungen unbrauchbar macht. Silicon Labs DSPLL-basierte XO/VCXOs indes fügen lediglich 0,1 bis 0,3 ps Jitter über die getesteten Frequenzen hinzu.

Andere DSPLL-Taktbausteine von Silicon Labs umfassen Jitter-arme, integrierte PLLs für die Jitter-Dämpfung und Taktmultiplikation. Sie basieren ebenfalls auf einer DSPLL-Architektur, die die UDD-Rauschempfindlichkeit beseitigt. Mit den Si5xx-XO/VCXOs und der Si53xx-Serie mit Any-Frequency-Taktmultiplizierern lassen sich hocheffiziente Schaltnetzteile realisieren und gleichzeitig geringe Jitter-Werte erzielen. Entwickler können zudem durchgehende Versorgungs- und Masse-Ebenen implementieren, ohne dass Linearregler auf dem Board verstreut montiert werden müssen.

Damit ergibt sich eine Masse-Ebene mit geringster Impedanz und den wenigsten Unterbrechungen. Die integrierte Leistungsregelung verbessert das Systemverhalten, verringert die Leiterplattenfläche und die Systemkosten, vereinfacht das Design und beschleunigt die Markteinführung.

Jobangebote+ passend zum Thema

- FPGA-basierte Systeme benötigen spezielle Taktgeber

- Schaltregler – der goldene Ausweg?

- Einsatz von Quarzoszillatoren

- DSPLL-basierte Oszillatoren