Quarzoszillatoren

FPGA-basierte Systeme benötigen spezielle Taktgeber

Fortsetzung des Artikels von Teil 1

Schaltregler – der goldene Ausweg?

Eine bessere Möglichkeit, den Wirkungsgrad zu erhöhen und eine Regelung über einen weiten Lastbereich zu garantieren, sind Schaltregler. Sie bieten einen Wirkungsgrad von 85 bis 95 Prozent und sind damit oft die einzige Leistungswandler-Alternative für FPGAs. Der höhere Wirkungsgrad sorgt allerdings für mehr Rauschen, das 50 bis 100 mV Störspannung (Spitze zu Spitze) betragen kann. Aufgrund der hohen Leistungsaufnahme durch die FPGA-Logik und I/Os kann ein Schaltungsrauschen von weniger als 50 mV nur teuer erkauft werden und ist daher unpraktisch.

Eine weitere Rauschquelle ist das FPGA selbst. Der Fabric-Systemtakt kann Hunderte MHz betragen. Beim Betrieb von Digitallogik mit hoher Leistung entstehen Störtransienten, die sich durch die verschiedenen Versorgungsebenen hindurch fortpflanzen. Schnelle Transienten erzeugen Pulse mit hoher Energie, die von Stromversorgungsfiltern nur schwer zu bereinigen sind. Da die Stromversorgungsentkopplung meist so optimiert ist, dass sie eine geringe Impedanz bei einer oder wenigen Frequenzen aufweist, ist es nahezu unmöglich, alle Rauschanteile bei höheren Frequenzen herauszufiltern. Dieses Rauschen pflanzt sich in andere Subsysteme der Stromversorgung fort, vor allem in jene, die in der Nähe des FPGA angeordnet sind.

Lastschwankungen als weitere Störquelle

FPGAs sorgen für eine weitere Herausforderung: Wenn Logikblöcke oder I/Os zwischen dem High- und Low-Betriebszustand hin- und herschalten, schwankt der Laststrom erheblich. Gehen die Logikblöcke in den High-Status über, findet eine intensive Verarbeitung statt und die Stromversorgung erfährt eine Lastschwankung. Geht der Logikblock in einen Zustand mit geringerer Leistungsaufnahme über, verschwindet die Lastschwankung und die Versorgungsschienen gehen in den Sollzustand über. Mehrere Ereignisse können erhebliche Lastschwankungen verursachen, wobei das Zusammenspiel aller Ereignisse unmöglich vorherzusagen oder zu regeln ist. Solche Laständerungen erzeugen eine niederfrequente Hüllkurve mit einer Frequenz von weit unter 100 kHz. Dieses Rauschen lässt sich mit zusätzlichen Reglern beseitigen, was aber die Kosten und die Leiterplattenfläche erhöht.

Gemeinsame Stromschienen schaffen Probleme

Wenn empfindliche Analogbausteine die gleiche Stromschiene wie die FPGAs nutzen, ist dies eine Herausforderung. In vielen Fällen ergibt sich eine unerklärliche Leistungsminderung oder ein anormales, unvorhersehbares Verhalten. Die übliche Lösung ist die Isolation jedes empfindlichen Timing-Subsystems auf seiner eigenen Versorgungsinsel. Dabei wird mit Linearreglern das niederfrequente Rauschen herausgefiltert, und umfangreiche LC-Filter mit Ferritperlen und Keramikkondensatoren zur Entkopplung filtern höhere Frequenzen.

Dies ist jedoch keine ideale Lösung, da sie teuer ist und die Layout-Komplexität erhöht. Zudem werden die Versorgungsebenen unterbrochen, was die Effizienz hinsichtlich geringer Impedanz und eng gekoppelter Masserückführung verschlechtert. Besser ist es, eine durchgehende Versorgungsebene sicherzustellen, die möglichst über das gesamte Board hinweg intakt bleibt. Dabei muss jedes Subsystem allerdings Rauschen seitens der Stromversorgung tolerieren.

Jobangebote+ passend zum Thema

- FPGA-basierte Systeme benötigen spezielle Taktgeber

- Schaltregler – der goldene Ausweg?

- Einsatz von Quarzoszillatoren

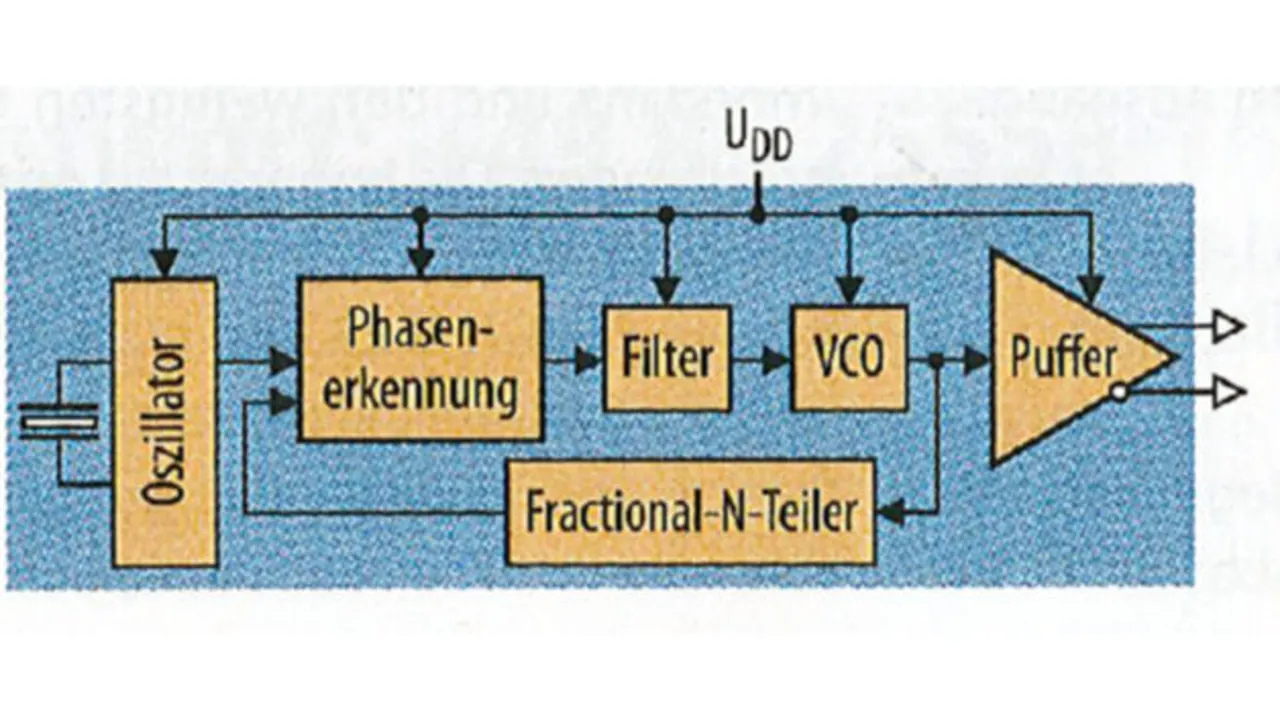

- DSPLL-basierte Oszillatoren