Quarzoszillatoren

FPGA-basierte Systeme benötigen spezielle Taktgeber

Fortsetzung des Artikels von Teil 2

Einsatz von Quarzoszillatoren

Heutige FPGAs erfordern Taktquellen, beispielsweise Quarzoszillatoren von Silicon Laboratories, mit sehr geringem Jitter, um die Anforderungen der Endanwendung zu erfüllen. Die Bilder 1 und 2 zeigen diesbezüglich zwei Arten von Quarzoszillatoren, zumal Quarze ein geringes Phasenrauschen und hohe Frequenzgenauigkeit aufweisen. Trotz dieser Vorteile haben Quarze einen großen Nachteil: Die Grundfrequenzschwingung ist auf unter 50 MHz begrenzt.

Für die meisten hochleistungsfähigen Anwendungen muss nach dem Quarz eine PLL folgen, die diese niedrige Frequenz multipliziert, um die erforderliche Ausgangsfrequenz zu erhalten. PLLs übernehmen die Multiplikation der Grundfrequenz um ganze Zahlen – zum Beispiel 3 – oder um Teilwerte wie 3,125.

Die Fractional-N-Topologie in Bild 1 umfasst einen Quarzoszillator, gefolgt von einem analogen Phasendetektor, Kompensationsfilter, VCO und einem Fractional-N-Rückkopplungsteiler. Die Ausgangsfrequenz entspricht der Eingangsfrequenz, die im Verhältnis 1/N skaliert werden kann. Ein rauscharmer Puffer steuert die externen Lastschaltkreise. Viele Anwendungen wie Gigabit Ethernet, Fibre Channel und High Definition Serial Digital Video (HD-SDI) benötigen Taktquellen mit geringem Jitter und Ausgangsfrequenzen von 100 bis 156,25 MHz.

Unter idealen Versorgungsbedingungen kann ein Fractional-N-PLL einen geringen Jitter von weniger als 1 ps im gesamten Band von 10 kHz bis 20 MHz erreichen. Im Gegensatz dazu hat ein Oszillator in störbehafteter Umgebung damit zu kämpfen, den im Datenblatt spezifizierten Phasen-Jitter zu erreichen. Außerdem bilden analoge Sub-Schaltkreise empfindliche Knoten, über die Störungen in den Schaltkreis gelangen können. Ist dies der Fall, werden diese Störungen meist verstärkt und erzeugen so einen Phasen-Jitter am Ausgang.

Jobangebote+ passend zum Thema

- FPGA-basierte Systeme benötigen spezielle Taktgeber

- Schaltregler – der goldene Ausweg?

- Einsatz von Quarzoszillatoren

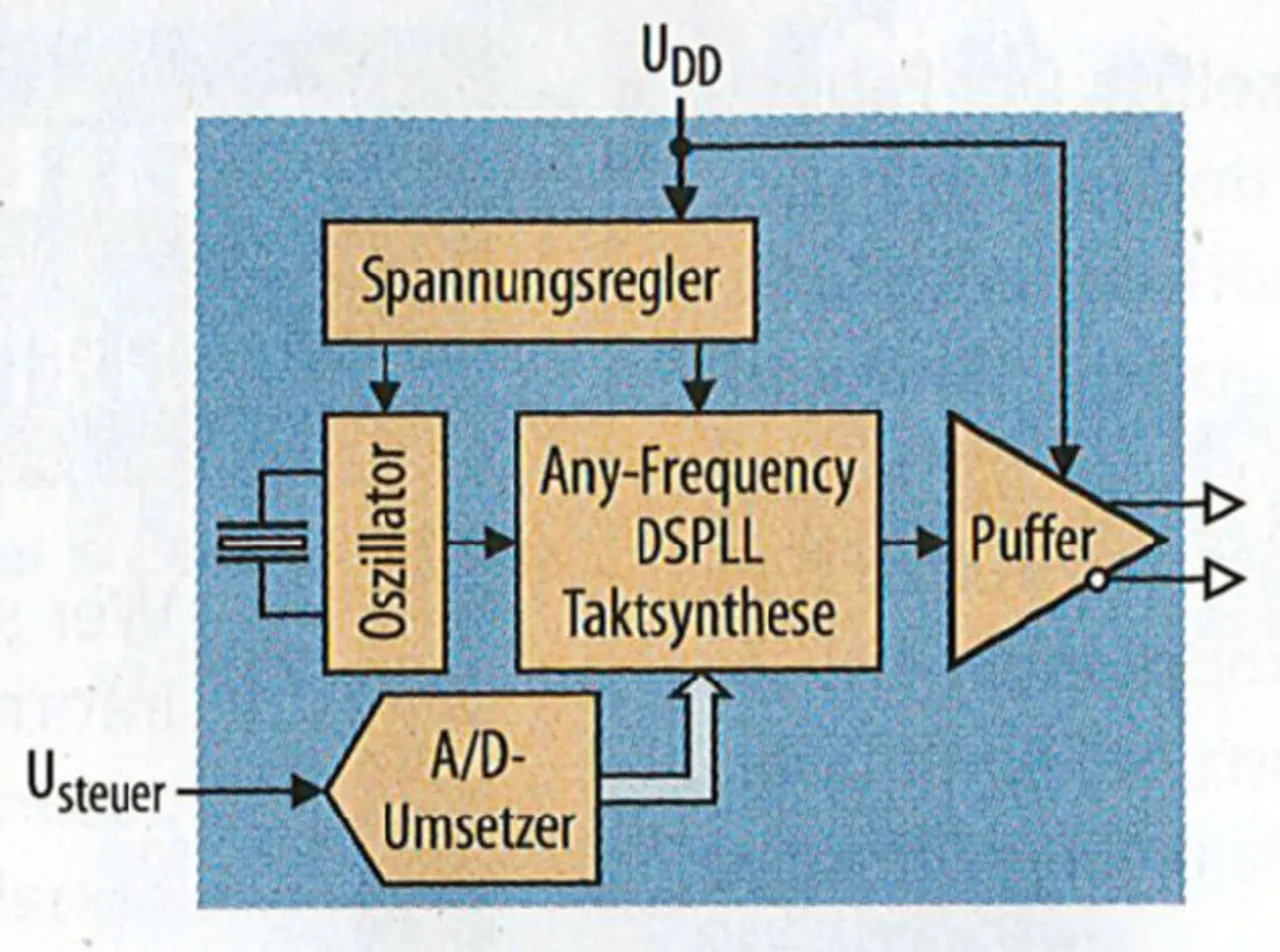

- DSPLL-basierte Oszillatoren