Intelligente Layoutverarbeitung

KI für ASIC- und PCB-Layouts

Fortsetzung des Artikels von Teil 1

Anwendung auf reale Designs – ASICs

Analog-zu-Digital-Umsetzer (ADU) stellen besondere Herausforderungen an das Layout: Gerade hier müssen Symmetrien eingehalten und z.B. Kreuzungen von digitalen Schaltsignalen und analogen Messgrößen vermieden werden. Am IMMS werden z.B. ADUs entwickelt, die nach dem Prinzip der sukzessiven Approximation arbeiten (SAR, Successive Approximation Register). Das Layout eines solchen ADUs liegt in zwei Versionen vor: Im ersten Schritt wird das Layout von einem unerfahrenen Ingenieur erstellt und im zweiten Schritt durch einen erfahrenen Layouter überarbeitet.

Jobangebote+ passend zum Thema

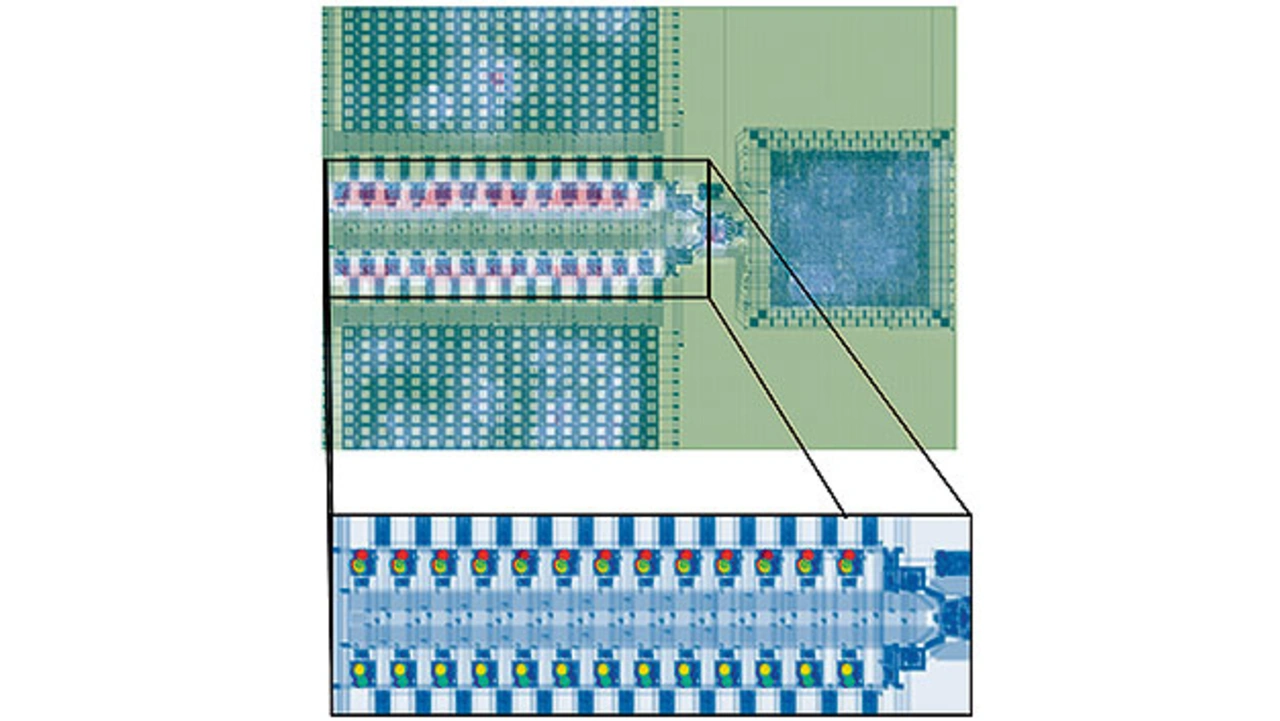

Das Layout des erfahrenen Layouters wurde zum Training des Algorithmus verwendet. Die verschiedenen Signalleitungen wurden dazu in Kategorien eingeteilt, die im »Farbkanal« der Querschnitte eingefügt wurden. Nach dem Training des Autoencoders wurde er zur Untersuchung der ersten Layoutvariante herangezogen. Die dabei entstandenen Rekonstruktionsfehler wurden in Bild 5 farblich im Layout in einer Heatmap markiert, wobei rote Bereiche Stellen mit größerem Rekonstruktionsfehler darstellen.

Es zeigt sich, dass der Algorithmus genau die Bereiche markiert hat, die in der Überarbeitung stark angepasst wurden, um die Leistung des AD-Umsetzers zu verbessern. Außerdem lassen sich die Fehlerstellen automatisch in verschiedene Kategorien einteilen, die in zukünftigen Analysen näher untersucht und verbessert werden sollen – z.B. darauf, ob dem Ingenieur Hinweise zur Verbesserung gegeben werden können.

Neben diesen erkannten Anomalien treten vereinzelt Artefakte auf, die in einer übergreifenden Analyse adressiert werden können. Wird das System so auf mehrere Entwürfe angewendet und der Trainingsdatensatz jeweils mit den »guten« Entwürfen erweitert, ist zu erwarten, dass die Erkennungsgenauigkeit ansteigt und so immer zielgerichteter mögliche Fehlerstellen erkannt werden können.

Anwendung auf reale Designs – Leiterplattenlayouts

Die Forschergruppe IntelligEnt hat ein studentisches Softwareprojekt an der TU Ilmenau betreut, in dem das Anomalieerkennungsverfahren als Plug-in für das freie PCB-Entwurfswerkzeug KiCad entwickelt wurde – siehe Kasten: Handhabung des ML-KiCad-Plug-ins »AnoPCB«. Mit dem Plug-in können in KiCad Signale in Kategorien eingeteilt und an den Trainings- bzw. Evaluationsprozess übergeben werden. Das System wurde so entworfen, dass die Entwurfsdaten beim Benutzer auf die für den Autoencoder notwendigen Querschnitte reduziert und dann an einen zentralen Server zur Verarbeitung übermittelt werden. So wird einerseits ein ggf. notwendiger Grafikprozessor nur im Server benötigt und andererseits können die Entwürfe mehrerer Benutzer kombiniert werden.

Für ein erstes Training wurde dabei auf quelloffene Entwürfe gesetzt, u.a. aus den Projekten »Crazyflie« und »HackRF«. Die Signale der Entwürfe wurden in Kategorien eingeteilt und dem Programm übergeben. Zur Evaluation wurden die in Bild 6 dargestellten Signale so verändert, dass sie von der Anomalieerkennung erkannt werden sollten: So wurde z.B. eine Taktleitung über einen sensitiven HF-Teil geführt.

Die Auswertung zeigt, dass die eingebauten Fehlerstellen korrekt erkannt wurden. Aufgetretene Artefakte bzw. falsch positive Regionen, die vermeintlich fehlerhaft sind, können beispielsweise dadurch erklärt werden, dass sie im Trainingsdatensatz unterrepräsentiert waren. Jedoch sollte dieser Effekt nach einer Erweiterung des Trainingsdatensatzes vermindert werden oder sogar ganz verschwinden.

Erweiterung auf andere Layouttypen

Die entwickelte Methode zur Anomalieerkennung auf Layoutdaten wurde in zwei verschiedenen Szenarien demonstriert. Sowohl im ASIC- als auch im PCB-Entwurf können damit Abweichungen von guter Designpraxis erkannt werden. Derzeit werden dafür jedoch nur Signalinformationen im Sinne von Signalkategorien – Analog, Digital, Taktsignal usw. – im Algorithmus abgebildet. Eine Kombination mit Simulations- oder Messdaten könnte die Treffsicherheit des Verfahrens stark verbessern – und zudem die Handhabung vereinfachen, da diese Informationen nicht manuell eingetragen werden müssen.

Eine Erweiterung auf andere Layouttypen wie z.B. MEMS-Layouts ist ebenso denkbar wie eine Anpassung und Verbesserung der eingesetzten Machine-Learning-Verfahren. Durch z. B. zusätzliche Klassifizierung könnten der genaue Fehlerfall identifiziert und dadurch Hinweise zur Behebung gegeben werden. Eine Kombination mit automatischen Layoutalgorithmen ist erfolgversprechend, da diesen so nahezu »menschliche« Designerfahrung mitgegeben werden kann.

Die Forschergruppe IntelligEnt wurde gefördert durch den Freistaat Thüringen aus Mitteln des Europäischen Sozialfonds unter dem Kennzeichen 2018 FGR 0089.

Die Autoren

Georg Gläser

ist dem IMMS Institut für Mikroelektronik- und Mechatronik-Systeme seit dem Studium durch Praktika und später als wissenschaftlicher Mitarbeiter verbunden. Er beschäftigt sich mit dem Entwurf integrierter Digitalschaltungen und leitet Forschungsprojekte für KI- basierte Entwurfsautomatisierung.

Georg.Glaeser@imms.de

Julian Kuners

ist Student der Ingenieurinformatik an der TU Ilmenau und seit dem hier vorgestellten Softwareprojekt zum KiCad-Plug-in auch als wissenschaftliche Hilfskraft mit dem IMMS Institut für Mikroelektronik- und Mechatronik-Systeme verbunden. Er entwickelt Software und beschäftigt sich zusätzlich mit Hardwareentwicklung.

Julian.Kuners@imms.de.

- KI für ASIC- und PCB-Layouts

- Anwendung auf reale Designs – ASICs