Tools für Embedded-Systeme

KI-Anwendungen erfolgreich entwickeln

Fortsetzung des Artikels von Teil 1

Existierende Tools und Ressourcen nutzen

Noch vor zehn Jahren mussten die Pioniere der KI-Technik in Embedded-Systemen alles von Grund auf selbst entwickeln – einschließlich der Tools zum Kompilieren eines Modells für die jeweilige Ziel-Hardware. Heute ist das völlig anders: Sofern gewünscht, können Entwickler nahezu jeden Aspekt eines neuen ML-Systems mit bereits verfügbaren Tools, Daten und Algorithmen implementieren. Geht es um das Entwickeln eines marktfähigen Produkts, können Entwickler ihre Erfolgschancen mit den existierenden Ressourcen klar verbessern.

Die ohnehin schon große Auswahl an neuronalen Netzen oder KI-Modellen wächst stetig. Oft ist das Finden der besten Möglichkeit für eine bestimmte Anwendung ein empirischer Prozess aus Versuch und Irrtum. Besonders hilfreich sind somit Plattformen, die den Transfer von Trainings-Datensätzen von einem Modell zum anderen erleichtern – zum Beispiel die VectorBlox-FPGAs von Microchip. Sie bieten die Möglichkeit zum Integrieren und Migrieren von Daten von einem ML-Modell zum anderen.

Ebenso wichtig wie das Modell selbst sind die Daten, auf deren Basis es ein Entwickler trainiert. Die Datensätze müssen also zu dem Zweck mit Labels und Tags versehen sein. Ein Personenzählsystem zum Beispiel benötigt zum Einarbeiten einen Datensatz mit Bildern von Menschen. Für ein Zustandsüberwachungssystem dagegen ist ein Datenbestand mit Vibrationsmustern und anderen charakteristischen Bewegungsdaten erforderlich.

Erfolgreich umgesetzte Ansätze von ML nutzen häufig allgemein verfügbare Trainings-Datensätzen oder beginnen oftmals mit ihnen. In Anwendungen, in denen es beispielsweise um das einfache Detektieren von Menschen oder Tieren geht, stehen derartige Datensätze in großem Umfang bereit. In anderen Anwendungen kann es dagegen nötig sein, einen neuen Datensatz zu erstellen oder einen allgemein verfügbaren Datenbestand zu erweitern. Embedded-Entwicklern sollte bewusst sein, welches Arbeitsvolumen hiermit einhergeht. Tatsächlich kann es mehrere Tage dauern, einen kompletten Datensatz zu erstellen, denn jede Probe ist präzise und in einem standardisierten Format zu taggen. Lediglich so lässt sich das neuronale Netzwerk effektiv trainieren.

Allgemein gilt außerdem die Regel, dass das trainierte neuronale Netzwerk um so leistungsfähiger ist, je mehr Daten der Datensatz enthält. In Anwendungen zur Objekterkennung etwa werden die neuronalen Netze erfolgreicher ML-Ansätze routinemäßig mit einem Datenbestand trainiert, der bis zu 10 Mio. mit Labels versehene Bilder der relevanten Objekte enthält. Selbstverständlich hängt der Parameter, ebenso wie jeder andere, von der Anwendung ab. Wichtig ist, wie genau die vom Modell getroffene Entscheidung ist. Ein größerer Datensatz macht es möglich, das Modell so zu trainieren, dass es präzise Entscheidungen fällt. Jedoch wirken sich die Genauigkeitsanforderungen ebenso auf den Code-Umfang des kompilierten Modells aus. Somit beeinflussen sie die Kapazität, die Kosten und die Leistungsaufnahme der eingesetzten Hardware.

Eingesetzte Hardware entscheidend

Ist das Modell hinreichend trainiert, um das erforderliche Maß an Genauigkeit bei der Entscheidungsfindung zu erreichen, geht es im letzten Schritt darum, es für eine Hardware-Inferenzmaschine zu kompilieren.

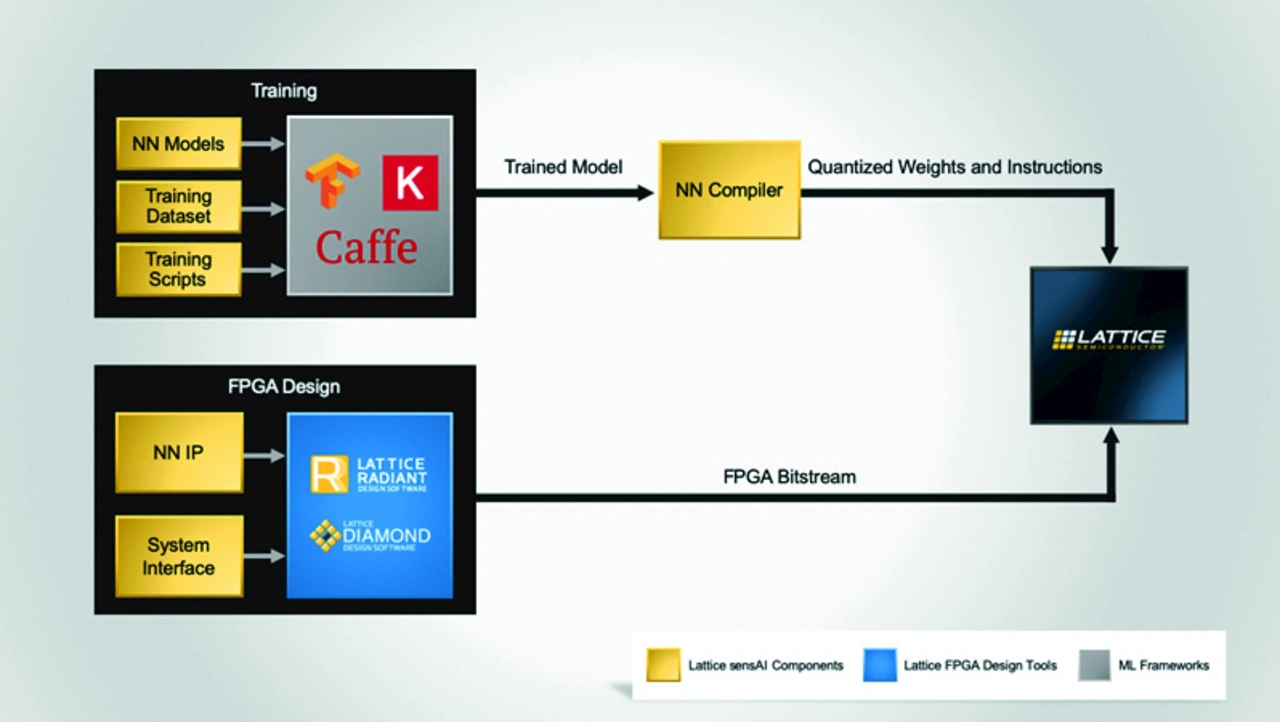

Handelt es sich bei dem vom System implementierten ML-Algorithmus um ein neuronales Netzwerk, ist ein FPGA aufgrund seiner hochgradig parallelen Struktur die ideale Plattform. Ein Entwickler muss die Ausgaben der Tools, die für das Trainieren des neuronalen Netzwerkes benutzt wurden, in ein zur gewählten Hardware-Plattform kompatibles Format übertragen. Obwohl FPGA-Hersteller solche Kompilierungs-Werkzeuge für ihre Produkte anbieten, ist Vorsicht geboten. Möglicherweise unterstützen die Tools nicht alle Arten und Größen von neuronalen Netzwerkmodellen. Die derzeit populärsten Tools für das Trainieren neuronaler Netze sind TensorFlow, Caffe und Keras. Wählt ein Entwickler ein FPGA als Hardware-Plattform für eine ML-Anwendung, sollte er darauf achten, dass das Kompilierungswerkzeug diese Frameworks oder ein anderes, vom OEM verwendetes Trainings-Tool unterstützt.

Den abschließenden Schritt bildet der standardmäßige Design Flow, der den zum Programmieren des FPGA erforderlichen Bitstream generiert. Ein FPGA-Hersteller wird stets gewährleisten, dass seine Entwicklungsumgebung kompatibel zu den von ihm angebotenen oder unterstützten Werkzeugen ist. Das zunehmende Interesse am Implementieren von KI am Edge hat vorausschauende Hersteller dazu veranlasst, Tool-Sätze und Produkte genauso wie Referenzdesigns für Machine Vision und Zustandsüberwachung zu entwickeln. Sie eignen sich ebenso für FPGAs.

Jobangebote+ passend zum Thema

Zum Beispiel bietet Lattice Semiconductor eine umfangreiche Auswahl an Services und Tools, zum Beispiel »sensAI«, an. Hiermit will das Unternehmen Anwendern seiner iCE40- oder ECP5-FPGAs sowie den auf der Nexus-Plattform basierenden Familien CrossLink-NX und Certus-NX die Möglichkeit geben, trainierte Modelle auf die Plattformen zu portieren (Bild 2). Jedoch umfasst der sensAI Stack ebenso modulare Hardware-Plattformen, exemplarische Demonstrationen, Referenzdesigns, Neurale-Netzwerk-IP-Cores sowie Software Tools für das Entwickeln sowie kundenspezifische Design Services.

Besonders nützlich ist der umfassende Stack für das rationelle Entwickeln von Anwendungen, die Lattice mit Referenzdesigns unterstützt, wie etwa das Zählen von Personen. Von Lattice gibt es fertig ausgearbeitete Trainingsskripte und Datensatzbeispiele. Zum Beispiel für das Trainieren der Modelle in einem Standard-Framework wie Caffe, genauso wie Tools zum Kompilieren des fertigen Modells für die gewählte Ziel-Hardware.

Auf der anderen Seite strebt Microchip mit seinem Neural-Netzwerk-Inferenz Tool VectorBlox an, Entwicklern eine Möglichkeit zum Implementieren von KI zu bieten, ohne dass sie dafür FPGA-Know-how benötigen. Das auf einer KI-Engine und einem Software Development Kit basierende VectorBlox-Tool kompiliert ein in TensorFlow, Caffe, PYtorch, DarkNet oder ONNX trainiertes neuronales Netzwerkmodell zu einem Binary Large Object (BLOB). Anschließend können Anwender das BLOB von der KI-Engine in einem PolarFire-FPGA implementieren. So unterstützt das VectorBlox-System mehrere Arten neuronaler Netze und bietet Anwendern zudem den Freiraum, dynamisch von einem zum anderen zu wechseln.

Innovationen – ja bitte!

Selbstverständlich ermöglicht KI ehrgeizige Innovationen für OEMs. Sie müssen jedoch bereit sein, sich Großes vorzunehmen und ein experimentelles Entwickeln in Angriff zu nehmen. Das birgt zwar ein hohes Ausfallrisiko, bringt im Erfolgsfall jedoch genauso viel ein. Zuerst gewagte Experimente entwickeln sich im Laufe der Zeit möglicherweise zu Mainstream-Anwendungen. Zumindest jedoch bringen sie neue Chancen auf dem KI- und ML-Sektor. In allen Fällen bieten FPGAs von Herstellern wie Microchip oder Lattice Semiconductor dank ihrer besonderen Fähigkeiten eine Plattform, die sich für das Implementieren KI-basierter Designs eignet. FPGA-Experten von Future Electronics stehen in jeder Phase des Prozesses mit Ratschlägen, Unterstützung und Anleitung bereit.

- KI-Anwendungen erfolgreich entwickeln

- Existierende Tools und Ressourcen nutzen