Methodisch vorgehen

Digitale Sicherheitsmechanismen in kritischen Systemen

Fortsetzung des Artikels von Teil 2

Ergebnisse der Methodik

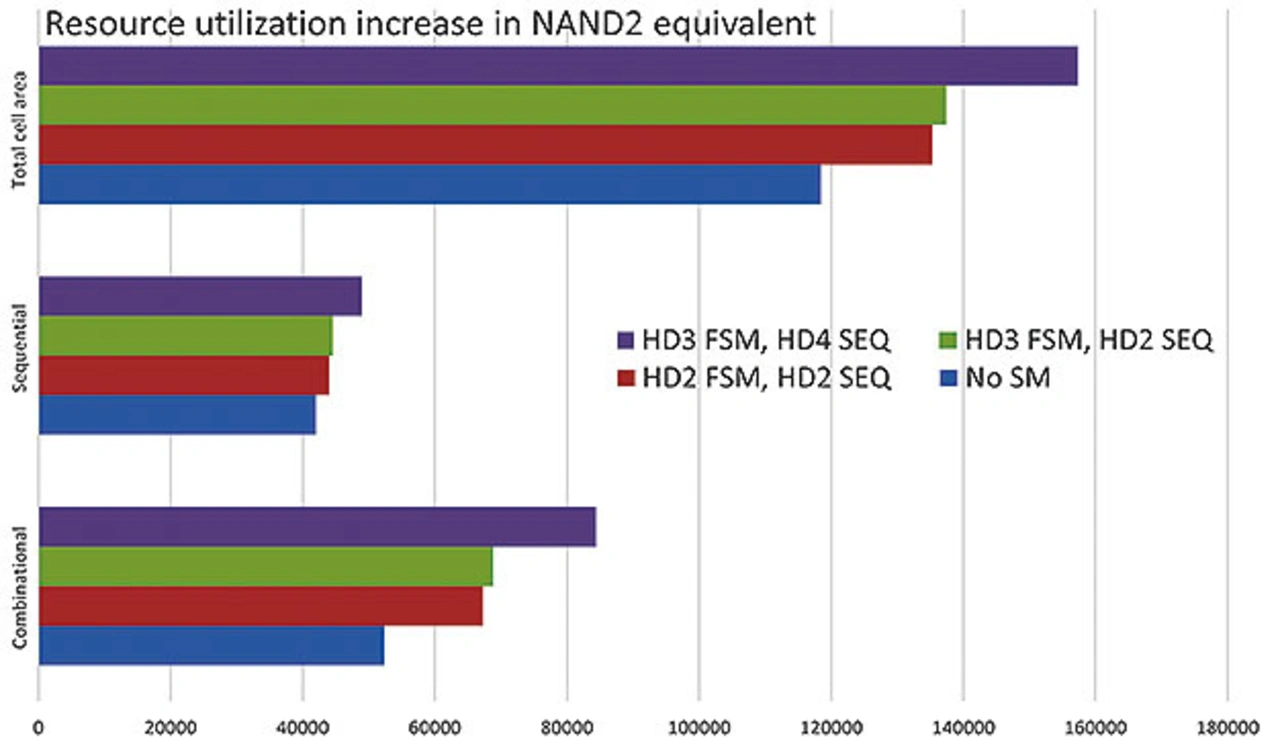

➔ Flächennutzung: Die Methodik ermöglicht eine frühzeitige Abschätzung der FuSa-bezogenen Auswirkungen in Form von Logikgattern. Die Entwickler können die Auswirkungen auf den Bereich bewerten, wenn sie unterschiedliche Prüfsummen und entsprechende Metriken nutzen. Mit diesen Zahlen ist es möglich, zu beurteilen, ob das IC in das projizierte Budget passt oder nicht, und Gegenmaßnahmen zu ergreifen (Bild 6).

➔ Design-Updates: Ein einheitlicher Ansatz für die Anwendung gängiger SMs kann die Design-Updates während der Projektentwicklung vereinfachen. Es beschleunigt auch die Entwicklungsphase, ermöglicht eine einfachere Nachverfolgung und erleichtert die Designüberprüfungen. Die Durchsetzung einer einheitlichen Methodik ist skalierbar, strukturell und insbesondere bei Großprojekten nützlich.

➔ Risikominderung: Die Verwendung einer Bibliothek mit verifizierten Blöcken, die dedizierte SMs im gesamten Design implementieren, reduziert das Gesamtdesign-risiko, beispielsweise die Implementierung falscher Funktionen oder das Auftreten von Fehlern.

➔ Flexibilität: Der vorgeschlagene Ansatz ermöglicht einfache Änderungen am Teil des Entwurfs auch in den späten Entwurfsphasen. Dieser kann weiter verbessert und erweitert werden, um verschiedene gängige SMs zu berücksichtigen, um eine Vielzahl von Designanforderungen zu erfüllen. Die Methodik lässt sich mit Techniken kombinieren, die in den Backend-Design-Flow-Tools (Synthese, Ort und Route) angewendet werden, um eine noch bessere Diagnoseabdeckung und ASIL-Metrik zu erzielen.

Literatur

[1] ISO 26262-2:2018, Road vehicles – Functional safety – Part 2: Management of Functional Safety, ISO, 2018.

[2] ISO 26262-3:2018, Road vehicles — Functional safety — Part 3: Concept phase.

[3] ISO 26262-5:2018, Road vehicles — Functional safety — Part 5: Product development at the hardware level, ISO, 2018.

[4] ISO 26262-9:2018, Road vehicles — Functional safety — Part 9: Automotive Safety Integrity Leve (ASIL) oriented and safety-oriented analyses.

[5] ISO 26262-10:2018(E), Road vehicles – Functional safety – Part 10: Guidelines on ISO 26262, ISO, 2018.

[6] Skliarova I. (2005) Self-correction of FPGA-Based Control Units. In: Yang L.T., Zhou X., Zhao W., Wu Z., Zhu Y., Lin M. (eds) Embedded Software and Systems. ICESS 2005. Lecture Notes in Computer Science, vol 3820. Springer, Berlin, Heidelberg.

[7] Cummings, Clifford. State Machine Coding Styles for Synthesis. 1998.

Der Autor

Trifon Trifonov

ist Staff Digital Design Engineer bei der Renesas Design Bulgaria Unit (RDBU) von Renesas Electronics Europe und arbeitet seit vier Jahren für das Unternehmen. Er verfügt über umfangreiche Erfahrung im Bereich Digital- und Mixed- Signal-Designs. Derzeit leitet er die digitalen Design-Aktivitäten für mehrere Automotive-Produkte im Zusammenhang mit der neuen Generation von Positionserfassungs-anwendungen.

trifon.trifonov.uw@renesas.com

- Digitale Sicherheitsmechanismen in kritischen Systemen

- Implementierung in RTL

- Ergebnisse der Methodik