Methodisch vorgehen

Digitale Sicherheitsmechanismen in kritischen Systemen

Fortsetzung des Artikels von Teil 1

Implementierung in RTL

Die RTL-Implementierung, die sich aus den vorgeschlagenen Systemen zur Erkennung von Fehlern ableitet, muss einer Reihe von Codierungsrichtlinien entsprechen. Die folgende Konvention wird für jeden Block übernommen, der direkt gegen das SG verstoßen kann – drei Top-Level-Parameter für SV werden in der gesamten Hierarchie des Designs hinzugefügt. Jeder von ihnen verarbeitet und instanziiert bedingt die Logik, die für die Erkennung von Fehlern erforderlich ist in:

➔ Sequenzielle Logik – SM_FF

➔ FSM-Logik – SM_FSM

➔ Kombinatorische Logik – SM_COMB

Diese Parameter unterstützen die folgenden Werte – 0, 1, 2 und 3. Sie definieren jeweils »No SM implemented« und »HD of 2-, 3- or 4-Bits«. Im Allgemeinen ist die Erkennung von Dual-Bit-Fehlern für die meisten Anwendungsfälle ausreichend. Die Werte der HD-Parameter können bei Bedarf weiter erweitert werden.

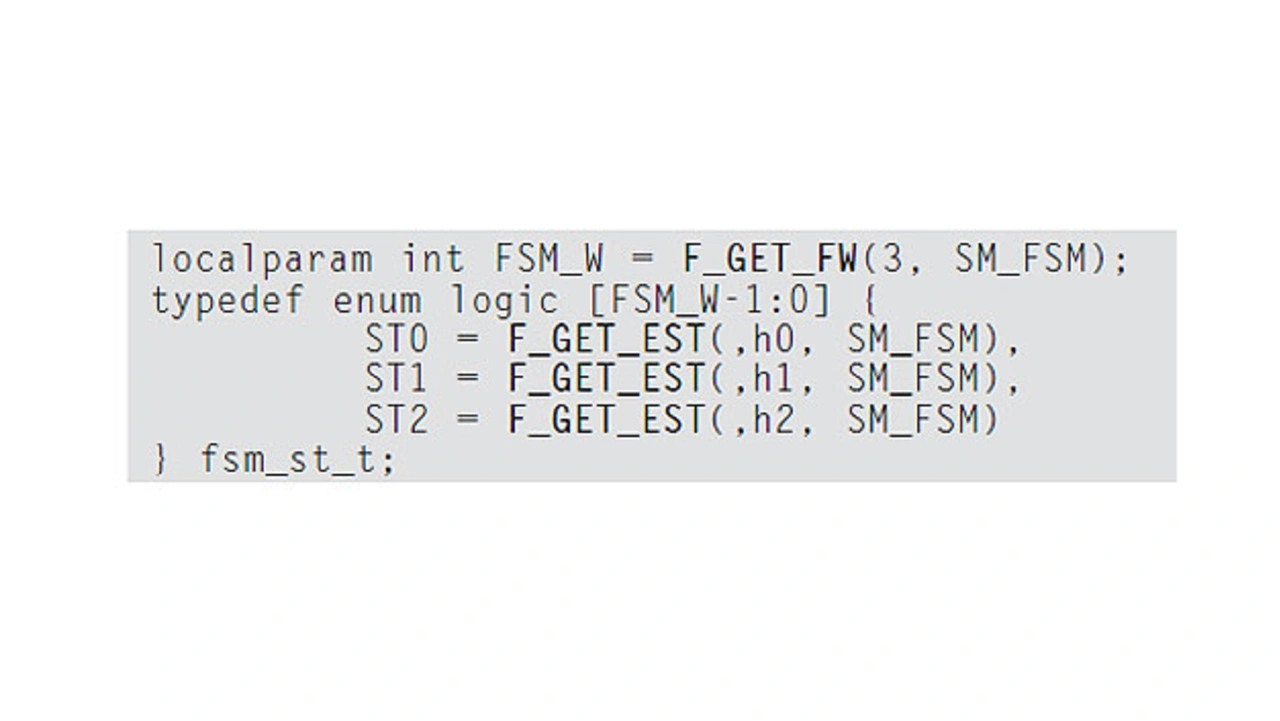

Generierung der FSM-Aufzählungswerte

Für die korrekte Generierung von Aufzählungswerten der FSM-Zustände werden die folgenden Funktions-Prototypenpaare eingeführt:

➔ F_GET_EST(int seq_num, logic [1:0] SM_FSM)

➔ F_GET_FW(int total_st, logic [1:0] SM_FSM)

SV-Codefragmente sind folgendermaßen dargestellt:

Der vorgeschlagene Ansatz für die FSM-Zustandsaufzählung lässt sich auch für Blöcke nutzen, die nicht FuSa-relevant sind, indem SM_FSM auf Null gesetzt wird.

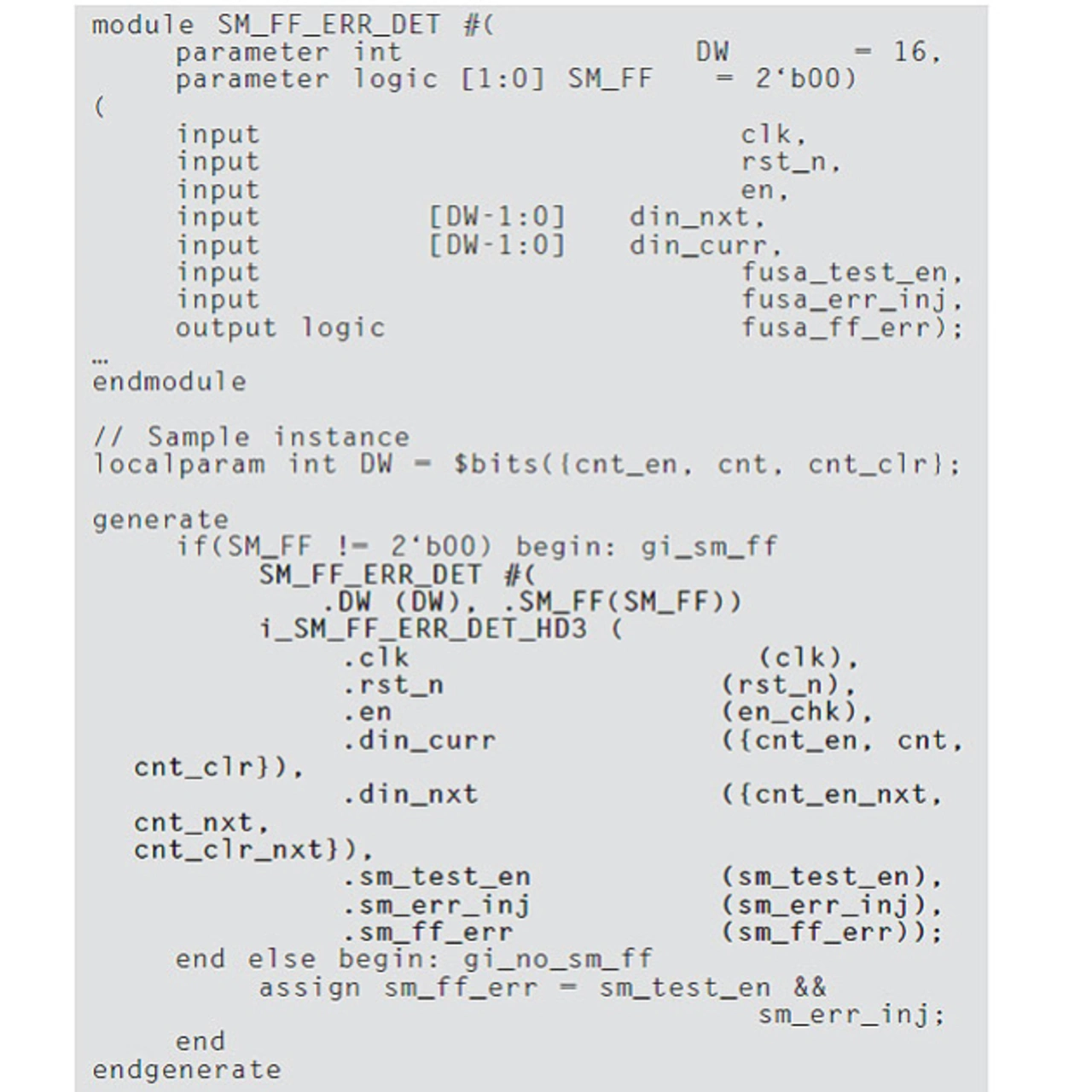

Register-Fehlererkennung

Um die Fehlererkennungslogik zu kapseln und zu trennen, wird ein dedizierter Block eingeführt, der in jedem sicherheitskritischen Block bedingt instanziiert werden muss. Aus struktureller Sicht sollten sequenzielle und kombinatorische Teile der Logik getrennt werden, das heißt in verschiedenen Blöcken in SV codiert werden. Die Portdefinition des Blocks wird nachfolgend gezeigt, ebenso wie das Beispiel einer bedingten Instanz. Mit dieser Art von Modul kann der Entwickler neue Signale basierend auf den Projektanforderungen hinzufügen bzw. entfernen und die Diagnoseabdeckung entsprechend ändern:

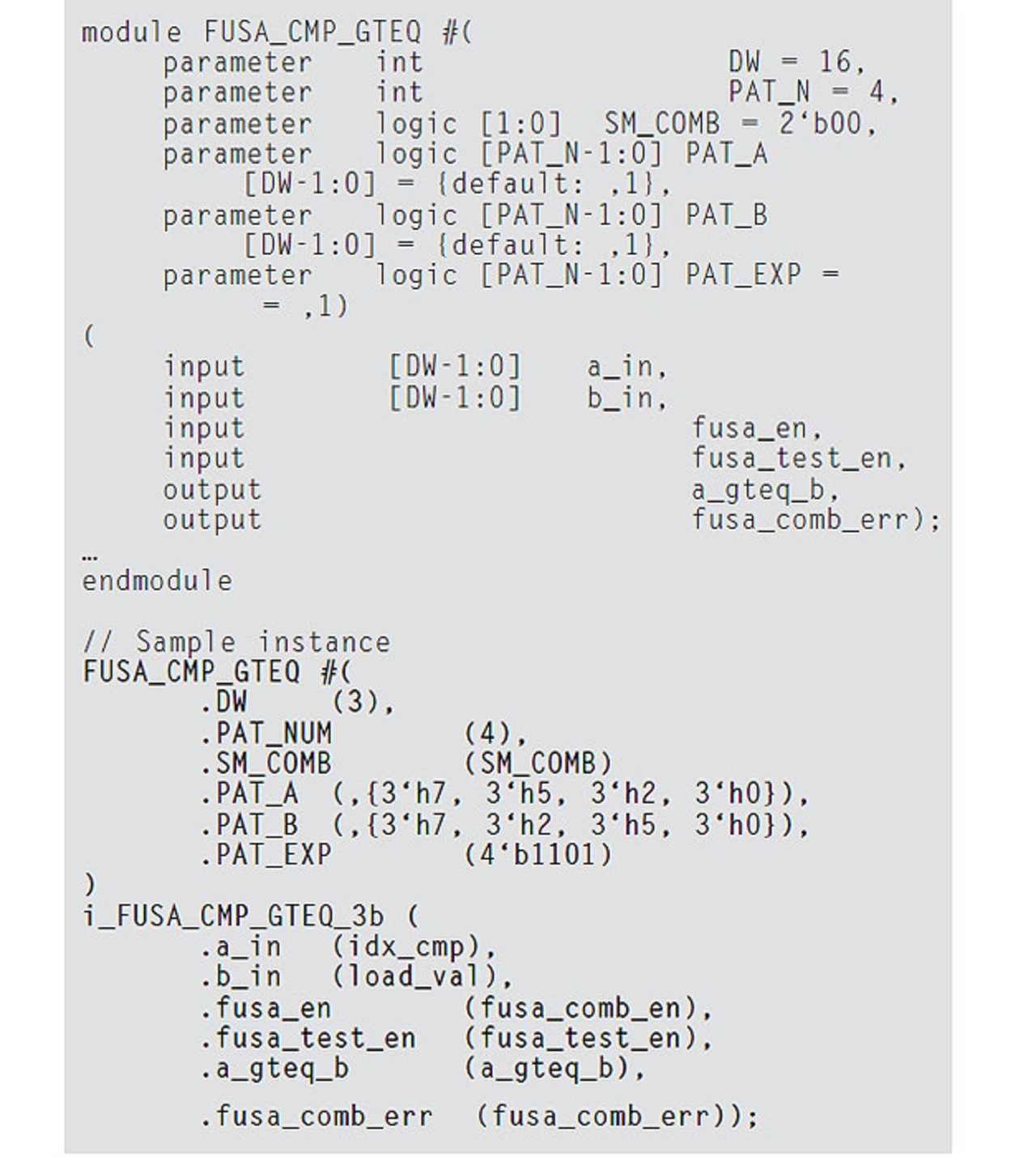

Kombinatorische logische Fehlererkennung

Es gibt einige Ansätze, die sich während der RTL-Implementierung umsetzen lassen.

Der erste Ansatz besteht darin, eigenständige Module für den Komparator, Addierer und Multiplexer zu haben, die alle erforderlichen Testlogiken, Muster und Vektoren implementieren. Für jedes dieser Module definiert der Entwickler auf Instanzebene die Anzahl der Muster, ihre Werte und Steuersignale, um die Diagnosefunktionen zu aktivieren/deaktivieren. Wie hier dargestellt gezeigt, sollte der gesamte FuSa-relevante Code im Zusammenhang mit dem Vergleich durch eine strukturelle Beschreibung ersetzt werden, die die Instanzen der folgenden Module verwendet:

Der andere Ansatz besteht darin, eine zentrale Steuereinheit mit vordefinierten Testvektoren für verschiedene Gruppen kombinatorischer Logik einzusetzen. Dieser Ansatz ist in Bezug auf die Fläche kosteneffizient, aber weniger flexibel. Er erfordert eine Anpassung der Erkennungslogik an die vorhandenen Muster.

- Digitale Sicherheitsmechanismen in kritischen Systemen

- Implementierung in RTL

- Ergebnisse der Methodik