Fachinterview Safety&Security

Verlässlichkeit auf Systemdesign-Basis

Fortsetzung des Artikels von Teil 4

IP-Schutz

D&E: Welche Methoden gibt es, um IP-Cores vor unlizenzierter Nutzung zu schützen?

DZ: Prinzipiell können wie im Multimedia-Bereich spezielle Wasserzeichen eingebracht werden. Allerdings entsteht hier ein Konflikt mit der funktionalen Sicherheit - die Gerätefunktion darf mit Wasserzeichen nicht beeinträchtigt werden.

Wasserzeichen die nicht in die Funktionalität eingebunden sind, werden allerdings leicht von den jeweiligen Entwurfswerkzeugen in der Optimierung entfernt, unabhängig von der jeweiligen Abstraktionsebene in der sie eingebracht wurden. Prinzipiell können Wasserzeichen auch in FPGAs, in freie Look-Up-Tabellen mit der Konfigurationsdatei hinterlegt werden.

Generell sind die Ansprüche an ein Wasserzeichenverfahren funktionale Korrektheit, angemessener Overhead, Transparenz aus Sicht der Entwurfswerkzeuge, Verifizierbarkeit, ein guter Beweis der Autorschaft und seine Robustheit.

Ein Grundsatzproblem: mit den Entwicklungswerkzeugen zur Optimierung wird auch häufig ein Weg zur Entfernung aufgezeigt. Eine Möglichkeit zur Erkennung einer Kopie für FPGA-Cores liegt prinzipiell im Vergleich der Inhalte der Look-Up-Tabellen von Original und unlizenzierter Kopie: je größer die Übereinstimmung, desto wahrscheinlicher ein Urheberrechtsverstoß. Es gibt allerdings auch den seltenen Fall, dass benachbarte IP-Cores funktionsäquivalente LUTs tragen und daher diese in der Synthese optimiert werden. Das muss eine etwaige Auswertefunktion berücksichtigen [3].

Jobangebote+ passend zum Thema

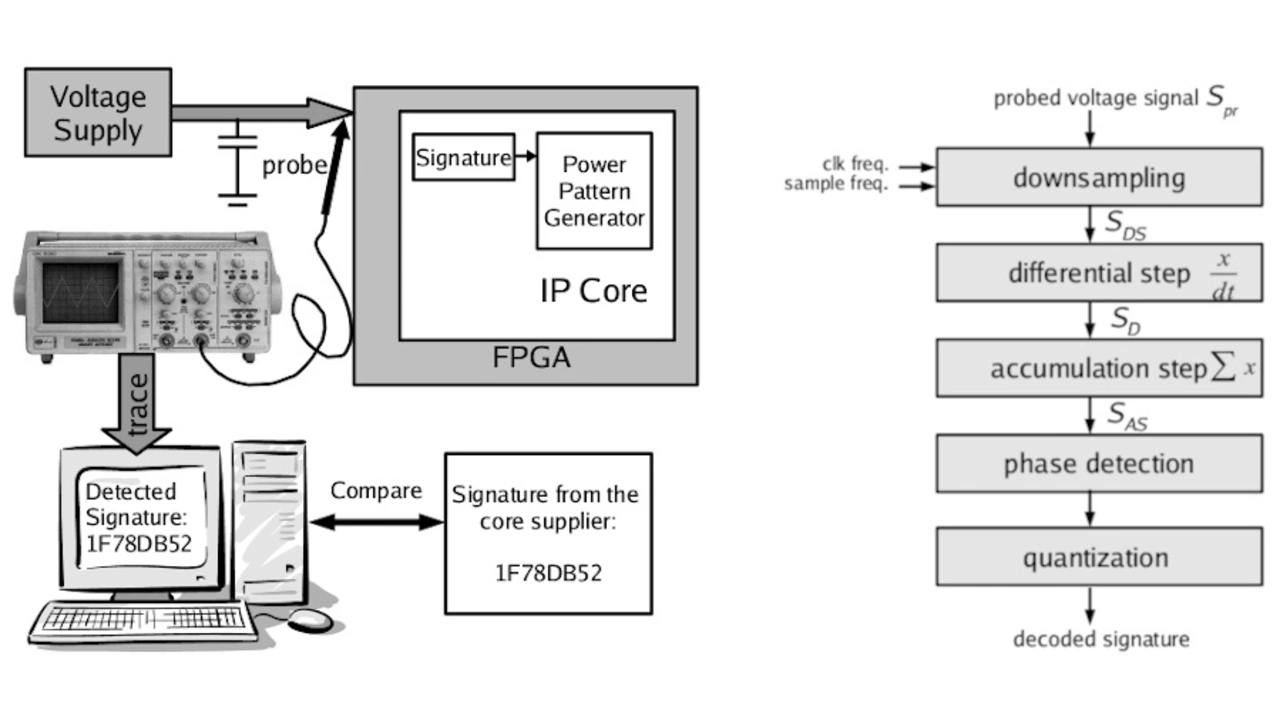

Eine weitere Verifikationsmöglichkeit ist das Auslesen eines Wasserzeichens an der Versorgungsspannung: hier wird im IP-Core eine Signatur hinterlegt, die der Eingang für einen Signalgenerator ist (Bild 5). Allerdings muss das SNR dann hoch genug sein, um den intrinsischen Abdruck des FPGA-Systems zu überragen. In der Regel ist die Signatur eine Binärfolge und kann durch Signalverarbeitung des elektrischen Signales zurückgewonnen werden. Generell kann auch Verschlüsselung Abhilfe schaffen, die Entschlüsselung erfolgt dann im Entwurfswerkzeug oder direkt auf dem FPGA.

Allerdings verliert man mit der Verschlüsselung eines HDL-Codes oder einer Netzliste die Anpassungsmöglichkeit. Die Nachteile von IP-Core Verschlüsselung sind die längere Simulationszeit, unzureichende Verhaltensmodelle, Einschränkungen in der Werkzeugkette sowie eingeschränkte Debug-Möglichkeiten. (ct)

- Herr Dr. Ziener, vielen Dank für das Gespräch und Ihre Zeit!

Referenzen

[1] Algirdas Avižienis, Jean-Claude Laprie, and Brian Randell. Fundamental concepts of dependability. Technical Report Series – University of Newcastle upon Tyne Computing Science, 2001.

[2] Pankaj Jalote. Fault Tolerance in Distributed Systems. Prentice-Hall, Inc., Upper Saddle River, NJ, USA, 1994.

[3] Daniel Ziener, Stefan Aßmus, and Jürgen Teich. Identifying FPGA IP-Cores based on Lookup Table Content Analysis. In Proceedings of 16th International Conference on Field Programmable Logic and Applications (FPL 2006), pages 481–486, Madrid, Spain, August 2006.

| Dr.-Ing. habil. Daniel Ziener |

|---|

wirkt am Lehrstuhl »Computer Architecture for Embedded Systems« an der Universität Twente. Seine Forschungsgebiete umfassen die partielle dynamische FPGA-Rekonfiguration, effizienter Einsatz von FPGA-Strukturen, Entwurf von IP zur Signalverarbeitung, verlässliche und fault-resiliente Embedded-Systeme sowie Security in FPGA-basierten Systemen. |

- Verlässlichkeit auf Systemdesign-Basis

- Anforderung an alle Systemebenen

- Angriffskategorien

- Kontrollflussmethoden

- IP-Schutz