Design&Verifikation

Chipdesign als Big-Data-Herausforderung

Fortsetzung des Artikels von Teil 2

Anwendungen I

Im Folgenden werden die oben benannten Prinzipien an praktischen Beispielen und Anwendungen vorgestellt.

Beispiel 1 - FIFO-Testbench

Das folgende Beispiel zeigt, wie Cogita unter Verwendung der Datenvisualisierung eines FIFO-Unterlaufs, die Ursache eines Testbench-Bugs aufdeckt. In diesem Fall weist die Fehlermeldung selbst nicht auf den FIFO-Unterlauf hin. Stattdessen wäre ein langer Debug-Prozess zur Aufdeckung notwendig. Cogitas adaptives Visualisierungsschema zeigt die Ursache des Problems sofort an.

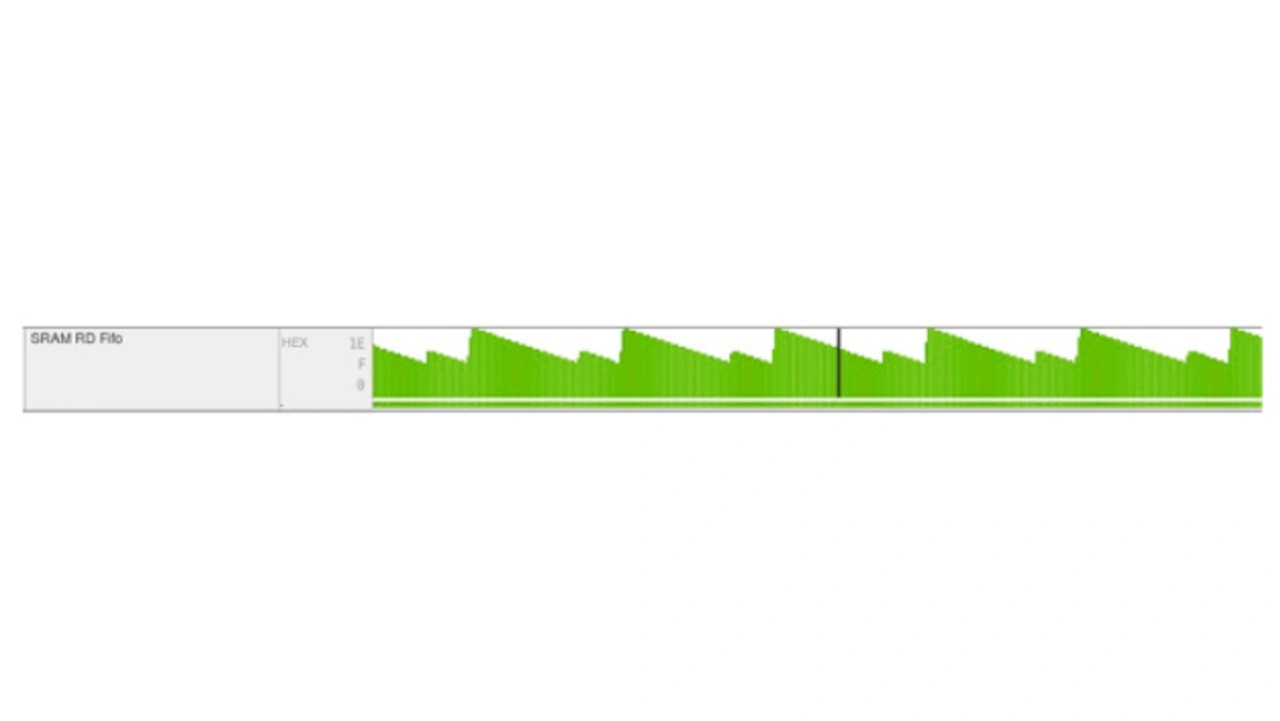

Bild 1 stellt eine FIFO-Ebenen-Modellierung der Testbench, über ein bestandenes Testszenario, dar. Die Y-Achse repräsentiert den FIFO-Pegel, je höher der Balken, desto voller ist der FIFO. Die X-Achse stellt die Simulationszeit dar. Dieses Diagramm verdeutlicht sofort, dass der FIFO niemals völlig leer läuft, hat er den Schwellenwert (in diesem Fall 0xF) erreicht, kann geschrieben werden. Die Schwellenwerte sind deutlich sichtbar.

Jobangebote+ passend zum Thema

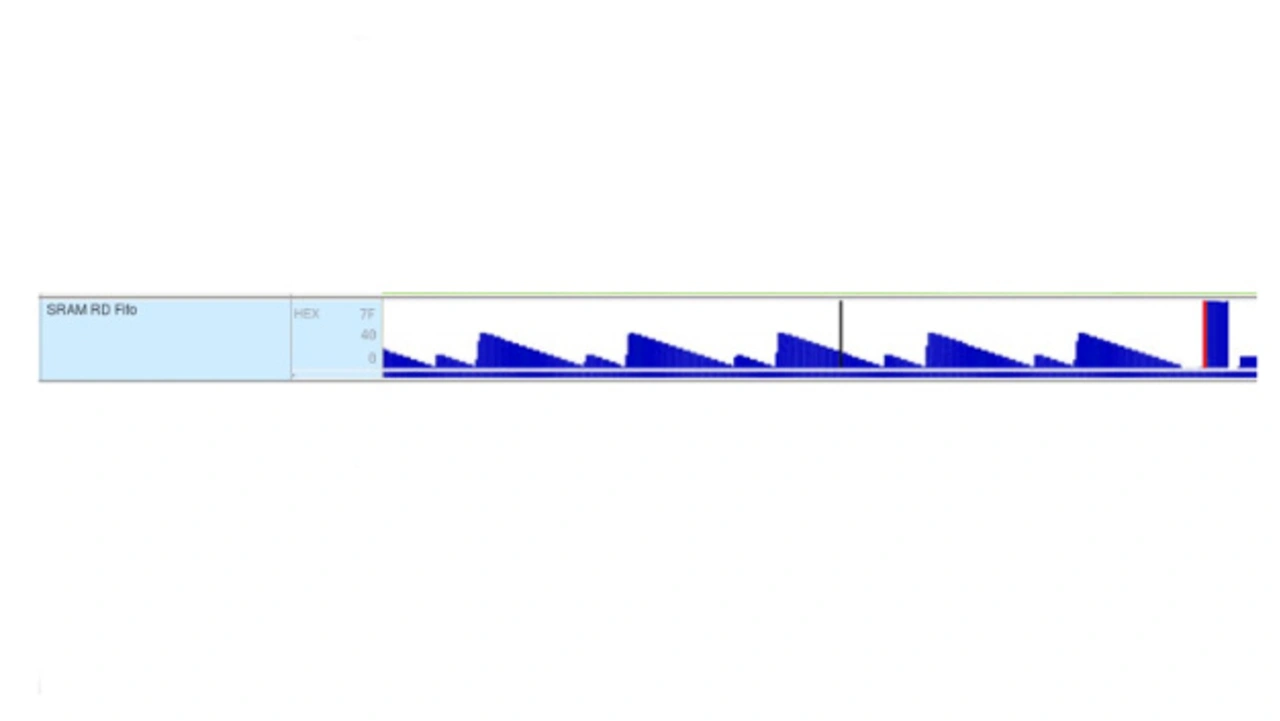

Bild 2 stellt ein Fehlerszenario dar, bei denen der FIFO an der Schwelle nicht gefüllt wird und somit unterläuft (bewirkt Wrap Around). Das signalisiert die rote Fehlerleiste. Im Vergleich beider Darstellungen wird das eigentliche Problem erkannt, mit Lesen der Logdatei wäre es unlängst schwieriger.

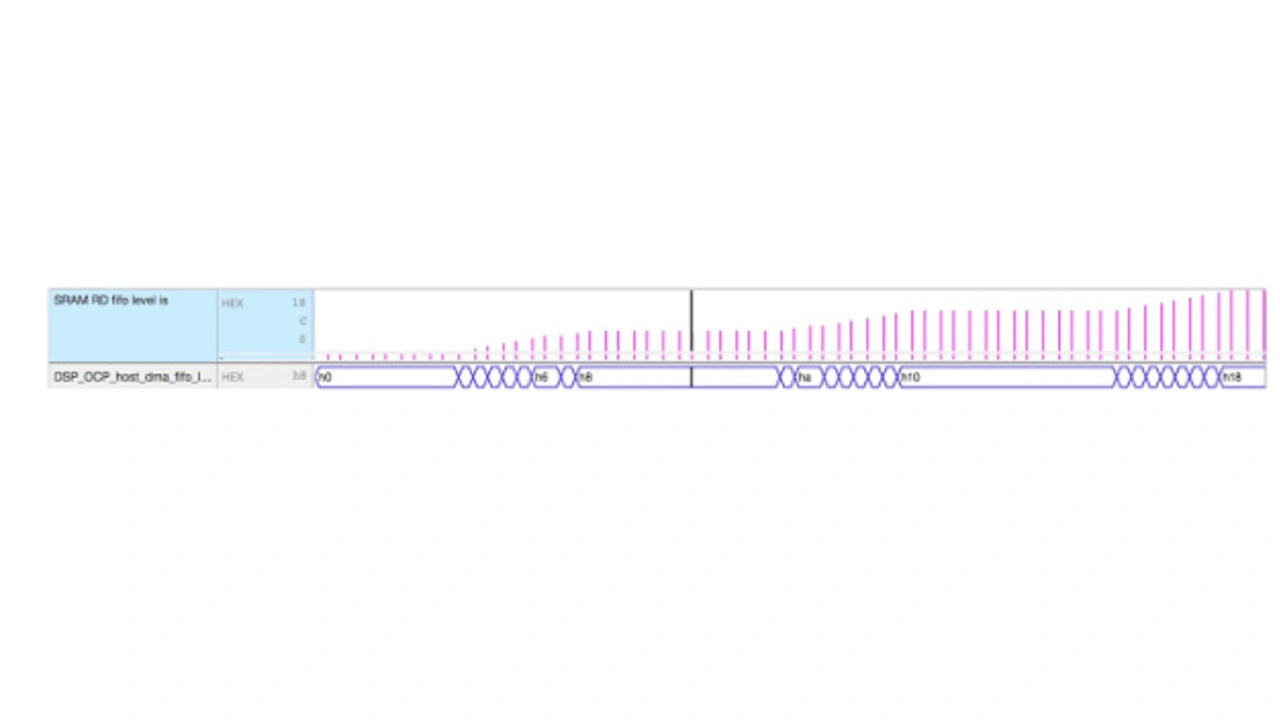

In Cogita kann die Datendarstellung (Bild 3) in verschiedenen Formen erfolgen, unabhängig davon, ob ein RTL-Signal oder eine Prüfstandsvariable verfolgt wird. Beide Ansichten ergänzen sich gegenseitig und schaffen ein einheitliches Verständnis des Systemverhaltens.

Beispiel 2 - Debugging mit Datenbankwerten

Der Prüfstand konfiguriert den DMA am Prüfling und injiziert dann Daten in den FIFO. Dabei soll der Prüfling DMA-Transaktionen für den internen DRAM generieren. Der Prüfling erzeugt eine konfigurationsgemäße DMA-Adresse, die Adressen sind über die Prüflingsschnittstelle nicht sichtbar. Sie können also nicht mit der Wellenformen verfolgt werden. Der Test schlägt bei einem FIFO-Überlauf fehl. Zur Ursachenanalyse sind mehrere Wellenformen und Protokolle auszuwerten.

Cogita ermöglicht einen wesentlich kürzeren Debug-Prozess, bei dem keine Gefahr besteht, sich mit irrelevanten Ereignissen aufzuhalten:

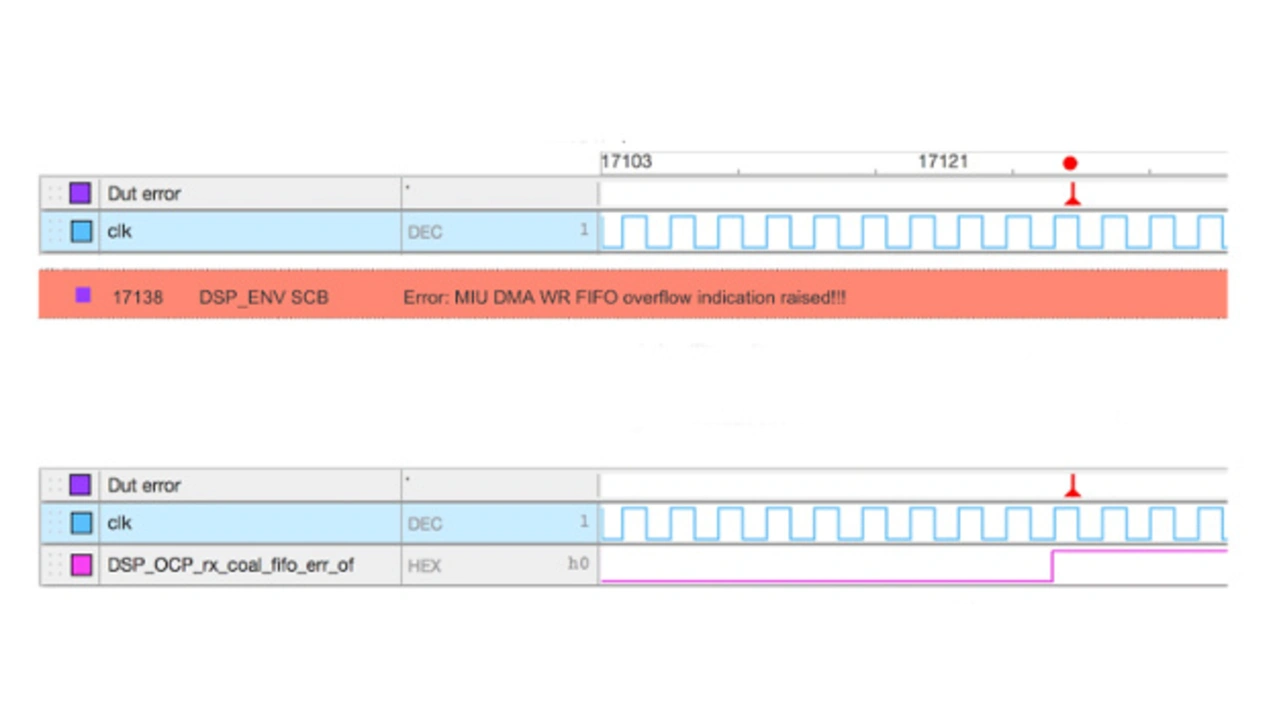

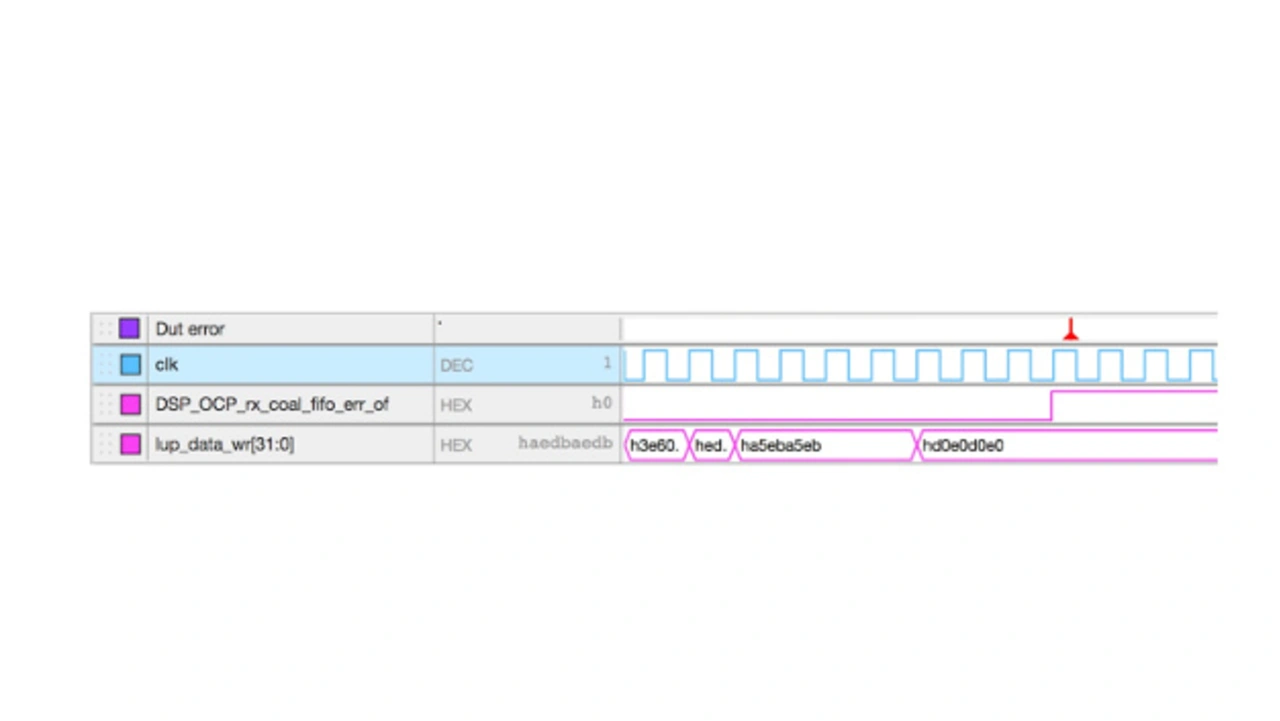

Lesen der Fehlermeldung im Protokoll: "FIFO-Überlauf" (Bild 4, oben)

Überprüfung des zusammenhängenden Berichts, mit Laden des aktuellen RTL FIFO-Überlaufanzeige-Bits (Bild 4, unten)

Ein Problem mit den generierten DMA-Adressen wird vermutet.

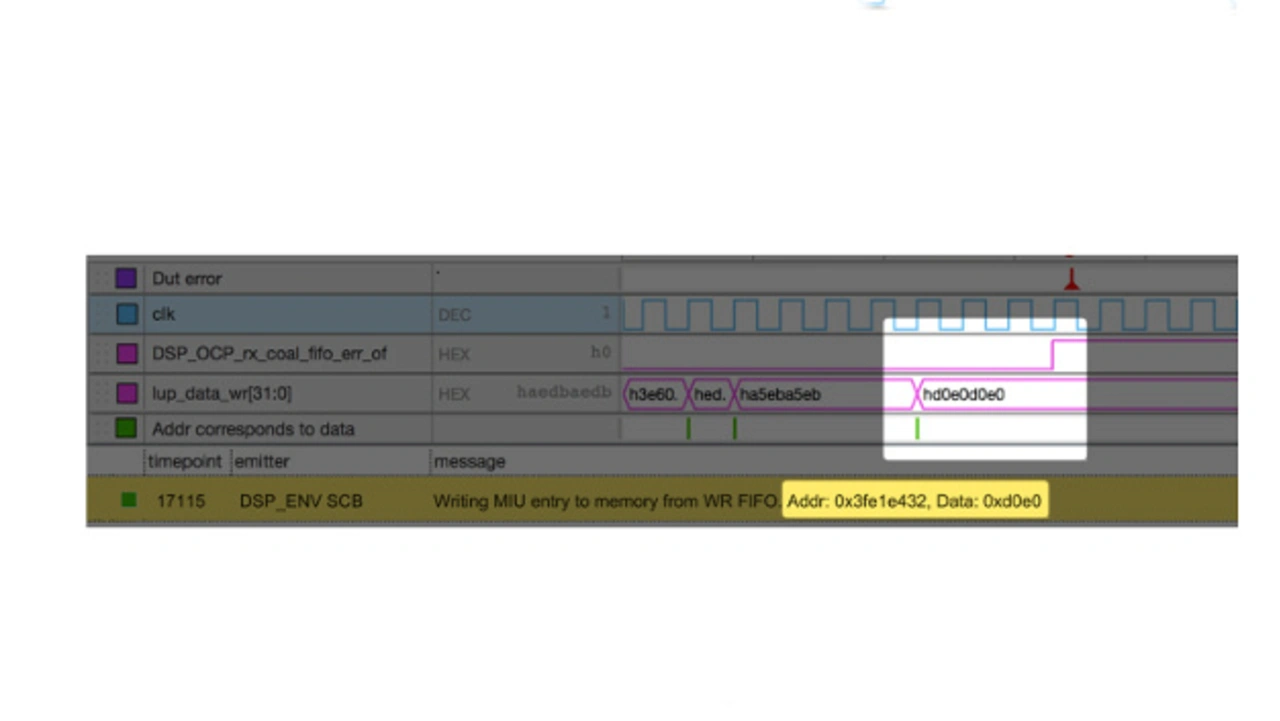

Damit werden die eingegebenen FIFO-Daten auf RTL geprüft, um eine Korrelation mit der erzeugten DMA-Adresse auszumachen (Bild 5)Das Datum (Bit 15:0) trägt den Wert 0xD0E0.

Cogita stellt fest, dass die zugehörige Adresse 0x3FE1_E432 in den Protokollnachrichten fest. Die Nachricht wird von Cogita mit dem genauen Zeitpunkt, synchron zu den Wellenformen angezeigt (Bild 6)Die genaue Ursache wird erkannt: die Adresse endet auf 0x2, während der DMA nur 64-Bit-Adressen erzeugen darf.

Beispiel 3 - Mustererkennung

Wie jede generische Maschine arbeitet ein Chip mit wiederholenden Sequenzmustern. Ein Muster kann Kommunikationspakete beinhalten, die der Prüfstand in den Prüfling einspeist, Bustransaktionen, FIFO-Abläufe oder jedes andere Szenario. Ein gemeinsamer Fehler wird als eine Sequenz identifiziert, die vom Restmuster abweicht. Die Analyse einer gültigen Sequenz und der Vergleich mit einer fehlerhaften Sequenz ist eine grundlegende Debug-Technik, aber oftmals schwierig umzusetzen.

Durch die Verwendung von Tagging- und Suffix-Baummanipulationen [2] im Log erkennt Cogita automatisch Wiederholungsmuster, die zu einer fehlerhaften Nachricht gehören. In einigen Fällen muss der Ingenieur möglicherweise grundlegende Informationen bereitstellen, um die Strukturierung der relevanten Muster zu unterstützen, wie z.B. einen Startpunkt, Signallänge und Endpunkt. In anderen Fällen übernimmt Cogita dies vollautomatisch.

Als Beispiel stellen die folgenden Schritte ein geeignetes Muster des DMA-Zugriffs dar:

- Schreiben in DMA-Konfigurationsregister (base_address, Anzahl der Blöcke, Schreiben pro Block)

- Schreiben von DMA_on_bit

- Daten in FIFO einspeisen (DMA erzeugt Adressen und Speicherzugriff)

- Bis zu 1000 Zyklen Wartezeit

- Das Interruptbit wird vom Prüfling gesetzt

Der Test führt 100 solcher Muster aus. In drei Fällen wird aufgrund eines Testbench-Bugs eine nicht ausgerichtete Basisadresse konfiguriert, so wird die DMA-Transaktion gestoppt und der Interrupt nicht gesetzt. Da der erwartete Interrupt ausblieb, wurde ein Fehler ausgelöst. Die Grundursache ist eine falsche Konfiguration der Basisadresse, der Verifikationsingenieur müsste hier schrittweise bis zur Aufdeckung untersuchen. Cogita erkennt das Muster automatisiert, da alle fehlgeschlagenen Transaktionen eine nicht-zugeordnete Basisadresse kennzeichnen.

Cogita analysiert die Protokolldatei und identifiziert eine Reihe von Meldungen als wiederholte Transaktion. Diese wird den Ingenieuren vorgelegt, um sie als gültiges Muster zu kennzeichnen:

- emitter = [AXI_WR]; message = DMA CFG config REG: BASE_ADDR, Data: 0x????????

- emitter = [AXI_WR]; message = CFG DMA config REG: WR_PER_BLK, Data: 0x????????

- emitter = [AXI_WR]; message = CFG DMA config REG: NUM_BLKS, Data: 0x????????

- emitter = [AXI_WR]; message = CFG DMA config REG: DMA_ON, Data: 0x1

- emitter = [INT_MON]; message = DUT interrupt bit set = TRUE

Die Muster werden dann, zum effektiven und sofortigen Testverständnis, auf einer Zeitachse dargestellt. Die Prüfingenieure können daraus schnell erkennen, wie viele Sequenzen erfolgreich abgeschlossen wurden, welche sie parallel laufen, wie lange sie dauern, und weiteres.

Im konkreten Beispiel erkennt Cogita 97 solcher Muster und identifiziert weitere drei ungültige Muster, in denen die Meldung #5 fehlt.

Ein gültiges Musterbeispiel (mit spezifischer Basisadresskonfiguration):

- emitter = [AXI_WR]; message = DMA CFG config REG: BASE_ADDR, Data: 0xABCD_1230

- emitter = [AXI_WR]; message = CFG DMA config REG: WR_PER_BLK, Data: 0x10

- emitter = [AXI_WR]; message = CFG DMA config REG: NUM_BLKS, Data: 0x3

- emitter = [AXI_WR]; message = CFG DMA config REG: DMA_ON, Data: 0x1

- emitter = [INT_MON]; message = DUT interrupt bit set = TRUE

Ein ungültiges Musterbeispiel (mit spezifischer Basisadresskonfiguration):

- emitter = [AXI_WR]; message = DMA CFG config REG: BASE_ADDR, Data: 0xABCD_123F

- emitter = [AXI_WR]; message = CFG DMA config REG: WR_PER_BLK, Data: 0x10

- emitter = [AXI_WR]; message = CFG DMA config REG: NUM_BLKS, Data: 0x3

- emitter = [AXI_WR]; message = CFG DMA config REG: DMA_ON, Data: 0x1

- MISSING

Cogita berichtet dem Benutzer, dass alle 97 gültigen Muster base_addr[1:0] == 0 teilen und alle ungültigen Muster davon abweichen. Gemäß der Spezifikation muss BASE_ADDR 64-Bit-konform sein und dies zeigt ein Konfigurationsproblem (Testbench) an. Ein langwieriger Debug-Prozess wird vermieden.

Durch die Definition eines Sequenzschwellenwerts kann Cogita Sequenzen mit hoher Ähnlichkeit anhand des definierten Musters hervorheben. Die Sequenzen werden dann zum Vergleich der Abweichung vom erwarteten Muster angezeigt und die Fehler sofort erkannt.

Durch das Erstellen eines Datensatzes aus der Reihenfolge der Einzelbilder, können Clustering-Algorithmen verwendet werden (z.B. K-means) [2], um die Ähnlichkeit zwischen mehreren fehlerhaften Mustern zu identifizieren, so wie nicht ausgerichtete Adressen, zusätzliche Taktzyklen oder andere schwer zu erkennende Abweichungen.