Fünf ungewöhnliche Anwendungen für Datenerfassungsgeräte

FPGAs revolutionieren die Messdatenerfassung

Fortsetzung des Artikels von Teil 2

Benutzerspezifische digitale Kommunikationsprotokolle / Anwendung Harris RF Communications

Viele Anwendungen erfordern eine Schnittstelle zu Geräten, die seltene oder proprietäre digitale Kommunikationsprotokolle verwenden. Oft ist die spezielle Hardware, die für solche Anwendungen nötig ist, entweder nicht verfügbar oder exorbitant teuer. In anderen Fällen arbeiten Anwender, um Systemkosten und -komplexität zu reduzieren, lieber mit nur einer physikalischen Schnittstelle, die mit einer Vielzahl von Protokollen kommunizieren kann. Hardware der R-Serie eignet sich hervorragend für solche Anwendungen. So können etwa Protokollkodierung und -dekodierung an den FPGA abgegeben werden. Dadurch entstehen vollständig anpassbare Bitstreams und die Prozessorauslastung der Host-CPU sinkt. Zudem profitieren Anwender von einfacheren Host-Programmen, die direkt mit Daten statt mit Low-Level-Protokollsignalen arbeiten. Weil ein FPGA inhärent parallel und in Software definiert ist, kann er verschiedene Gerätecharakteristika annehmen und als flexible Schnittstelle für praktisch jedes Kommunikationsprotokoll dienen, darunter I2C und SPI oder anwenderdefinierte digitale Protokolle. Zudem ermöglicht die R-Serie auch die Kommunikation mit Geräten, die eine Antwort auf bestimmte Signale innerhalb eines festgelegten Zeitraums erfordern. Die geringe Latenz und die Funktionen zur Entscheidungsfindung des FPGAs erlauben es, diese Art der Anforderungen mit integrierter Datenverarbeitung zu erfüllen, ohne dabei Daten an den Prozessor und zurück übertragen zu müssen.

Aus der Praxis

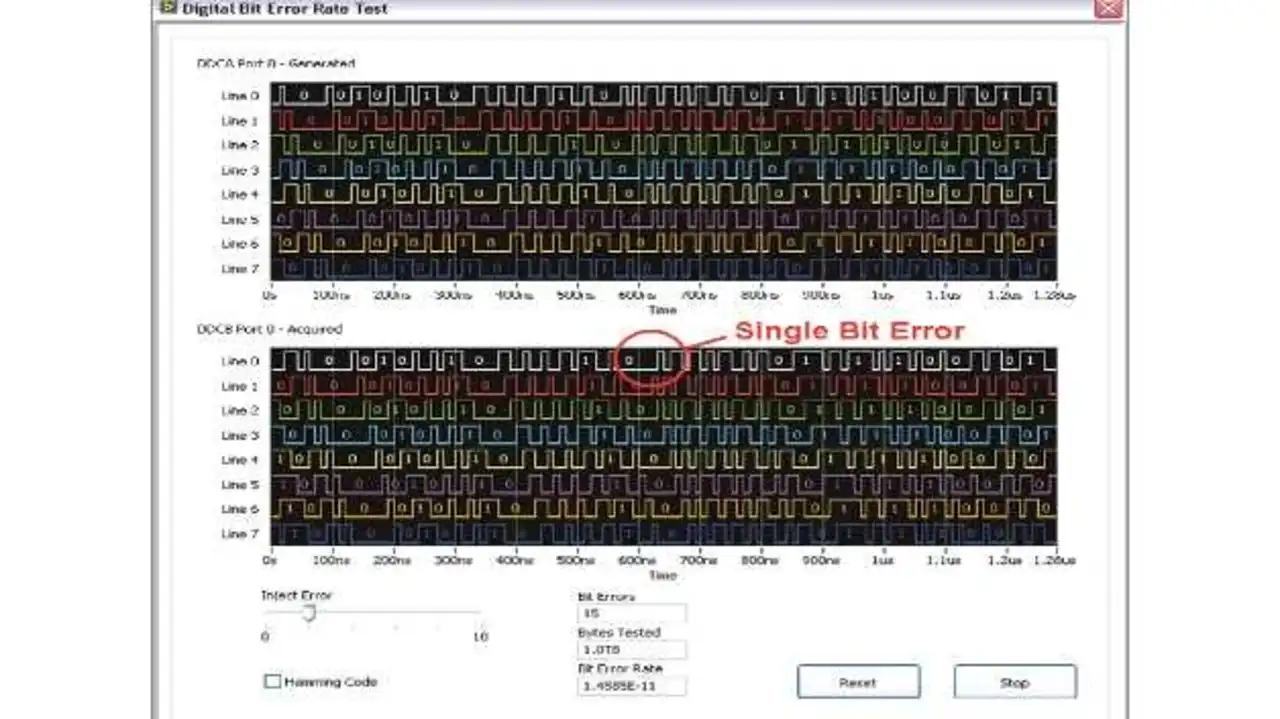

Harris RF Communications musste seine Stand-alone-Messgeräte ersetzen, um neue und moderne Produkte testen zu können. Die RF-Produkte, die am häufigsten geprüft werden sollten, waren ein Datensender und ein Datenempfänger mit drei verschiedenen seriellen Schnittstellen, die validiert werden mussten. Das ältere System unterstützte nur eine begrenzte Zahl von Kommunikationsarten, so dass man eine neue, flexible und skalierbare Lösung finden musste. Mithilfe eines Geräts der R-Serie und LabVIEW FPGA wurde ein komplettes Prüfsystem für serielle Tests der Bitfehlerraten implementiert. Bei den zu validierenden physikalischen Schnittstellen handelte es sich um RS232, RS422 und RS485. Die beiden letzten sind symmetrische Schnittstellen für Hochgeschwindigkeitsanwendungen bis zu 1,6 Mbit/s. Um serielle Daten mit 1,6 Mbit/s verarbeiten zu können, musste die Anwendung mit einer FPGA-Taktrate von 80 MHz laufen. Die Daten mussten außerdem mit einer Auflösung von maximal 20 ns verarbeitet werden, und das neue System bot eine garantierte Verarbeitungszeit von 12,5 ns pro Bit. All das wäre mit klassischen Datenerfassungsgeräten nicht möglich gewesen. Das Resultat war eine drastische Kostenreduzierung pro Prüfling.

Jobangebote+ passend zum Thema

- FPGAs revolutionieren die Messdatenerfassung

- Benutzerdefiniertes Timing und Triggern / Anwendung OptiMedica

- Benutzerspezifische digitale Kommunikationsprotokolle / Anwendung Harris RF Communications

- Integrierte Signalverarbeitung / Anwendung Cal-Bay Systems

- Präzises Timing und hohe Zuverlässigkeit für kritische Aufgaben / Anwendung MicroNova