Sicherheit für Cortex-M-Prozessoren

Viele vertrauenswürdige Zonen

Fortsetzung des Artikels von Teil 1

Die Umsetzung der TEE mit mehreren Zonen

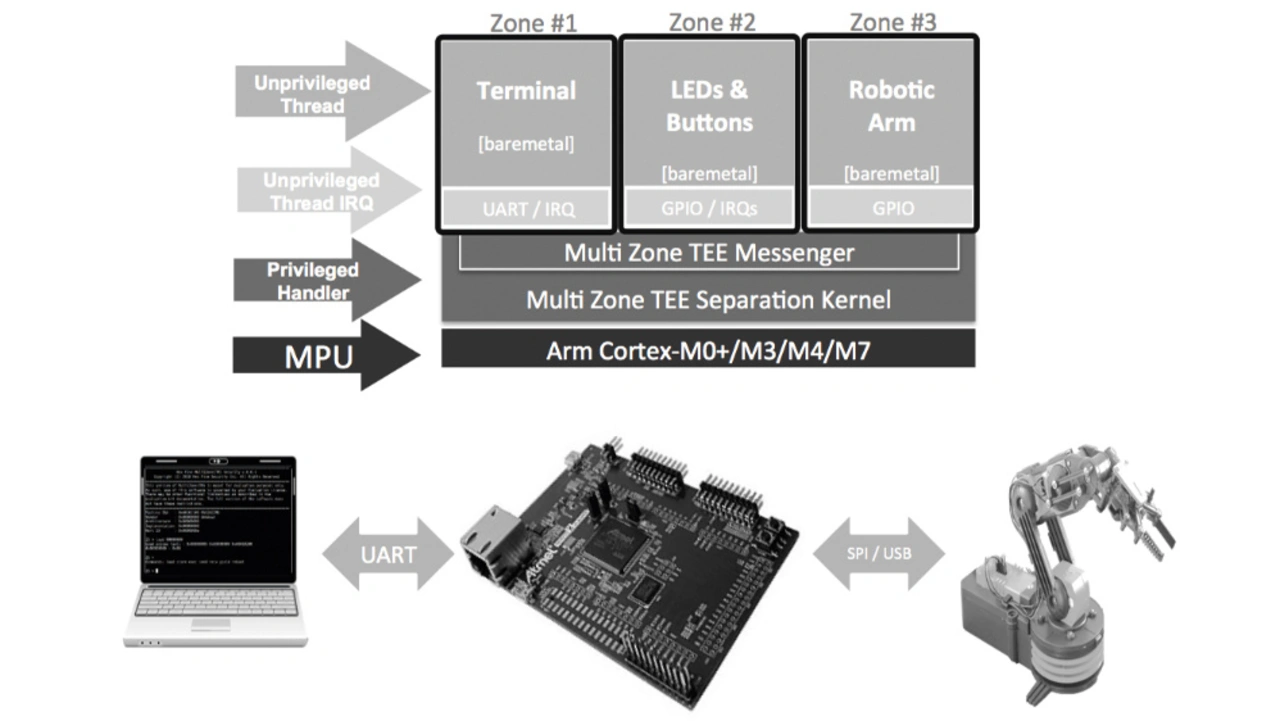

Die vorgeschlagene neue Systemarchitektur basiert auf einem „leichten“ Separation-Kernel, der auf der höchsten Privilegienebene (Privileged Handler Mode) läuft, und auf Anwendungscode- und Interrupt-Handlern, die in getrennten Zonen auf der niedrigsten Privilegienebene (Unprivileged Thread Mode) laufen. Die resultierende TEE besteht aus den folgenden Komponenten.

TEE-Konfigurator

Um die Möglichkeit menschlicher Fehler zu begrenzen, kapselt ein Konfigurator-Dienstprogramm die Komplexität der Verwaltung der zugrunde liegenden Hardware-Sicherheitsblöcke und verbirgt sie. Die einzige Interaktion des Systementwicklers mit der TEE ist eine einfache, flache Format-Policy-Definitionsdatei. Es ist keine Codierung, Kompilierung, Verknüpfung und Fehlersuche erforderlich – und sogar erlaubt. Stattdessen wird ein Befehlszeilen-Dienstprogramm als Toolchain-Erweiterung zur Verfügung gestellt. Das Konfigurator-Dienstprogramm kombiniert die vollständig verknüpften Binärdateien jeder Zone mit der vorgefertigten TEE-Laufzeit, wendet die in der Konfigurationsdatei definierten Sicherheits- und Trennungsrichtlinien an und erzeugt das sichere Boot-Firmware-Image für den Ziel-Upload. Darüber hinaus bietet der Konfigurator

- Eine binäre Übersetzung, um die in Abschnitt Systembeschränkungen zu beheben

- Volle Unterstützung für trap-and-emulate, ohne den vorhandenen Quellcode zu modifizieren

- Einen ausgeklügelten MPU-Optimierungsalgorithmus, der jeden benutzerdefinierten Bereich und jede beliebige Größe der im Speicher abgebildeten Ressourcen ermöglicht

TEE-Separation-Kernel

Zur Laufzeit bietet ein leichter Separation-Kernel eine formal überprüfbare, in sich geschlossene Möglichkeit zur zeitlichen und räumlichen Isolierung mehrerer isolierter Threads. Der Kernel unterstützt eine unbegrenzte Anzahl von getrennten TEEs, die als Zonen bezeichnet werden. Über die Richtliniendefinitionsdatei weist der Systementwickler jeder Zone einen Satz von Ressourcen zu.

Dazu gehören alle im Speicher abgebildeten Ressourcen wie RAM, ROM, E/A, Unterbrechungen und relative Lese-/Schreib-/Ausführungs-Zugriffe. Der TEE-Kernel implementiert einen präemptiven Echtzeit-Scheduler, der für sicherheitskritische Anwendungen mit konfigurierbaren Round-Robin- und/oder kooperativen Scheduling-Richtlinien geeignet ist. Der Kernel bietet auch unabhängige Software-Timer für jede Zone, die mit dem Armv7-M-System-Timer – auch bekannt als SysTick – übereinstimmen.

Es gibt eine vollständige Unterstützung für vektorielle Interrupts mit niedriger Latenz (NVIC, Nested Vector Interrupt Control) und den Wait for Interrupt (WFI). Ein einzigartiger Sicherheitsaspekt des Multizonen-TEE ist die Fähigkeit, Interrupt-Handler im unprivilegierten Thread-Modus im Kontext der abgebildeten Zone sicher auszuführen.

Um eine vollständige und transparente Unterstützung für unmodifizierte Binärdateien zu bieten, sind im Kernel die Funktionen für trap-and-emulate für die meisten privilegierten Systemregister zugänglich – einschließlich derjenigen, die über privilegierte MRS- und MSR-Befehle, z.B. MSP, BASEPRI, zugänglich sind, und derjenigen, die im Speicher abgebildet werden, z.B. VTOR, ICSR, CFSR in der SCS-Region.

TEE Messenger

Die TEE stellt eine eigenständige Einrichtung für die sichere Kommunikation zwischen den Zonen dar. Sie ermöglicht es den Zonen, sichere Nachrichten – geschützte Byte-Ströme – auf einer nicht gemeinsam genutzten Speicherbasis auszutauschen. Die TEE-Programmierschnittstelle (API, Application Programming Interface) bietet zwei Systemaufrufe zum Senden und Empfangen von Nachrichten – ECALL_SEND und ECALL_RECV.

TEE Secure Boot

Mit dem zweistufigen sicheren Bootloader, der in der TEE implementiert ist, lassen sich die Integrität und Authentizität des Firmware-Images (SHA-256) überprüfen und der Laufzeit-Speicherbedarf sowie die Angriffsfläche des Ziels minimieren.

TEE-API

Trap-and-emulate ist unerlässlich, um die Wiederverwendung von Software zu gewährleisten und um Fehler, Entwicklungskosten und die Zeit bis zur Markteinführung zu reduzieren – da es keine Änderungen an bestehender Software erfordert. Diese Technik kann jedoch einen leichten Einfluss auf den Durchsatz und die Unterbrechungslatenz haben. Zur Optimierung von Durchsatz und Latenzzeit steht eine vollständig optionale API zur Verfügung, um privilegierte Anweisungen in funktional äquivalente TEE-Aufrufe zu verpacken. Die API wird in Form iner C-Header-Datei zur Verfügung gestellt und besteht aus einem kleinen und effizienten Assembler-Code – ohne Bibliotheks- oder Stack-Overhead.

Jobangebote+ passend zum Thema

Test des Konzepts und Benchmark

Die als Referenz genommene Anwendung steuert die Bewegungen eines kleinen Roboterarms von einer lokalen Terminalkonsole aus. Sie umfasst einen Satz integrierter Bare-Metal-Befehle zum Testen der Sicherheit und Trennung des Systems sowie zur Messung des Leistungsbedarfs für die Verwaltung und der Interrupt-Latenz (Bild 2).

Zone #1 wird über den seriellen Anschluss (UART) mit einem PC-Terminal verbunden, um die Zuordnung von Peripheriegeräten, sichere Treiber, die Durchsetzung von Isolationsrichtlinien, Leistungsstatistiken, Software- Timer und die Kommunikation zwischen den Zonen zu demonstrieren. Zone #2 lässt eine LED blinken und ist über eine Schnittstelle mit Tasten verbunden, um die sichere Handhabung von Interrupts auf Benutzerebene und die sichere Nachrichtenübermittlung zu demonstrieren. Zone #3 bedient den über GPIO angeschlossenen Roboterarm. Befehle werden von Zone #1 empfangen und der Status des Roboters über sichere Nachrichtenübermittlung zurück gemeldet.

Die Leistung der Multizonen-TEE wurde auf einem Entwicklungsmodul von Microchip gemessen (Bild 2). Das Modul (SAM E70 Xplained Evaluation Kit) ist mit einem Cortex-M7-Prozessor (ATSAME70Q21) ausgestattet, der mit 240 MHz getaktet wird. Zusätzlich zu den umfangreichen Tests für Sicherheit, Trennung und Zuverlässigkeit, die über Zone #1 zugänglich sind, wurde die Größe und die Leistung der TCB gemessen:

TCB-Größe

Um die Angriffsfläche zu minimieren und eine formale Verifikation zu ermöglichen, wurde die Multizonenlaufzeitumgebung vollständig in Assembler geschrieben. Sie ist in sich geschlossen, ohne Abhängigkeiten von Compiler- Bibliotheken – typisch für in C geschriebene Software auf Systemebene. Die TCB des Systems umfasst eine Gesamtmenge von ca. 2 KB.

Mindestens eine Größenordnung kleiner als jede in der öffentlich zugänglichen Literatur dokumentierte Software auf Systemebene. Auf der Grundlage der nachgewiesenen Korrelation zwischen der TCB und der Anzahl der Defekte können wir schließen, dass die vorgeschlagene TEE mindestens zehnmal weniger anfällig für Schwachstellen ist – oder etwa zehnmal »sicherer«.

Aufwand für die Verwaltung

Um den Leistungsaufwand zu bewerten, wurde die Zeit für den Zonenkontextwechsel gemessen. Für das zu testende System, das für vier Zonen konfiguriert ist, dauert ein kompletter Kontextwechsel 146 Taktzyklen – oder 608 ns bei einer Taktfrequenz von 240 MHz. Bei einem System, das mit einer Preemtion-Time von 10 ms konfiguriert ist, beträgt der Aufwand für die Verwaltung im schlimmsten Fall 0,006 %, was in jeder realen Anwendung praktisch vernachlässigbar ist.

Literatur

[1] Car, B.; Garlati, C.: Systemdesign – Viele vertrauenswürdige Umgebungen. elektronik.de, 28.8.2019, www.elektroniknet.de/elektronik/embedded/viele-vertrauenswuerdige-umgebungen-168719.html

Die Autoren

Dr.-Ing. Cesare Garlati

ist ein anerkannter Experte für Informationssicherheit. Als ehemaliger Vizepräsident für mobile Sicherheit bei Trend Micro ist Dr. Garlati der Gründer von Hex Five Security und der Erfinder von MultiZone, der ersten TEE für RISC-V-Prozessoren. Er ist ein langjähriger Befürworter von Open-Source-Software und offener Standards, hatte sich in der prpl Foundation als Chefstratege für Sicherheit engagiert und ist aktives Mitglied der RISC-V Foundation.

Dr. Garlati hat einen MBA von der U.C. Berkeley, einen Master in Elektrotechnik und Informatik, professionelle Zertifizierungen von Microsoft, Cisco und Oracle und ist Fellow der Cloud Security Alliance, wo er die Gruppen Mobile Security und IoT Security gegründet und geleitet hat.

cesare@hex-five.com

Prof. Dr. Sandro Pinto

ist Wissenschaftler und eingeladener Professor an der Universität Minho, Portugal. Er hat einen Doktortitel in Elektronik und Computertechnik. Während seiner Promotion war Prof. Pinto Gastforscher am Asian Institute of Technology (Thailand), der Universität Würzburg (Deutschland) und der Jilin Universität (China). Er verfügt über einen fundierten akademischen Hintergrund und hat mehrere Jahre mit der Industrie zusammengearbeitet – mit deinem Fokus auf Betriebssystemen, Virtualisierung und Sicherheit für eingebettete, cyber-physische und IoT-basierte Systeme.

Prof. Pinto ist ein langjähriger Unterstützer von Open-Source-Projekten, Mitglied der RISC-V Foundation und hilft Hex-Five derzeit dabei, eingebettete Sicherheit in großem Maßstab praktisch umzusetzen.

d5631@dei.uminho.pt

- Viele vertrauenswürdige Zonen

- Die Umsetzung der TEE mit mehreren Zonen