Field Programmable Gate Array

Energiesparend + schnell + klein

Eine hohe Rechenleistung wird in Edge-Applikationen immer wichtiger. Gleichzeitig ist im Edge aber auch höchste Energieeffizienz gefordert. Diese Kombination stellt oft ein Problem dar, das die FPGAs aus der Titanium-Familie lösen können.

Eine hohe Rechenleistung im Edge wird zum Beispiel zur Vorverarbeitung von Daten benötigt, um etwa sehr schnell zu reagieren oder um die Datenflut zu minimieren, die die Sensoren aufnehmen und an übergeordnete Systeme wie etwa in die Cloud oder zum nächsten Board weiterzuleiten. Dabei ist klar, dass diese Kommunikation möglichst effizient gestaltet werden sollte, denn das spart Kosten und minimiert den Platzbedarf. Und es ist auch klar: Kleinere Datenmengen können kleinere oder langsamere Interfaces ermöglichen, was sich immer positiv auf die Kosten auswirkt.

Jobangebote+ passend zum Thema

Das Edge-Problem lösen

Bausteine für die Vorverarbeitung der Daten mit entsprechender Rechenleistung gibt es schon länger auf dem Markt. Das Problem von Edge-Applikationen ist aber, dass sie gleichzeitig auch sehr effizient mit der Energie haushalten müssen, um die Leistung, die zugeführt werden muss, möglichst gering zu halten oder die Abwärme zu verringern.

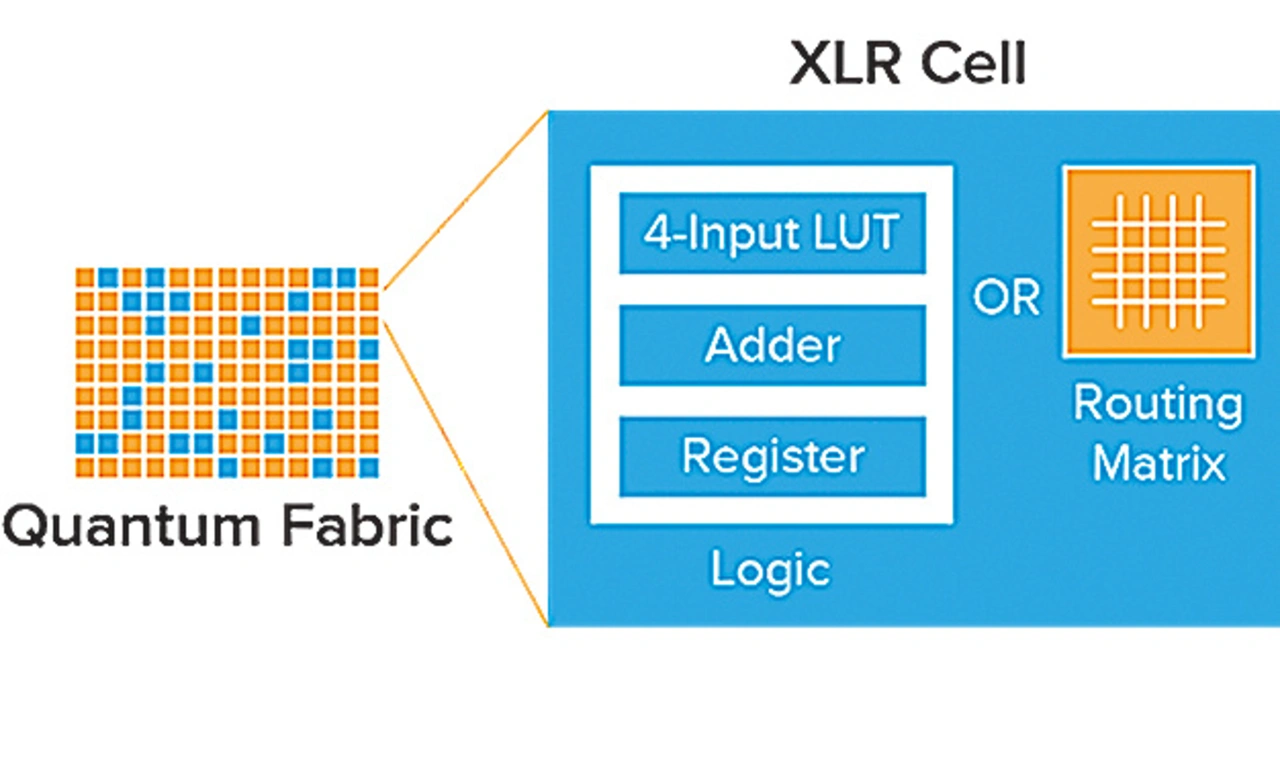

Hier setzt Efinix mit seiner »Quantum-Compute-Architektur« in der Titanium-Familie an, denn die Quantum-Compute-Architektur ermöglicht ein flexibles Routing über den kompletten Baustein hinweg und zeichnet sich durch eine Halbierung der Fläche zu vergleichbaren FPGAs in gleicher Silizium-Struktur aus. Die Folge: eine doppelt so hohe Logikdichte auf gleicher Fläche.

Gleichzeitig werden mit diesem Ansatz der Stand-by-Strom und die dynamische Leistungsaufnahme verringert, da durch die Quantum-Compute-Architekture die Verbindungen zwischen den XLR-Zellen kürzer gehalten werden können. XLR steht für »eXchangeable Logic and Routing«, eine Besonderheit von Efinix, denn XLR-Zellen können flexibel für Logik und Routing eingesetzt werden. Und zurück zu den kürzeren Verbindungen: Sie haben eine geringere Kapazität zur Folge, was wiederum einen positiven Einfluss auf die Verlustleistung sowie die Geschwindigkeit hat.

Ein weiterer Vorteil der Architektur ist, dass sie skalierbar ist. Das bedeutet, dass Entwickler sehr effizient kleine, aber auch große FPGAs entwickeln können, ohne in die Routing-Probleme von Standard-FPGAs zu laufen.

Titanium-FPGAs

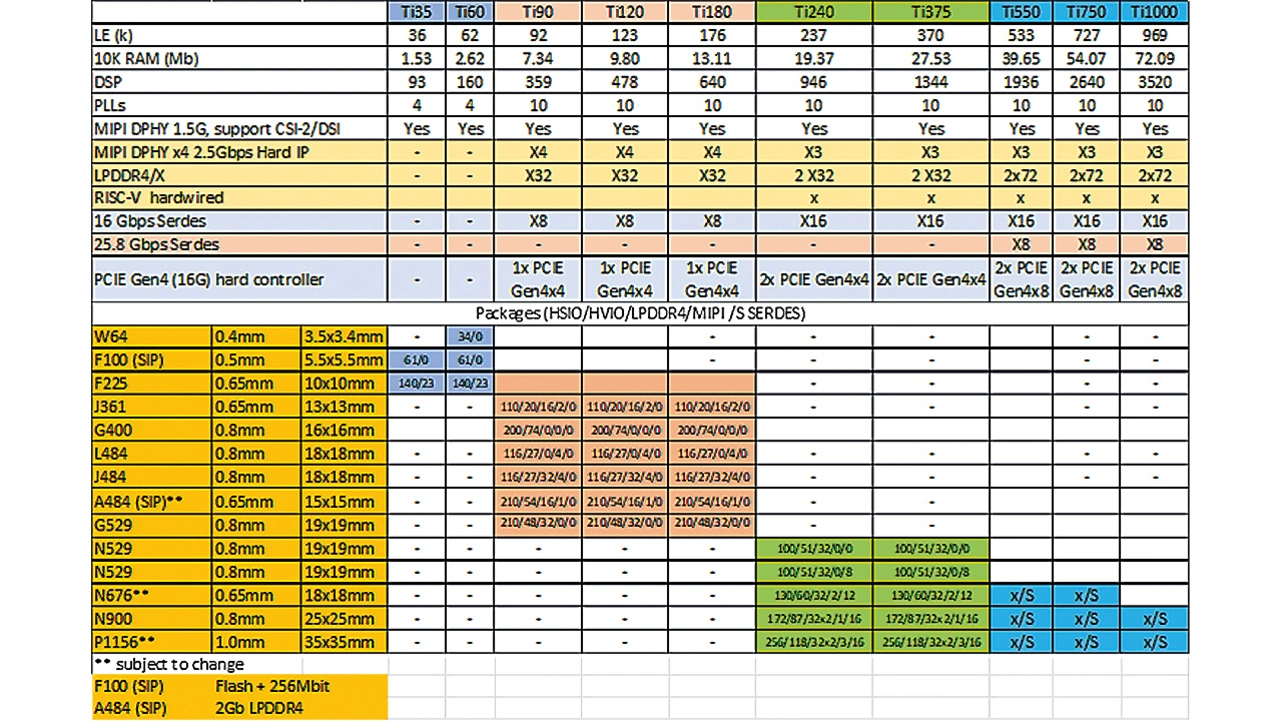

Die Titanium-FPGAs basieren auf einem 16-nm-TSMC-Prozess. Die ersten Bausteine, die bereits in der Produktion sind, sind der »Ti35« und der »Ti60«. Den »Ti60« gibt es auch in einem Wafer-Level-Chip-Scale-Gehäuse, welches die Die-Fläche widerspiegelt, sie beträgt lediglich 3,5 x 3,4 mm² für ein FPGA mit 60.000 Logikelementen.

Auch die Titanium-Familie basiert auf der Quantum-Compute-Architektur. Wie bereits erwähnt, basiert sie auf XLR-Zellen, die sowohl als Logik als auch für das Routing genutzt werden können. Das bedeutet, dass die Titanium-FPGAs dank dieser Technologie Routing-Ressourcen in Bereichen bereitstellen können, in denen diese benötigt werden. Das hat zur Folge, dass für Entwickler auf Basis von Efinix-Komponenten, nicht die Gefahr besteht, in typische Routing-Probleme zu laufen, wie sie mit herkömmlichen FPGA-Architekturen auftreten – und das gilt für kleinere wie größere Efinix-FPGAs. Gleichzeitig fällt damit auch die Die-Größe klein aus, was der Ti60 im Wafer-LevelChip-Scale-Gehäuse deutlich aufzeigt.

SiPs mit zusätzlichem Speicher

Den Ti35 und Ti60 gibt es auch als System-in-Package (SiP), in dem Fall in einem BGA100-Gehäuse (5,5 x 5,5 mm2). Efinix hat in dem SiP ein FPGA mit 35.000 bzw. 60.000 Logikelementen mit weiteren Bausteinen kombiniert. Dazu gehört ein HyperRAM, das eine Kapazität von 256 Mb aufweist und mit einer Datenrate von bis zu 500 Mb/s kommuniziert. Hinzu kommt noch ein 16 Mb großes SPI-Flash zum Booten des Bausteins, wobei die Speicherkapazität ausreicht, um zwei komprimierte Images aufzunehmen. Dank dieses Ansatzes sind auch Fail-Safe-Applikationen mit einem »Golden Image« einfach zu realisieren.

Weitere Eigenschaften der Titanium-FPGAs

Die integrierten HSIOs (Highspeed I/Os) unterstützen eine Geschwindigkeit von 1,5 Gb/s für LVDS aber auch 1,5 Gb/s für MIPI-CSI2 und DSI, darüber hinaus ist ein Anschluss an DDR3-Speicher mit bis 800 Mb/s möglich. Die HVIOs (High Voltage I/Os) wiederum unterstützen 1,2 V bis 3,3 V (LVCMOS). Die festverdrahteten Memory- und DSP-Blöcke erlauben eine Geschwindigkeit von 1000 MHz im Register-Mode.

Mit diesen Features ist die Titanium-Familie in der Lage, einen RISC-V- Prozessor (Sapphire RISC-V SoC von Efinix) mit bis zu 350 MHz zu takten. Die standardmäßigen Systemfrequenzen liegen bei den Titanium-FPGAs zwischen 300 und 450 MHz, dies ist abhängig von der kombinatorischen Tiefe des Designs.

Die Verlustleistung des Ti60 liegt bei der Low-Power-Variante (0,85 V) im Stand-by-Modus bei typischerweise zirka 16 mW.

Zur Datensicherheit bietet der Ti35/60 einen SEU-Checker (SEU, Single Event Upset, dabei geht es um die Erkennung, dass ein Bit kippt), aber auch eine AES-256-Verschlüsselung sowie eine RSA-4096-Authentifizierung.

Die drei neuesten Familienmitglieder sind die FPGAs Ti90-, Ti120 und Ti180, die in den verschiedenen Gehäusen zur Verfügung stehen. Diese Bausteine weisen die gleichen Features wie die Ti60-FPGAs auf, darüber hinaus unterstützen sie zusätzlich auch MIPI CSI2/DSI bis zu 2,5 Gb/s sowie LPDDR4/X-Speicherschnittstellen mit bis 3,3 Gb/s (Gehäuse-abhängig).

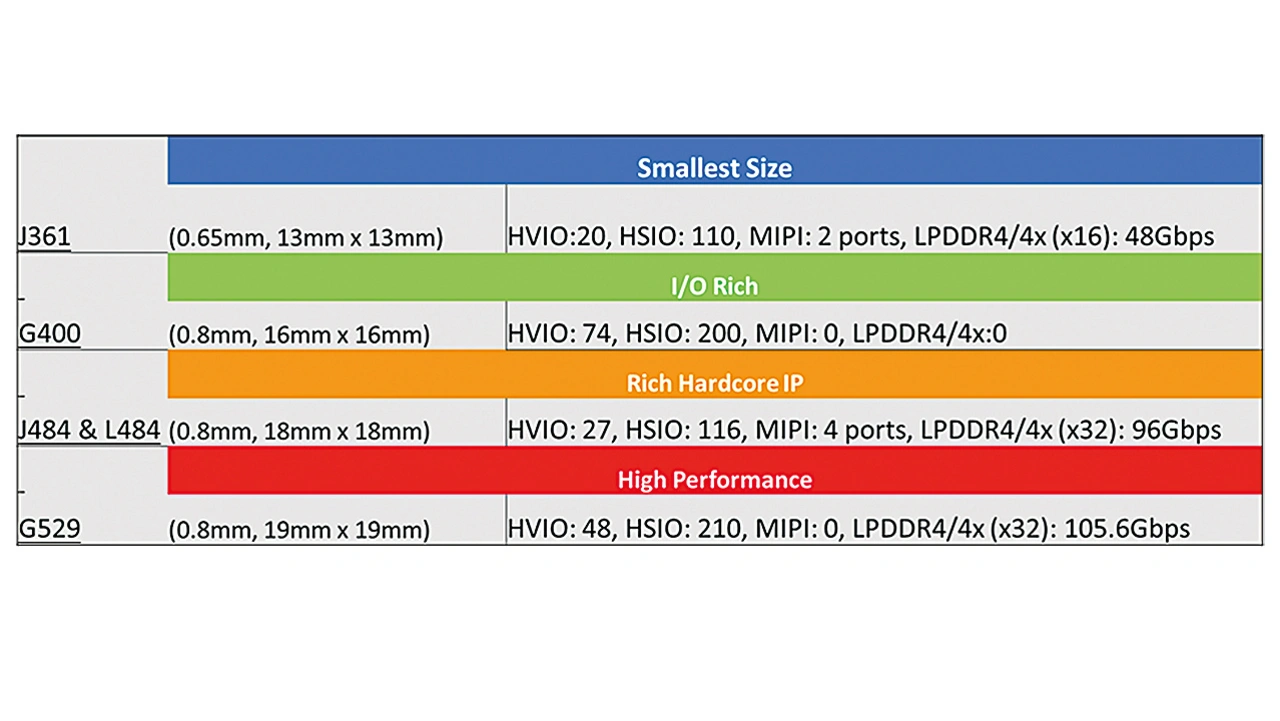

Für die verschiedenen Anwendungen stehen die verschiedensten Gehäusevarianten zur Verfügung. In den jeweiligen Gehäusen stehen entsprechend natürlich auch unterschiedliche Funktionen zur Verfügung.

Das zurzeit kleinste Gehäuse für diese drei Bausteine ist eine BGA361- Variante (13 x 13 mm² mit einem Pitch von 0,65 mm). Dieses Gehäuse bietet zwei MIPI-x4-Schnittstellen (2,5 Gb/s) sowie eine 16 Bit-LPDDR4/x-Schnittstelle mit bis zu 3 Gb/s. Die Bausteine im G529-Gehäuse (19 x 19 mm², 0,8 mm Pitch) bieten eine Speicherschnittstelle bis 3,3 Gb/s mit einer Busbreite von 32 bit sowie 210 HSIOs und 48 HVIOs. Die Bausteine im 484-Gehäuse (18 x 18 mm2, 0,8 mm Pitch) bieten eine 32-bit-Speicherschnittstelle (nur J484) mit bis zu 3 Gb/s sowie 116 HSIOs und 27 HVIOs. Für Applikationen, die mehr I/Os benötigen, steht ein BGA400 (16 x 16 mm2, 0,8 mm Pitch) zur Verfügung, das 200 HSIOs sowie 74 HVIOs aufweist.

DSP-Funktionsblock

Für schnelle Filterapplikationen bietet der in die FPGAs integrierte DSP-Block die Möglichkeit, folgende verschiedene Busbreiten zu unterstützen: 19 x 18, 11 x 10 oder 7 x 6. Hierbei können Integer-Multiplikationen sowie Additionen/Subtraktionen (Akkumulator) in einem Block unterstützt werden. Darüber hinaus kann der DSP-Block auch Floating-Point-Formate für Multiplikationen sowie Additionen/Subtraktionen (Akkumulator) verarbeiten. Alle Funktionen im DSP-Block können mit einer Geschwindigkeit von 1000 MHz durchgeführt werden.

Durch die Verwendung von fest verdrahteten Schaltungen für MIPI-DPHY- und LPDDR4/X-Schnittstelle konnte auch bei diesen Bausteingrößen die Verlustleistung sehr gering gehalten werden. So liegt die typische Verlustleistung bei den Ti180-Low-Power-Bausteinen im Bereich von 70 mW. Bei der Benutzung einer 16 Bit LPDDR4x-Schnittstelle (50 % Read/Write) kommen lediglich 530 mW (typisch) zur Verlustleistung hinzu.

Somit sind typische Kamera-Applikationen mit einer Vorverarbeitung der Daten einfach und effizient zu realisieren. Schnittstellen wie MIPI-CSI2 oder LVDS lassen sich einfach über den IP-Manager sowie Interface-Designer von Efinix erstellen. Der LPPDDR4/X-Speicher wird über eine AXI-Schnittstelle angesteuert und im Interface-Designer konfiguriert.

Der Ti60F225Q3 sowie der Ti180J484Q3 und Ti180G400Q3 stehen außerdem als AEC-Q100-Bausteine für Automotive-Applikationen zur Verfügung.

Aktuell arbeitet Efinix am Ti375-FPGA mit Highspeed-SERDES und festverdrahteten PCI-E Gen4- und Quad-RISC-V-Core.

Softwareunterstützung

Die Entwicklungssoftware »Efinity« ist kostenlos und kann nach der Registrierung von der Unternehmens-Website heruntergeladen werden. Die Software unterstützt Verilog, System Verilog und VHDL bis 2008. Die Sprachen können auch in einem Design gemixt werden. Ab Softwareversion 2023.1 wird auch eine graphische Darstellung des RTL-Designs unterstützt.

Bei der Software unterscheidet Efinix zwischen Core- und Interface-Design, wobei beides in einem Tool integriert ist.

Im Interface-Design können Entwickler die I/O-Belegung mit den verschiedenen I/O-Standards festlegen, ohne eine Zeile RTL-Code zu schreiben. Auch die Benutzung von PLLs, Speicherschnittstellen oder MIPI-Interfaces erfolgt über den Interface-Designer. Das bedeutet, dass die RTL-Beschreibung nur den Teil des FPGA-Designs beinhaltet, der einfach über verschiedene FPGAs ausgetauscht werden kann.

Das Timing kann über Standard-SDC-Files überprüft werden. Zur Systemverifikation steht ein Debugger zur Verfügung, mit dem Entwickler interne Signale im laufenden Betrieb triggern und evaluieren können. Im Debugger können Entwickler auch Signale im RTL-Design auswählen, was aber auch erst nach der Synthese erfolgen kann. Die Entwickler bevorzugen meist die Auswahl im RTL-Design, da hier die Signalnamen unverändert zur Verfügung stehen.

Im IP-Katalog sind die verschiedenen IP-Cores abgelegt. Dazu gehören verschiedene Speicherblöcke, aber auch serielle Interfaces sowie Ethernet MAC und RISC-V. Die IP-Blöcke können nach den jeweiligen Bedürfnissen konfiguriert und entsprechend generiert werden. Alle diese IP-Cores gehören zur Software und sind somit ebenfalls kostenlos verwendbar.

Die »Efinity«-Software läuft unter Windows 10 und darüber sowie unter Linux Ubuntu/Red Hat Enterprise. Die Version 2023.1 ist zertifiziert nach IEC 61508 (SIL4) und ISO 26262-2018 (ASIL D) und erleichtert dadurch die Arbeit bei Safety-kritischen Anwendungen.

Neben der Standard-Design-Software stellt Efinix auch KI-Lösungen basierend auf dem Efinix-RISC-V mit Hardware-Beschleunigung (TinyML) zur Verfügung – auch in diesem Fall kostenlos. Mit der TinyML-Lösung können KI-Modelle aus TensorFlow Lite geladen werden und danach kann der Entwickler entsprechend den eigenen Anforderungen die verschiedenen Lagen des neuronalen Netzwerkes beschleunigen bzw. die Verlustleistung anpassen.

Evaluation-Boards

Für die einfache Implementierung einer Schaltung oder auch nur Teile einer Schaltung stehen dem Entwickler verschiedene Evaluation-Boards zur Verfügung. Für den Ti60 gibt es ein »Ti60 Basis Board« mit HyperRam und den verschiedenen Adaptern für die Interfaces wie z. B. MIPI. Ein MIPI-DSI-Display sowie eine MIPI-CSI2-Kamera ist auch enthalten. Ein ähnliches Konzept verfolgt Efinix auch mit seinem »Ti180 Eval Board«. Das Ti180 Basis Board ist mit einem LPDDR4X-Speicher (bis 3 Gb/s) ausgestattet, plus verschiedene Adapter für die Interfaces z. B. MIPI, Ethernet, DDR3 etc.

Zusammenfassung

Efinix Titanium FPGAs erfüllen alle Anforderungen, die an Bausteine für Edge-Applikationen gestellt werden. Mit der einzigartigen Quantum-Architektur werden »Low Power«, »High Speed« in kleinen Gehäusen möglich und dies zu einem attraktiven Preis. Die Software ist kostenlos, und Evaluation Boards sind verfügbar, um eine schnelle Implementierung zu ermöglichen. Referenzdesigns für verschiedene Applikationen helfen, den ersten Schritt mit den Efinix-Bausteinen einfach und erfolgreich zu gestalten.

Der Autor

Harald Werner ist EMEA Senior Sales Director und Managing Director von Efinix.