Dense 3D-Stacking, CFETs, TMDs …

Neue Technologien statt bloßer Geometrieverkleinerung

Auf der IEDM 2023 in San Francisco wurden wieder zahlreiche Durchbrüche in der Halbleitertechnik und verwandten Technologien präsentiert. Das Motto lautete: »Devices for a Smart World Built Upon 60 Years of CMOS«.

Bekanntermaßen wird die laterale Skalierung über die Verkleinerung der Prozessgeometrien immer schwieriger; dementsprechend treibt die Halbleiterindustrie 3D-Ansätze voran. Im Gegensatz zum 3D-Ansatz im Packaging-Bereich, bei dem komplette Chips (oder Chiplets) zusammengefügt werden, geht es beim »Dense 3D-Stacking« darum, die Skalierung durch das Stapeln einzelner Transistoren voranzutreiben. Bei CFETs (komplementäre Feldeffekttransistoren) werden GAA-Transistoren (GAA: Gate All Around) mit entgegengesetzter Polarität vertikal gestapelt, sodass dank der Tatsache, dass auf horizontaler Ebene keine Abstände zwischen NMOS- und PMOS-Transistoren notwendig sind, die Grundfläche einer CMOS-Anordnung halbiert wird. Intel konnte auf dem 69. IEDM (International Electronic Device Meeting) in San Francisco mit einigen wichtigen Neuerungen punkten. So konnte das Unternehmen monolithisch einen gestapelten CFET mit drei NMOS-Nanobändern (Nanoribbons) auf drei PMOS-Nanobändern mit einem Abstand von 30 nm implementieren, das Ganze mit einer rückseitigen Stromversorgung und direkten Rückseitenkontakten (BSCON) kombinieren und damit einen funktionsfähigen Inverter als Testschaltung mit einem Gate-Abstand von 60 nm realisieren.

Wie bereits früher nutzt Intel für die Fertigung einen Dual-Source/Drain-Epitaxieprozess und einen Dual-Metal-Gate-Fertigungsprozess. Darüber hinaus hat Intel auch einen »Depopulation«-Prozess beschrieben, mit dem obenliegende Transistoren vom Stapel entfernt werden können. Dieser Ansatz kann helfen, parasitäre Effekte in Schaltungen zu reduzieren, in denen die Anzahl der PMOS- und NMOS-Komponenten nicht gleich ist (z. B. SRAM-Bitzelle). Intel trägt mit diesen Entwicklungen aus der Sicht der Experten zu einem besseren Verständnis des Potenzials für die Skalierung von CFETs für Logik- und SRAM-Anwendungen bei und hilft, die wichtigsten Prozessfaktoren zu verstehen.

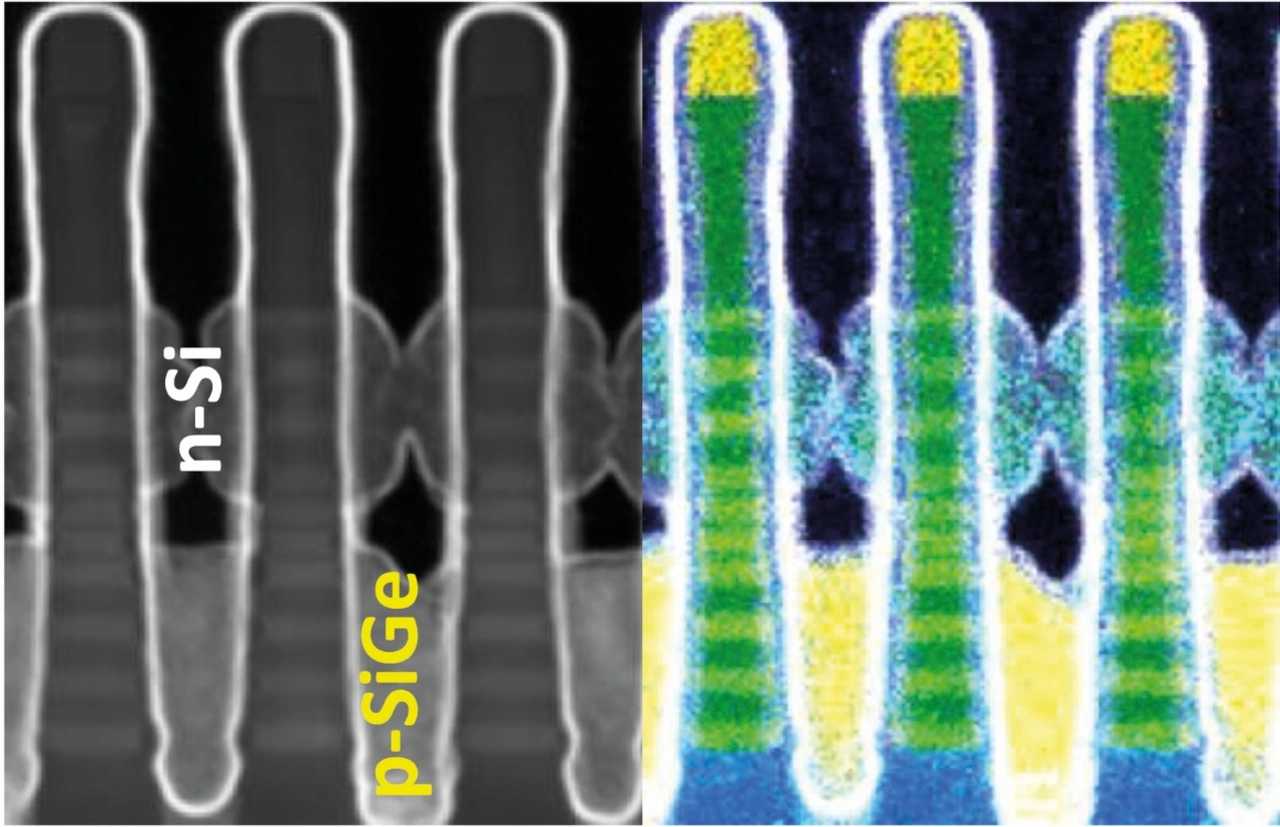

Ein weiterer Vortrag zum Thema CFETs kam von TSMC. Die Forscher haben in ihrem Vortrag ihren sogenannten praktischen, monolithischen CFET-Architekturansatz für die Logikskalierung vorgestellt. Dabei stapelt TSMC NMOS- auf PMOS-Nanosheet-Transistoren mit einem Gate-Abstand von 48 nm. Aus der Sicht der Experten zeichnet sich der Ansatz von TSMC dadurch aus, dass die Transistoren einen hohen Einschaltstrom und einen geringen Leckstrom im Unterschwellenbereich aufweisen, was zu einem sehr hohen Verhältnis von Einschalt- und Ausschaltstrom führt (sechs Größenordnungen). Außerdem konnte mit diesem Ansatz eine relativ hohe Ausbeute erreicht werden. Darüber hinaus konnte TSMC einen Gate-Abstand von lediglich 48 nm erreichen, was mit bisherigen Ansätzen nicht möglich war. Dafür nutzt TSMC einen vertikal gestapelten n/p-Source-Drain-Epitaxie-Prozess, der eine mittlere dielektrische Isolierung, einen inneren Spacer und eine n/p-SD-Isolierung umfasst. Die Experten weisen darauf hin, dass beim TSMC-Ansatz zwar noch weitere wesentliche Merkmale integriert werden müssen, um das Potenzial der CFET-Technologie ausschöpfen zu können, dass diese Arbeit aber den Weg dafür ebnet.

Jobangebote+ passend zum Thema

TSMC hat in diesem Bereich noch mit einem weiteren Vortrag laut den Experten eine besondere Entwicklungsleistung gezeigt, dieses Mal bei 2D-Materialien. FET-Bauelemente jeder Polarität (n-FETs und p-FETs) müssen eine aufeinander abgestimmte Leistung aufweisen, damit CMOS-Logikbauelemente ordnungsgemäß funktionieren. Doch während MoS2 ein geeignetes TMD-Material für n-Typ-Bauelemente ist, eignet es sich nicht gut für p-Typ-Bauelemente, für die das TMD-Material WSe2 besser geeignet ist. Außerdem müssen diese beiden extrem dünnen Materialien robust genug sein, um den typischen Herstellungsprozessen standzuhalten.

Als erstes Unternehmen der Branche haben die Entwickler bei TSMC gut angepasste N- und PMOS-Transistoren entwickelt, die mit diesen beiden TMD-Kanalmaterialien hergestellt wurden. Sie konnten auch die Robustheit dieser hoch skalierten (~50 nm Kanallänge) und stromdichten Materialien zeigen, indem sie sie separat auf Saphir züchteten und dann Die für Die auf einen 300-mm-Silizium-Wafer übertrugen, um sie zu integrieren. Die Bauelemente zeigten nach diesem Transferprozess eine nahezu unveränderte Leistung mit einem hohen Ausgangsstrom (~410 µA/µm) bei gleicher Gate-Übersteuerung sowohl für n- als auch für p-FETs (VDS = 1 V). Darüber hinaus erreichte die p-FET-Mobilität ein Rekordniveau (~30 cm2/V∙s).

Leistungselektronik

Intel-Forscher haben aufbauend auf ihren früheren Arbeiten zur Integration der GaN-Technologie in die traditionelle Si-CMOS-Technologie den ersten integrierten CMOS-Treiber-GaN-Leistungsschalter (»DrGaN«-Leistungsschalter) in 300-mm-GaN-on-Si-Technologie präsentiert. Er enthält einen e-Mode-HEMT und einen integrierten monolithischen 3D-Si-PMOS und ermöglicht somit Lösungen für die Stromversorgung, die mit den Anforderungen an die Leistungsdichte und -effizienz zukünftiger CPUs und GPUs Schritt halten können. Die 180-nm-DrGaN-Bauelemente weisen einen hervorragenden Rds(on) von 0,8 mΩ∙mm2 und Leckstrom von deutlich weniger als 0,1 mA auf. Die Forscher haben einen neuen Gate-Last-Prozessablauf für die monolithische 3D-Integration von GaN und Si-CMOS durch einen Schichttransfer erläutert, bei dem die Hochtemperatur-Aktivierungsschritte für die Si-CMOS-Transistoren abgeschlossen werden, bevor das Gate-Dielektrikum des GaN-MOSHEMT abgeschieden wird.

Damit wird eine große Hürde bei der monolithischen 3D-Integration von GaN- und Si-CMOS-Transistoren überwunden. Außerdem können die GaN- und Si-CMOS-Transistoren mit diesem Prozessablauf denselben Back-End-Interconnect nutzen, was den Widerstand zwischen den Verbindungen eliminiert und die Anzahl der Masken reduziert. Das beste FOM = 1/(Ron∙QGG) von 0,59 (mΩ∙nC)–1 wurde bei einem GaN-MOSHEMT mit einer Gate-Länge von 30 nm erreicht und zeigt das Potenzial für eine weitere Skalierung dieses Ansatzes.

Neuromorphes Computing

Ein Team, das von der Tsingua-Universität geleitet wurde, hat eine monolithische 3D-Architektur vorgestellt, das eine GPU-ähnliche Genauigkeit erreicht, aber mit einem weitaus geringeren Energieverbrauch und einer deutlich kürzeren Inferenzzeit, und adressiert damit das Problem, dass groß angelegte KI-Modelle immer höhere Anforderungen an die Rechenleistung und Geschwindigkeit der Hardware stellen. Typische 2D-Compute-in-Memory-Architekturen (CIM) leiden unter Engpässen bei der Datenübertragung zwischen den verschiedenen CIM-Array-Schichten, die als Verarbeitungselemente verwendet werden.

Das liegt daran, dass die Berechnungsergebnisse jeder Schicht einen On-Chip-Bus mit begrenzter Bandbreite nutzen müssen, um zwischen den CIM-Arrays und Puffern zu wechseln, was die Gesamtrechenzeit für tiefe neuronale Netze erheblich verlängert. Das Team unter der Leitung der Tsinghua-Universität hat eine monolithische 3D-Bauelementarchitektur entwickelt, bei der Puffer-Arrays direkt auf den CIM-Arrays angeordnet sind und über dichte, feinkörnige Vias verbunden sind, was die Bandbreite erhöht. Das 1-kbit-Array besteht aus drei Funktionsschichten: eine Si-CMOS-Logikschicht, ein RRAM-Array als CIM-Schicht und eine CNT-RRAM-Schicht für den Daten-Cache. Alle Komponenten und Schaltungen wurden charakterisiert, um zu bestätigen, dass jede Schicht wie vorgesehen funktioniert.

Mit diesem Ansatz konnten die Forscher bei der Bildklassifizierung mit MLP- und ResNET32-Netzwerken eine GPU-äquivalente Genauigkeit von zirka 96,5 Prozent erreichen, wobei der Energieverbrauch um den Faktor 39 und die Inferenzzeit um den Faktor 49,6 geringer ausfallen.

IEDM 2023

Die IEDM 2023 war bereits die 69. Konferenz dieser Art. In mehr als 225 Vorträgen aus Industrie und Forschung aus Asien (55 Prozent), Amerika (27 Prozent) und Europa (18 Prozent) konnten knapp 2000 Teilnehmer erfahren, welche Fortschritte in den verschiedenen Halbleitertechnologien erzielt wurden.

In der Konferenz standen folgende Themen im Mittelpunkt:

- Vier Fokus-Sessions: »Neuromorphes Computing für intelligente Sensoren«, »Logik, Speicher, Gehäuse und Systemtechnologien für zukünftige generative KI«, »3D-Stacking für die nächste Generation von Logik und Speicher mithilfe von Wafer-Bonding und zugehörigen Technologien« und »Nachhaltigkeit in der Halbleitertechnologie und Fertigung«

- CMOS-Skalierung: CFETs und 2D-Channel-FETs

- Speicher

- Neuromorphes Computing (für diesen Bereich wurde ein eigenes technisches Unter-Komitee eingerichtet)

- Leistungselektronik

- High-Speed-Bausteine

- Fortschritte im Imaging-Bereich.