Neue RISC-V-Prozessor-Familie

Vom Mikrocontroller bis zum Multicore-Prozessor

Fortsetzung des Artikels von Teil 1

Neue CPU bei Serie 7

Die neue Dual-Issue-CPU der Serie 7 stellt eine Abkehr von den bisherigen CPUs von SiFive dar: Die Serie 5 verwendet eine einfache fünfstufige skalare Pipeline, implementiert mit TSMCs 28-nm-Prozess ist eine Taktfrequenz von bis zu 1,5 GHz erreichbar. Der S54 enthält die RV64I-Basis-ISA sowie die Erweiterungen Multiply und Divide (M), Atomic (A) und Compressed (C). Optional verarbeitet der Serie-5-Prozessor die Gleitkomma-Erweiterungen mit einfacher (F) und doppelter Genauigkeit (D).

Jobangebote+ passend zum Thema

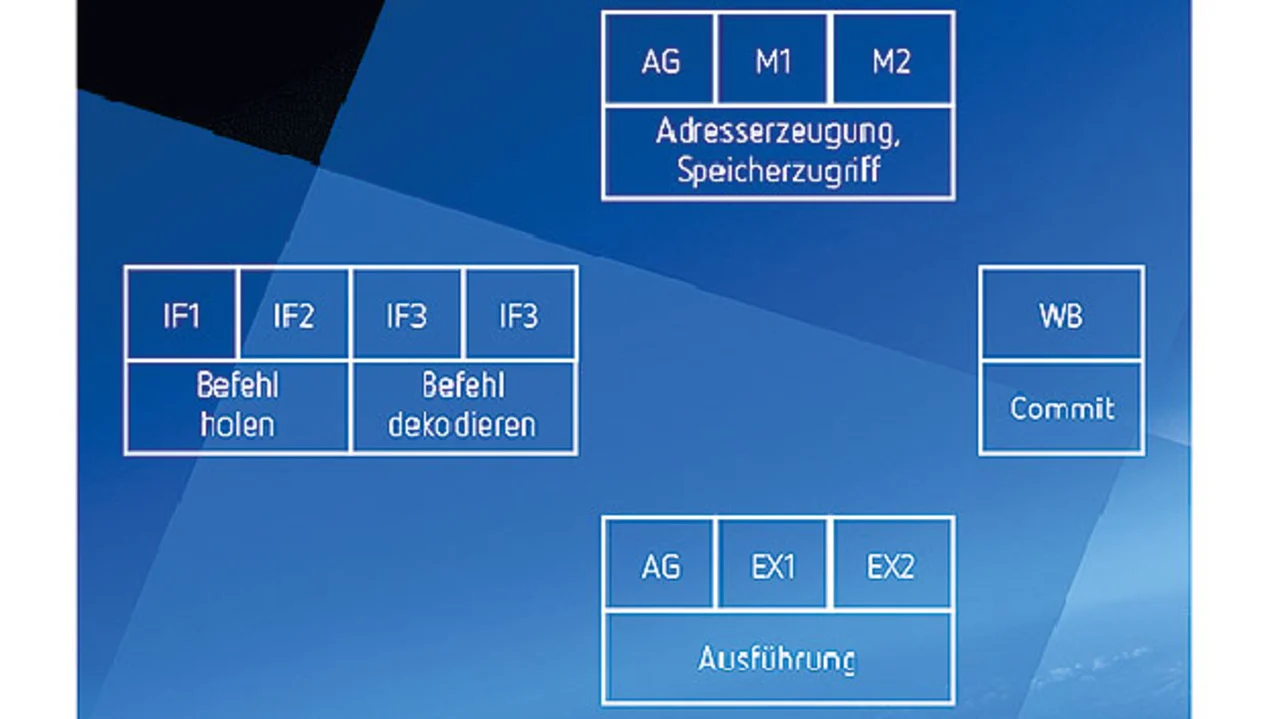

Wie Bild 3 zeigt, erweitert die Prozessor-Serie 7 die Pipeline auf acht Stufen und fügt mehrere Ausführungseinheiten für superskalare Operationen hinzu. Der erste Ausführungs-Slot führt Speicheroperationen (Laden/Speichern) und einfache Integer-Operationen aus, wogegen der zweite Slot beliebige Integer-Operationen (einschließlich Multiplizieren/Dividieren), Verzweigungsauflösung und Gleitkomma-Operationen ausführt. SiFive hat eine zweite Fetch-Stufe und eine zweite Datenspeicher-Zugriffsstufe hinzugefügt, um größere L1-Cache- und Scratchpad-Speicher zu ermöglichen. Eine zweite Decodierstufe übernimmt das superskalare Dispatching.

Beide Ausführungs-Slots enthalten in der 5. Stufe arithmetisch-logische Ausführungseinheiten (ALUs). Sie verarbeiten die meisten arithmetischen Anweisungen. Die Verzweigungsauflösung kann diese ALUs sofort verwenden, was bei einer Sprungfehlvorhersage zu fünf Taktzyklen Latenz führt. Wenn ein ALU-Befehl jedoch die Ausgabe eines anstehenden Ladevorgangs benötigt, geht er zu Stufe sieben über, die einen zweiten Satz von ALUs enthält. Diese »späten« ALUs ermöglichen eine Load-to-Use-Latenz von null Zyklen, was bedeutet, dass ein abhängiger ALU-Befehl in dem Zyklus abgearbeitet werden kann, der unmittelbar auf den Befehl folgt, der seine Daten lädt. Wenn eine Verzweigung mit den späten ALUs aufgelöst wird, steigt die Latenz bei einer Sprungfehlvorhersage auf sieben Taktzyklen an.

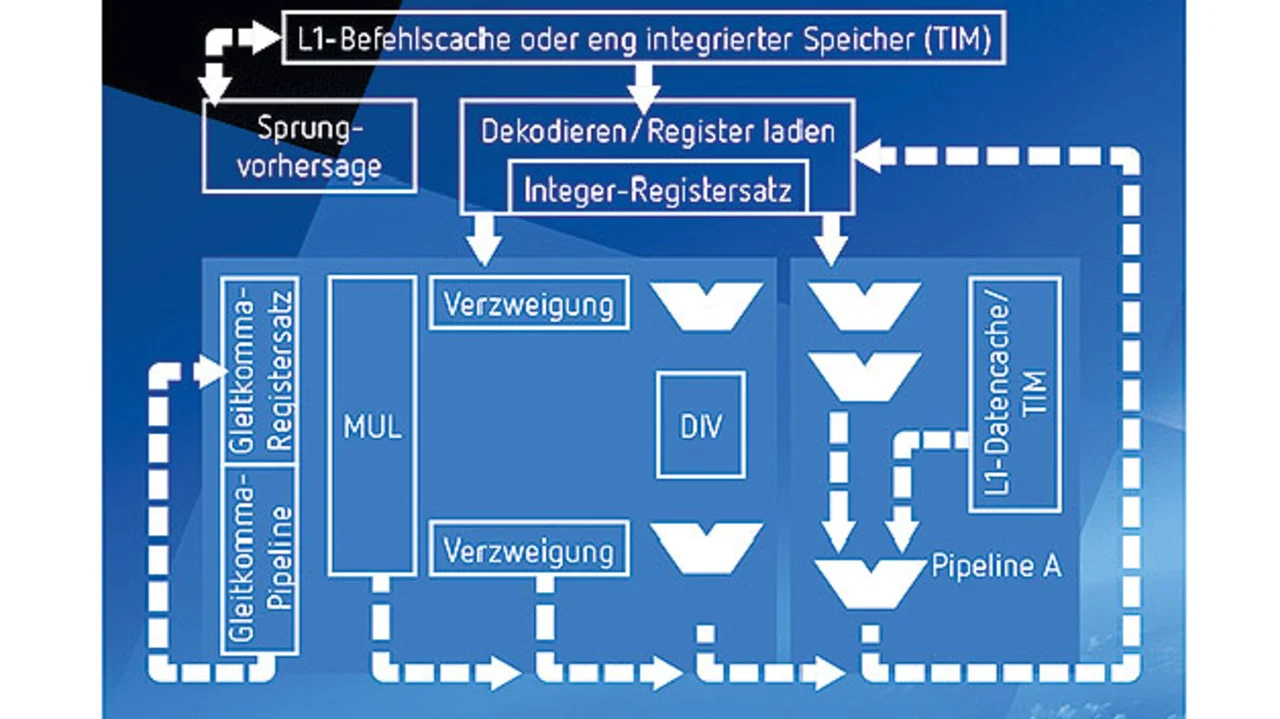

Die größte Änderung in der 7er-Serie ist die Überarbeitung des Speichersubsystems mit Daten-Cache und optionalem, eng integriertem Speicher (TIM, Tightly Integrated Memory). Der FIO-Port umgeht den Core-Complex-Bus. Bild 4 zeigt den Aufbau der CPU.

Der U74MC verfügt über einen 64-bit-Registersatz und einen 64-bit-Datenpfad, L1-Befehls- und Daten-Caches, die durch ECC geschützt sind, eine Physical-Memory-Protection- (PMP)-Einheit und eine Memory-Management- (MMU)-Einheit, die den Einsatz von Linux ermöglicht. Die MMU implementiert die 39-bit-Version (SV39) des RISC-V-Virtual-Memory-Systems. Die PMP schützt bis zu acht Speicherbereiche und ermöglicht die Vergabe von Berechtigungen für Zugriffe im Benutzermodus. Der Prozessor-Core kann auch einen lokalen Interrupt-Controller (CLIC) enthalten, um Interrupt-Priorisierung und Preemption zu ermöglichen. Um Seitenkanalangriffe zu vereiteln, kann die Systemsoftware beim Umschalten von Prozessen die Verzweigungshistorie löschen.

Der 32-bit E76 und der 64-bit S76 sind CPUs der Mikrocontroller-Klasse, die im Vergleich zum U74 keine MMU aufweisen, dafür aber optionalen, eng integrierten Speicher (TIM) und den FIO beinhalten. SiFive konfiguriert die E7x-Cores mit einem 64-KB-Instruktions-Cache mit Vier-Wege-Assoziativität, einem Instruktions-TIM, der in einem einzigen Zyklus adressierbar ist, oder beidem.

Für Daten kann ein Cache oder TIM gewählt werden. Obwohl der Daten-TIM von 4 KB bis 256 KB reicht, entscheiden sich die meisten Entwickler für 32 KB. Für echtzeitfähige Prozessoren können Entwickler den Instruktions-TIM verwenden und die dynamische Sprungvorhersage zur Boot-Zeit deaktivieren. Auf diesen Prozessorkernen laufen typischerweise ein Echtzeit-Betriebssystem (RTOS) und kleine Anwendungen, sodass keine komplexen Cache-Strukturen erforderlich sind.

| Vektoreinheit für den S7 von SiFive |

|---|

|

Anfang 2021 wurde VIS7 vorgestellt, ein Prozessor, der 64 Milliarden FP32-Operationen pro Sekunde ausführen und für deterministische Operationen ausgelegt ist. Der VIS7 verbindet den S7-Prozessor mit einer 512 bit breiten Vektoreinheit. Der neue VIS7-Prozessor enthält die Vektorerweiterung RVV 1.0. Die Vektoreinheit arbeitet mit 8-, 16- und 32-bit-Daten im Gleitkomma-, Festkomma- und Integer-Format. Sie verwendet eine 512-bit-Vektor- ALU und eine 512-bit-Vektorspeichereinheit. Der SiFive-Prozessor VIS7 erreicht 5,1 CoreMarks/MHz und liegt damit 12 % hinter dem R82 von ARM, und er arbeitet mit einer ähnlichen Spitzenfrequenz von 2,0 GHz. Er glänzt jedoch bei SIMD-Operationen, da seine Vektoreinheit 4-mal breiter ist und den FP32-Spitzendurchsatz der Neon-Einheit des R82 fast vervierfacht. rogrammierer können LMUL (lengthmultiplier) – ein Kontrollregister zur Gruppierung von Vektor-Registern – auch auf 2, 4 oder sogar 8 einstellen, wodurch im Extremfall ein 8182 bit breites virtuelles Register entsteht. LMUL verbessert zwar nicht den Spitzendurchsatz, aber es reduziert die Anzahl der Anweisungen, die zur Versorgung der Vektoreinheit benötigt werden. |

Der Core-Komplex umfasst einen vollständig kohärenten und gemeinsam genutzten Speicherbereich. Ein Platform-Level Interrupt Controller (PLIC) verteilt globale Interrupts. Jeder Prozessorkern kann konfiguriert werden, z. B. einer mit SRAM, ein anderer mit einem Beschleuniger und ein dritter Kern ohne beides. Alle Prozessorkerne sind mit einem Cache-kohärenten Bus verbunden und können den FIO-Port auf allen anderen Kernen sehen und darauf zugreifen, was bedeutet, dass sie auch auf das SRAM und einen möglichen benutzerdefinierten Beschleuniger der anderen Kerne zugreifen können.

Für einen einfachen Mikrocontroller kann, statt einer Multicore-Konfiguration, auch nur ein E76-Kern mit TCM-, FIO- und CLIC-Funktionen (Core-Local Interrupt Controller) verwendet werden und der L2-Cache und der PLIC-Block weggelassen werden. Ohne Berücksichtigung der Speicher belegt ein solcher Mikrocontroller im 28HPC-Prozess von TSMC 0,112 mm2 Siliziumfläche, wenn eine 9-Track-Standardzellenbibliothek verwendet wird. Laut SiFive nimmt dieser Mikrocontroller 20,4 mW auf, wenn auf ihm der Dhrystone-Benchmark bei 400 MHz Taktfrequenz läuft – ohne Speicher. Für eine maximale Leistung sollte eine 12-Track-Bibliothek im ungünstigsten Fall einen Betrieb mit 875 MHz ermöglichen, wobei der Prozessorkern 0,174 mm2 belegt und 74,4 mW Leistung aufnimmt.

- Vom Mikrocontroller bis zum Multicore-Prozessor

- Neue CPU bei Serie 7

- SiFive vs. Arm