»Intelligente« Peripherie in MCUs

Low Level Tasks automatisiert

Fortsetzung des Artikels von Teil 1

Merkmale des DTC

Nun zu den Details des DTC: Die Nutzung des SRAM zur Speicherung der DTC-Konfigurationsdaten bedeutet, dass der DTC-Controller nicht nur einen oder zwei Kanäle für die Datenübertragung erstellen kann, sondern 10 oder 20 – und falls erforderlich sogar mehr. Der Hauptnachteil dieses Mechanismus besteht darin, dass für jede Übertragung einige Zyklen benötigt werden, um vor jeder Übertragung die im SRAM gespeicherten Konfigurationsdaten zu lesen. Daher ist die DTC-Übertragung im Allgemeinen langsamer als eine DMA-Übertragung.

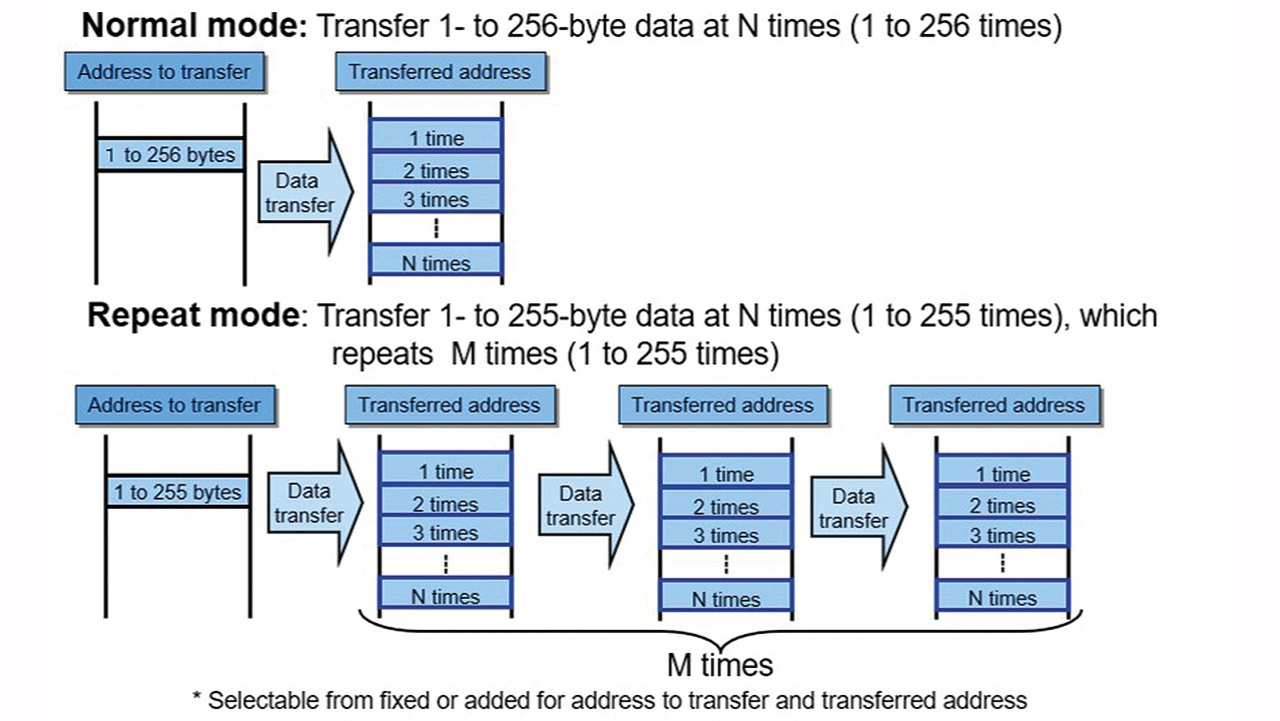

Der DTC kann ein Byte oder mehr zwischen Peripherie und Speicher oder Speicher und Peripherie bis zu 256-mal übertragen. Die Quell- und die Zieladresse für die Übertragung können jeweils gleich sein oder unabhängig voneinander inkrementiert oder dekrementiert werden. Dadurch entsteht eine Pufferstruktur im Speicher.

Am Ende der Übertragung kann der DTC einen Interrupt erzeugen, um der CPU mitzuteilen, dass die Daten bereit sind. Alternativ kann er eine zweite DTC-Übertragung auslösen. Auf diese Weise lassen sich mehrere Übertragungen aneinanderreihen. Deshalb wird dieser Modus auch als Chain-Modus bezeichnet. Der Chain-Modus kann besonders nützlich sein, wenn mehrere Datenelemente zwischen Peripherie und Speicher übertragen werden müssen. Der Chain-Modus ist besonders interessant, wenn er mit dem zuvor besprochenen DOC zum Einsatz kommt.

Jobangebote+ passend zum Thema

Denn dann können mehrere Übertragungen von verschiedenen Stellen im Speicher und/oder der Peripherie durch eine einzige Interrupt-Quelle ausgelöst werden. Das heißt zum Beispiel, dass mit einem Interrupt, z. B. dem ADC-Interrupt, Vergleichsdaten in den DOC geladen werden können. Durch die Verkettung einer zweiten Übertragung lassen sich die Daten aus dem ADC zum Abgleich vollautomatisch in den DOC laden. Diese Interrupt-Möglichkeit, eine komplexe Sequenz verschiedener Übertragungen zu erzeugen, ist nicht nur in Verbindung mit dem DOC äußerst leistungsfähig. Bild 3 zeigt verschiedene Betriebsmodi des DTC.

Der DTC kann auch in den Wiederholungsmodus versetzt werden und die Übertragung weitere Male wiederholen. Für die meisten Anwendungen bietet der DTC einen perfekten Kompromiss zwischen Geschwindigkeit und Flexibilität. Die Anwender können nahezu unbegrenzt automatische Übertragungen zwischen jeder beliebigen Peripherie und jedem Speicher realisieren.

Dies zeigt, dass der DTC viel flexibler als der herkömmliche DMAC ist. Der DMAC ist jedoch immer noch die schnellere Methode, wenn höchste Geschwindigkeiten für die Datenübertragung erforderlich sind. Fast alle RA-Mikrocontroller enthalten eine Reihe von DMAC-Kanälen. Wenn es jedoch um Flexibilität und einfaches Datenmanagement geht, schneidet der DTC mit Abstand am besten ab. Darüber hinaus können Anwender mehrere Kanäle erstellen, die nur durch den verfügbaren SRAM begrenzt sind.

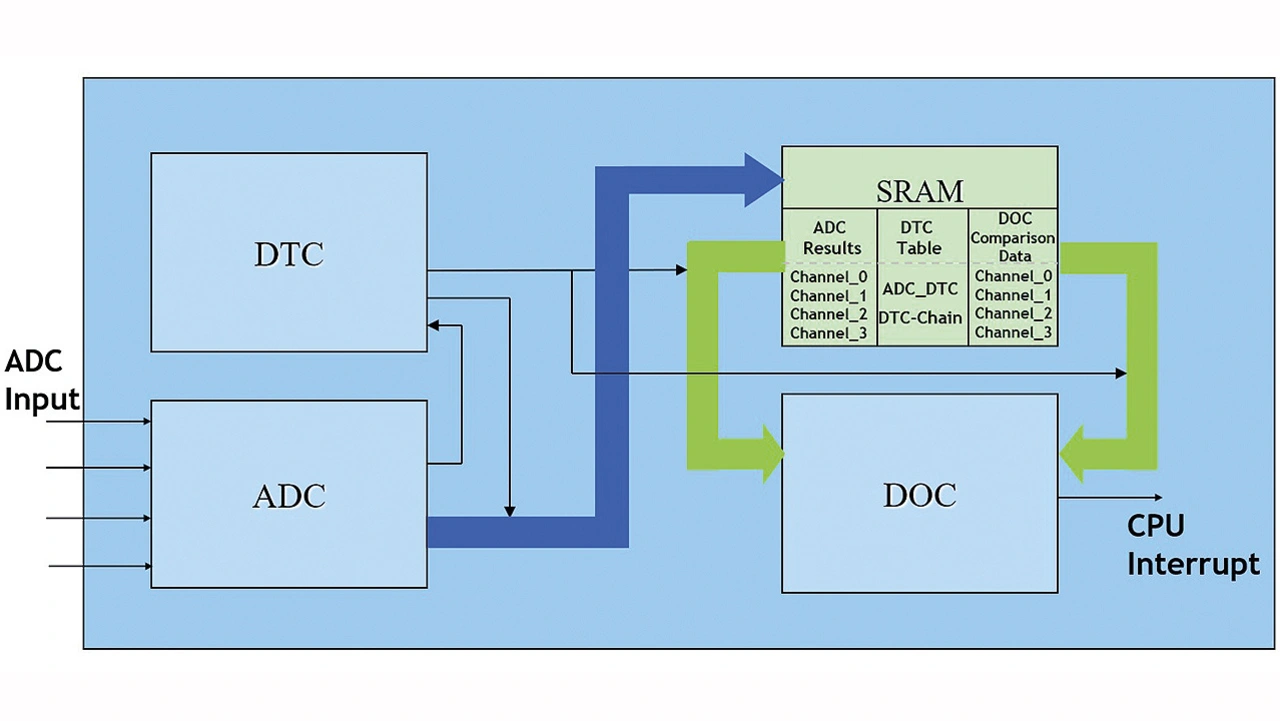

Nun folgt abschließend ein Blick darauf, wie sich DTC und DOC mit dem ADC kombinieren lassen, um ein »intelligentes« analoges Sampling-System zu entwickeln. Dies kann die Anforderungen an die CPU verringern und sogar die Leistungsaufnahme senken. Hierfür wird die CPU in den Ruhezustand versetzt, während ADC, DTC und DOC arbeiten. Das hier als Beispiel zu erstellende System ist ein einfacher Pegeldetektor mit mehreren Eingängen, der den Group-Scan-Modus des 12-bit-ADC nutzt, um jedes der vier Eingangssignale nacheinander abzutasten. Die Kombination aus DTC und DOC erkennt, ob ein programmierbarer Schwellenwert überschritten wird. Das System erzeugt nur dann einen Interrupt und weckt die CPU auf, wenn dieser Wert überschritten wurde.

Nach dem Hochfahren des Systems geht die CPU in den Ruhezustand, um Strom zu sparen. Sie wacht erst auf, wenn ein Interrupt vom DOC erfolgt, der anzeigt, dass der Schwellenwert überschritten wurde. Bild 4 zeigt ein vereinfachtes Diagramm des Systemdesigns.

Im Group-Scan-Modus tastet der ADC kontinuierlich jeden Eingang der Reihe nach ab und kopiert das Ergebnis in den SRAM. Sobald alle vier Eingänge abgetastet sind, erzeugt der ADC einen DTC-Request. Im Chain-Modus startet dieser Befehl eine Kette von acht Übertragungen zwischen dem Speicher und dem DOC. Aus dem On-Chip-SRAM werden sowohl die vier ADC-Ergebnisse als auch ein entsprechender Schwellenwert kopiert, mit dem jedes ADC-Ergebnis verglichen wird (s. Ablaufdiagramm).

Für diesen Anwendungsfall wird der DOC so initialisiert, dass er jeden Wert vergleicht und einen Interrupt erzeugt, wenn einer der Schwellenwerte überschritten wird.

Sobald ADC, DOC und DTC initialisiert sind, wird jeder ADC-Eingang kontinuierlich im Hintergrund überprüft. Die CPU kann andere Aufgaben ausführen oder in den Ruhezustand versetzt werden. Sie wacht erst wieder auf, wenn einer der Eingänge den entsprechenden Wert überschreitet.

Viele andere Low-Level-Aufgaben lassen sich durch die Kombination von DOC und DTC in ähnlicher Weise automatisieren. Dies kann eine äußerst leistungsfähige Technik zur Automatisierung von Low-Level-Funktionen sein. Sie kann Zeit und Kosten bei der Entwicklung von Low-Level-Softwaretreibern sparen sowie die Systemleistung verbessern.

Jeder Mikrocontroller der RA-Familie verfügt über intelligente Peripheriefunktionen wie den DOC und den DTC. Hinzu kommen viele weitere leistungsfähige Peripheriefunktionen, die ebenfalls zur Erstellung intelligenter Subsysteme genutzt werden können. Zusammen bieten der DOC und der DTC hochflexible und leistungsstarke Funktionen zur Automatisierung von Low-Level-E/A-Funktionen in vielen verschiedenen Anwendungen. Die Automatisierung dieser Low-Level-Funktionen verbessert nicht nur die Reaktionszeit des Systems auf Echtzeitereignisse, sondern reduziert auch Komplexität und Umfang der Software. Dies erhöht die Zuverlässigkeit und verringert die Kosten für Systemtests.

Die RA-Mikrocontroller-Familie ist für eine breite Palette von Kommunikations- und Steuerungsanwendungen wie Motorsteuerung, intelligente Sensoren, Metering, Handheld-Instrumente, Low-Power-Modems sowie viele andere Industrie- und Konsumgüter-Anwendungen konzipiert. Sie ist in einer Vielzahl von Speichergrößen und Gehäuseoptionen erhältlich.

Der Autor

Graeme Clark ist Principal Engineer bei Renesas Electronics

- Low Level Tasks automatisiert

- Merkmale des DTC