arm TechCon 2018

arms TrustZone-Technologie bei NXP- und ST-Mikrocontrollern

Die beiden größten 32-bit-MCU-Lizenznehmer von arm, ST Microelectronics und NXP, haben zu arms Entwicklerkonferenz TechCon erste Familien mit arms Cortex-M33-CPU vorgestellt. Die STM32L5x und LPC5500 genannten MCUs unterschieden sich trotz gleicher CPU deutlich.

NXP kombiniert in seinen und in einem 40-nm-Embedded-Flash-Prozess gefertigten LPC-Chips gehärtete Sicherheitssubsysteme und Software in einer sicheren Ausführungsumgebung (Secure Execution Environment, SEE). Die MCUs kommen dazu optional in einer Dual-Core-Ausführung und zielen auf IoT- und Industrie-Anwendungen.

Ein Eckpfeiler zur Etablierung der Zuverlässigkeit von Geräten ist der ROM-basierte sichere Boot-Prozess, der mit Hilfe von geräteeigenen Schlüsseln eine unveränderliche Hardware »root-of-trust« erstellt. Die Schlüssel können nun lokal bei Bedarf durch eine SRAM-basierte Physically-Unclonable-Function (PUF) erzeugt werden, die natürliche Variationen der SRAM-Bitzellen nutzt. Dies ermöglicht Closed-Loop-Transaktionen zwischen dem Endverbraucher und dem OEM und ermöglicht so den Wegfall der Schlüsselbehandlung von Drittanbietern in potenziell unsicheren Umgebungen. Optional können Schlüssel durch eine traditionelle fused-basierende Methode injiziert werden.

Darüber hinaus verbessert die SEE die symmetrische und asymmetrische Kryptographie für Edge-to-Edge- und Cloud-to-Edge-Kommunikation, indem es durch den Einsatz des SRAM-PUF chipindividuelle Geheimschlüssel erzeugt. Die Sicherheit für Public-Key-Infrastructure (PKI) oder asymmetrische Verschlüsselung wird durch den Sicherheitsstandard Device-Identity-Composition-Engine (DICE) gemäß der Definition der Trusted Computing Group (TCG) erhöht. SRAM-PUF gewährleistet die Vertraulichkeit des Unique-Device-Secret (UDS) gemäß den Anforderungen von DICE. Die neu vorgestellten Produkte unterstützen die Beschleunigung für asymmetrische Kryptographie (RSA 1024 auf 4096-Bit-Längen, ECC) sowie bis zu 256-Bit symmetrische Verschlüsselung und Hashing (AES-256 und SHA2-256) mit der mbedTLS-optimierten Bibliothek.

Beschleunigung des maschinellen Lernens und der DSP-Compute-Performance

NXP entschied sich strategisch für Cortex-M33, um die erste vollständige Implementierung der Armv8-M-Architektur zu nutzen und damit Vorteile für die Sicherheitsplattform und erhebliche Leistungssteigerungen im Vergleich zu bestehenden Cortex-M3/M0-MCUs (jeweils über 15 bis 65 Prozent Verbesserung) zu erzielen. Mit dem Cortex-M33 hat arms TrustZone-Technologie Einzug in die Mikrocontroller-Welt gefunden, wir haben die CPU schon ausführlich an dieser Stelle besprochen.

Eines der Hauptmerkmale des Cortex-M33 ist die spezielle Co-Prozessor-Schnittstelle, die die Verarbeitungsfähigkeit der CPU erweitert, indem sie eine effiziente Integration von eng gekoppelten Coprozessoren ermöglicht und gleichzeitig die volle Kompatibilität mit dem Ökosystem und der Toolchain gewährleistet. NXP hat diese Fähigkeit genutzt, um einen Coprozessor zur Beschleunigung wichtiger ML- und DSP-Funktionen wie Faltung, Korrelation, Matrixoperationen, Übertragungsfunktionen und Filterung zu implementieren und die Leistung um das Zehnfache im Vergleich zur Ausführung auf Cortex-M33 zu verbessern. Der Coprozessor nutzt die beliebten CMSIS-DSP-Bibliotheksaufrufe (API) weiter, um die Portabilität von Kundencode zu vereinfachen.

Der Single- oder Dual-Core Cortex-M33 mit integriertem DC-DC-Wandler liefert eine Rechenleistung von bis zu 90 CoreMark/mA. Der große On-Chip-Speicher (bis zu 640 KB Flash und 320 KB SRAM) ermöglicht die Ausführung auch komplexer Edge-Anwendungen. Darüber gibt es eine autonome, programmierbare Logikeinheit (PLU) zum Ausführen von benutzerdefinierten Aufgaben, um die CPU(s) zu entlasten. Sie eignet sich zum Erstellen kleiner kombinatorischer und/oder sequentieller logischer Netzwerke einschließlich Zustandsmaschinen.

Die LPC55S69-Chips nehmen laut NXP im aktiven Modus nur 32 µA/MHz auf (ein Datenblatt lag bei Drucklegung noch nicht vor, daher kann der Betriebspunkt nicht validiert werden, es erscheint schon arg wenig zu sein und passt nicht zu der Angabe von 90 CoreMark/mA). Eine integrierte Power-Management-Unit (PMU) soll zur Minimierung der Stromaufnahme beitragen, es gibt die Low-Power-Modi Sleep, Deep Sleep mit RAM-Speicherung, Abschaltung mit RAM-Speicherung und Speicherung des CPU-0-Status sowie eine totale Abschaltung der Spannungsversorgung. Der Micro-Tick-Timer, der vom Watchdog-Oszillator aus läuft, und die Echtzeituhr (RTC), die vom 32.678 kHz Taktgeber aus läuft, können verwendet werden, um die MCU aus dem Ruhe- und Tiefschlafmodus zu wecken.

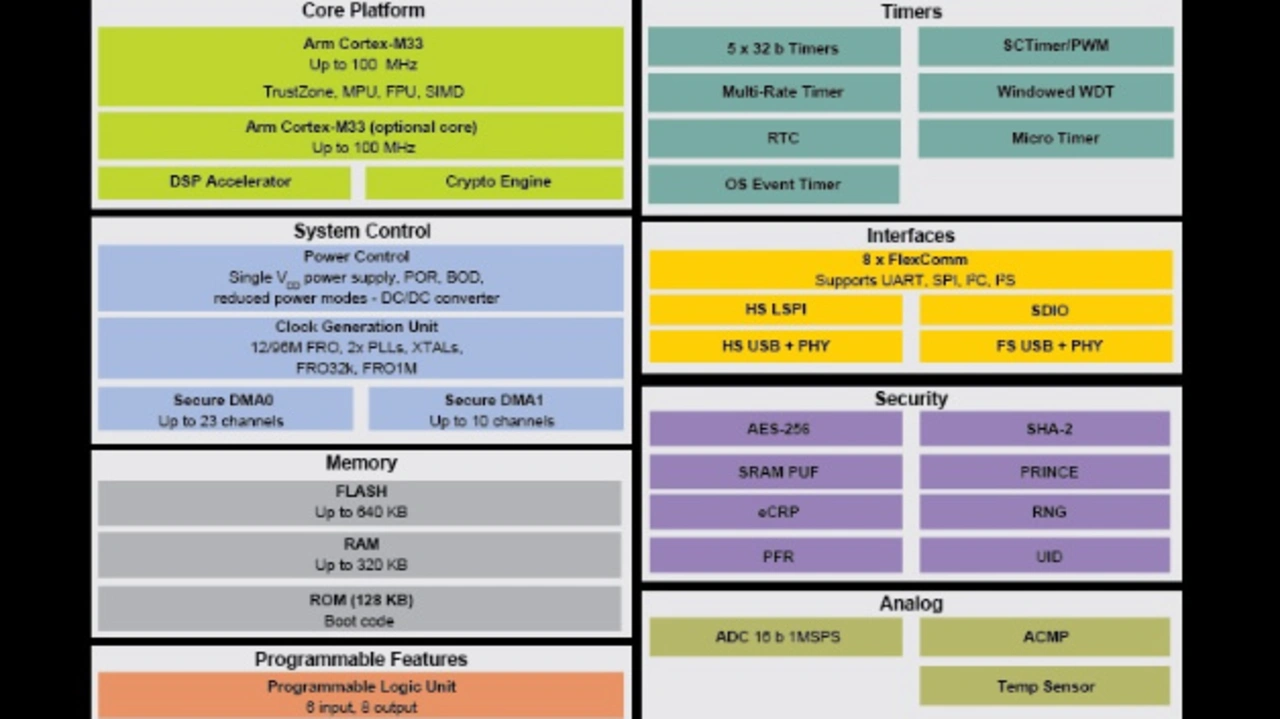

Bild 1 zeigt das Blockdiagramm des LPC55S69. Zu der zweiten CPU in einer Dual-Core-Konfiguration ist zu sagen, dass diese ebenfalls mit einer Frequenz von bis zu 100 MHz betrieben werden kann, aber anders als der erste Core keine MPU, FPU, DSP, ETM und TrustZone-Implementierung beinhaltet. Der On-Chip-Flash-Programmspeicher ist über einen Cache angebunden und die 320 KB SRAM bestehen aus 288 KB, die am Systembus angebunden sind, und 32 KB, die direkt am CPU-Bus hängen. Die PUF nutzt speziellen SRAM für den Silizium-Fingerprint. PUF kann Schlüsselgrößen von 64 bis 4096 Bit erzeugen, speichern und rekonstruieren und enthält entsprechende Hardware für die Schlüsselextraktion.

An digitaler Peripherie gibt es abhängig von der Familie einen DMA-Controller mit 30 Kanälen und bis zu 24 programmierbaren Triggern, der auf alle Speicher und DMA-fähige Peripherien zugreifen kann; einen LCD-Controller, der sowohl Super-Twisted-Nematic (STN) als auch Thin-Film-Transistor-Displays (TFT) unterstützt. Es verfügt über einen dedizierten DMA-Controller, eine wählbare Bildschirmauflösung (bis zu 1024 × 768 Pixel) und unterstützt bis zu 24 Bit Echtfarbenmodus; der Controller für externen Speicher (EMC) bietet Unterstützung für asynchrone statische Speicher wie RAM, ROM und Flash sowie dynamische Speicher wie SDRAM mit einer Taktfrequenz von bis zu 100 MHz; SD/MMC und SDIO mit DMA-Unterstützung. Die CRC-Engine kann eine Prüfsumme aus den gelieferten Daten berechnen, indem sie mit DMA-Unterstützung eines von drei Standardpolynomen verwendet; bis zu 171 GPIO-Pins, wobei sich GPIO-Register für einen schnellen Zugriff auf dem AHB befinden. Bis zu acht GPIOs können als Pin Interrupts (PINT) ausgewählt werden, ausgelöst durch steigende, fallende oder beide Eingangsflanken. Zwei GPIO-Grouped-Interrupts (GINT) ermöglichen einen Interrupt basierend auf einer logischen (UND/OR) Kombination von Eingangszuständen.

An analoger Peripherie gibt es einen 16-Bit-A/D-Wandler mit fünf differentiellen Kanalpaaren (oder 10 Single-Ended-Kanälen) und mit mehreren internen und externen Triggereingaben und Abtastraten von bis zu 1,0 MSamples/s. Der Wandler unterstützt zwei unabhängige Konvertierungssequenzen. An ihn angeschlossen ist ein integrierter Temperatursensor. Weiterhin gibt es einen Komparator mit fünf Eingangspins und externer oder interner Referenzspannung.

Last but not least gibt es noch serielle Schnittstellen wie die Flexcomm-Schnittstelle, die bis zu neun serielle Peripherien abbilden kann. Jede Flexcomm-Schnittstelle kann per Software als USART-, SPI-, I2C- und I2S-Schnittstelle ausgewählt werden. I2C-Bus-Schnittstellen unterstützen Fast-Mode und Fast-Mode Plus mit Datenraten von bis zu 1 Mbit/s und mit Mehrfachadressenerkennung.

Der USB-2.0-Full-Speed-Host/Device-Controller mit On-Chip-PHY und dediziertem DMA-Controller unterstützt den quarzlosen Betrieb im Device-Modus, der USB-2.0-Hochgeschwindigkeits-Host/Device-Controller enthält On-Chip-Hochgeschwindigkeits-PHY.

Die MCU-Serie LPC5500 bietet Pin-, Software- und Peripheriekompatibilität in sieben verschiedenen Familien mit unterschiedlichem Funktionsumfang. Die Versorgungsspannung kann zwischen 1,8 V und 3,6 V liegen, der Betriebstemperaturbereich beträgt -40 °C bis +105 °C. Verfügbar sind die Chips in den Gehäusen HLQFP100, VFBGA98 und HTQFP64.

Entwicklungsunterstützung und Produkteinführung

Für die erste Familie gibt es das Entwicklungs-Kit LPC55S69-EVK, ein Evaluierungsboard, das von NXPs MCUXpresso Integrated Development Environment (IDE) und einem umfassenden Softwareentwicklungskit unterstützt wird, das Peripherietreiber, Sicherheits- und Konnektivitäts-Middleware, Amazon FreeRTOS-basierte Demos und arms trustzone-basierte Sicherheitsbeispiele enthält.

Um den Entwicklungsaufwand weiter zu reduzieren, enthält MCUXpresso eine Reihe von Konfigurationstools - Pins, Uhren und Peripheriegeräte. Weitere Sicherheitstools sind unter anderem das hostseitige Tool zum Erstellen und Signieren eines sicheren Flash-Images, die Flash-Programmierung mit SRAM-PUF-Key-Provisioning und der Generator für sichere Debug-Zertifikate. Tools gibt es von arm (Keil MDK), IAR, Segger und anderen.

NXP bemustert derzeit LPC55S69 Entwicklungsboards und 100-Pin-LQFP-Pakete mit zugehörigem MCUXpresso-basiertem Softwareentwicklungskit. Die Massenproduktion beginnt im 1. Quartal 2019. Die LPC55S6x-Familie hat einen Stückpreis von 1,99 US$ für 256 KB Flash und 2,49 US$ für 640 KB Flash (in 10.000 Stückzahlen).

Offenlegung: DESIGN&ELEKTRONIK hat auf Einladung von arm an der TechCon in San Jose teilgenommen, die Reisekosten wurden zur Gänze von arm bezahlt. Unsere Berichterstattung ist davon nicht beeinflusst und bleibt gewohnt neutral und kritisch. Der Artikel ist, wie alle anderen auf unserem Portal, unabhängig verfasst und unterliegt keinerlei Vorgaben seitens Dritter.

Jobangebote+ passend zum Thema

- arms TrustZone-Technologie bei NXP- und ST-Mikrocontrollern

- Neue STM32-MCUs in zwei Varianten