arm TechCon 2018

arms TrustZone-Technologie bei NXP- und ST-Mikrocontrollern

Fortsetzung des Artikels von Teil 1

Neue STM32-MCUs in zwei Varianten

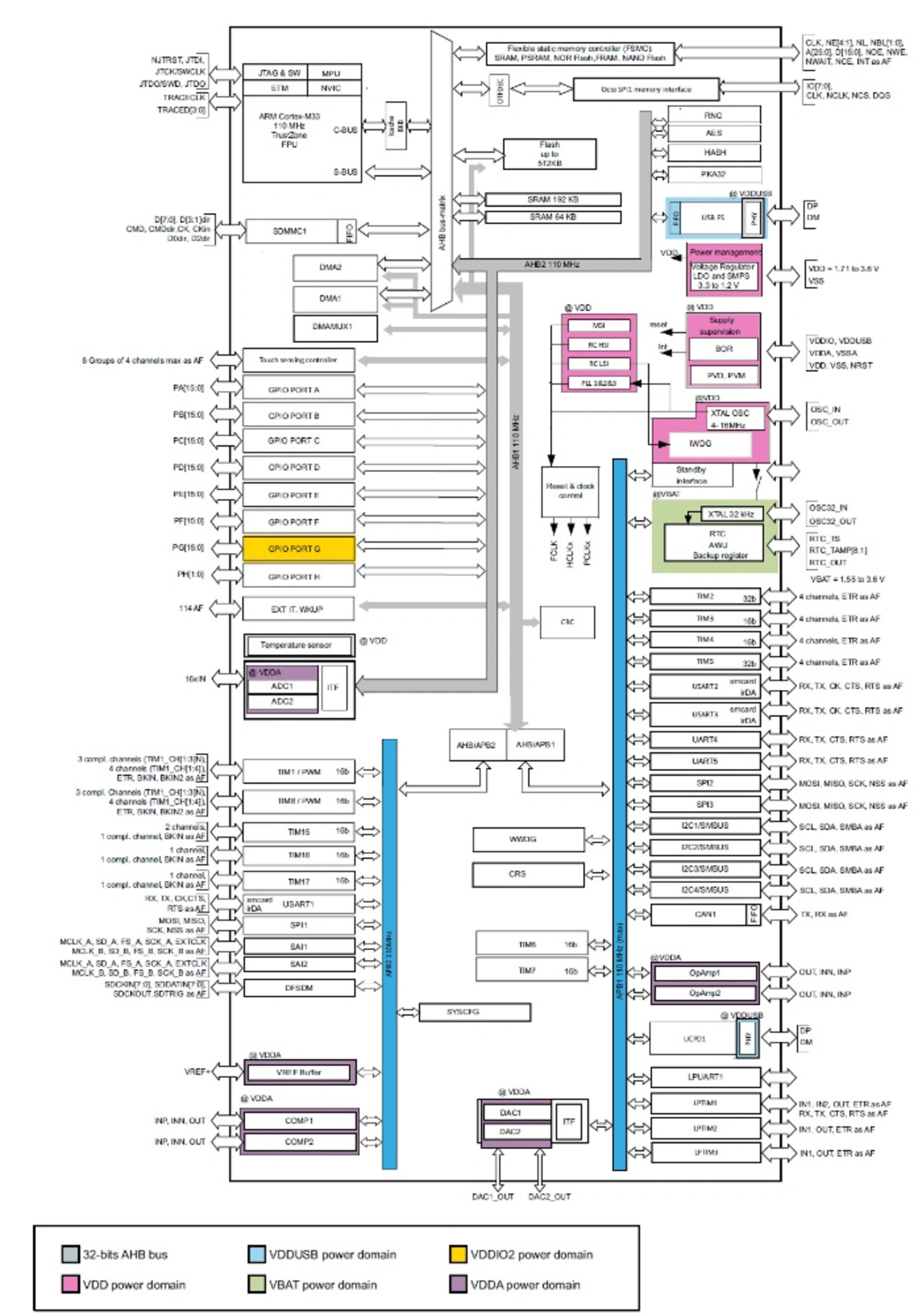

Nach Microchip und NXP stellte nun auch ST Microelectronics seine ersten Mikrocontroller-Familien mit arms Cortex-M33-CPU vor. Die STM32L552 und STM32L562 genannten Familien sollen neben Sicherheit vor allen Dingen auch mit Energieeffizienz punkten. Der Coretx-M33 ist hier als Single-Core implementiert und wird mit 110 MHz getaktet, angeboten werden bis zu 512 KB Flash, der entweder als Single- oder Dual-Bank konfiguriert werden kann. In letzterer Option ist es möglich, aus einer Bank daten zu lesen und gleichzeitig die andere Bank zu löschen oder zu beschreiben. An SRAM sind 256 KB verfügbar, davon 64 KB mit Hardware-Paritätsüberprüfung. Dieser Block ist für eine maximale Geschwindigkeit der Datenübertragung auch direkt an den C-Bus angebunden, was aus dem Blockdiagramm (Bild 2) nicht unmittelbar hervorgeht. Im Standby-Modus kann man auswählen, ob die Daten in 4 KB oder 64 KB SRAM erhalten bleiben sollen.

Mit einer Rechenleistung von 427 CoreMark bei 100 MHz Taktfrequenz in dem entsprechenden EEMBC-Benchmark erzielen die neuen Familien, die sich durch das Vorhandensein einer Krypto-Engine unterscheiden, einen neuen Rekordwert bei STs STM32L-Familien. Bislang stand der L4+ mit 409 CoreMark an der Spitze. Bei einem weiteren Benchmark, dem ULP-CP wird bei 1,8 V Versorgungsspannung ein Wert von 402 erreicht, was im ST-Universum ebenfalls ein neuer Höchstwert ist und sogar leicht Microchips SAML11 (Score 400) übertrifft, der auf arms Cortex-M23-CPU basiert und mit 32 MHz Taktfrequenz hinsichtlich der Rechenleistung nicht mit den neuen ST-Devices konkurrieren kann. Im ULPMark-PP wird ein Score von 59,5 erreicht, was unterhalb des STM32L433 liegt (70,6).

Angegeben werden soll auch ein Wert für den neuesten EEMBC-Benchmark, den sogenannten SecureMark-TLS. Dieser analysiert den Energieverbrauch, der mit der Implementierung von TLS auf einem Edge-Gerät unter Verwendung einer gemeinsamen IoT-Ciphersuite, bestehend aus ECC und ECDSA auf der NIST-secp256r1-Kurve, SHA256 und AES128-CCM/ECB, einhergeht. Er bietet ein von der Industrie entwickeltes und standardisiertes Werkzeug für Anwendungsentwickler zur Analyse von Sicherheitsimplementierungen und misst Rechenleistung, Energieverbrauch und Leistungsaufnahme. Geprüft wird die Kombination aus Mikrocontroller, Hardware- und/oder Software-Sicherheitsprodukten und Compileroptionen (Codegröße vs. Geschwindigkeit). Während der STM32L476 auf einen SecureMark-Score von 4360 kommt, schätzt ST den neuen STM32L5 auf mindestens 28000 Punkte. Dieser große Unterschied kommt durch die später beschriebene neue Hardware-Krypto-Engine zustande, die dem L4 abgeht.

Im Gegensatz zu den NXP-Produkten lag uns zur Drucklegung von ST bereits ein (unvollständiges) Datenblatt vor, sodass wir insbesondere hinsichtlich des Energieverbrauchs genauere Angaben für die unterschiedlichen Betriebsmodi machen können.

Im aktiven Modus bewegt sich die Stromaufnahme bei 3 V Versorgungsspannung zwischen 60 µA/MHz (SMPS-Abwärtswandler-Betrieb) und 96 µA/Mhz bei Betrieb an einem Linearregler (LDO).

Die fünf Energiesparmodi nehmen zwischen 33 nA (Shut-Down, Aufwecken der MCU über fünf Pins möglich) und 2,5 µA (Stop-Modus 2 mit Echtzeituhr). Ein Aufwecken der MCU aus dem Stop-Modus soll übrigens in nur 5 µs erfolgen, für die anderen Modi sind (noch) keine Werte vorhanden.

Wie üblich hat ST auch bei seinen neuen Controllern den ART-Beschleuniger implementiert, ein 8 Kbyte großer Befehls-Cache, der bei Cache-Treffern eine 0-Waitstate-Operation der CPU bei Codeausführung sowohl aus dem Flash als auch aus externem Speicher erlaubt. Der externe Speichercontroller unterstützt SRAM, PSRAM, NOR, NAND und FRAM. Dazu gibt es noch eine OctoSPI-Speicherschnittstelle, die Single-, Dual-, Quad- oder Octal-SPI-Speicher bedienen kann.

Optionaler Verschlüsselungsblock on Chip

Der STM32L562 kommt im Gegensatz zum STM32L5xx mit einem umfangreichen Hardware-Verschlüsselungsblock daher. Neben einem Zufallsgenerator ist ein AES-Hardwarebeschleuniger zu nennen, der sowohl zum Verschlüsseln als auch zum Entschlüsseln von Daten mit einem AES-Algorithmus genutzt werden kann und 128/256 bit lange Schlüssel verwenden kann. Unterstützt wird die Verschlüsselung/Entschlüsselung mittels AES-Rijndael-Blockverschlüsselungsalgorithmus und einer NIST-FIPS-197-konformen Implementierung des AES-Verschlüsselungs-/Entschlüsselungsalgorithmus.

Der Hash-Prozessor ist eine vollständig konforme Implementierung des sicheren Hash-Algorithmus (SHA-1, SHA-224, SHA-256), des MD5 (message-digest algorithm 5) Hash-Algorithmus und des HMAC (Keyed-Hash Message Authentisierungscode) Algorithmus, der für eine Vielzahl von Anwendungen geeignet ist.

Der Public-Key-Beschleuniger (PKA) ist für die Berechnung von kryptographischen öffentlichen Schlüsseln vorgesehen, insbesondere solche, die mit RSA, Diffie-Hellmann oder ECC zusammenhängen (elliptische Kurve Kryptographie) über GF(p) (Galoisfelder). Um einen hohen Durchsatz zu einem vernünftigen Preis zu erreichen, werden diese Operationen in der Montgomery-Domäne ausgeführt.

Das eingebettete OTFDEC entschlüsselt in Echtzeit die verschlüsselten Inhalte, die in externen OctoSPI-Speichern, die im Memory-mapped-Modus verwendet werden, liegen. Das OTFDEC verwendet den AES-128-Algorithmus im Counter-Modus (CTR). Codeausführung auf externen OctoSPI-Speichern kann dank STMicroelectronics proprietärer Minicipher gegen Fehlerinjektion geschützt werden.

An analoger und digitaler Peripherie mangelt es den neuen ST-Chips nicht. Ein USB-FS-Controller, zwei SAIs (serielle Audio-Schnittstelle), vier I2C FM+(1 Mbit/s), SMBus/PMBus, sechs USARTs (ISO 7816, LIN, IrDA, Modem), drei SPIs (5 mal SPIs mit dem Dual OctoSPI), CAN FD, SDMMC-Schnittstelle stehen ebenso zur Verfügung wie zwei DMA-Controller mit 14 Kanälen.

Für Touch stehen bis zu 24 kapazitive Abtastkanäle zur Verfügung, die Tasten sowie lineare und Drehbewegungen erfassen können. Bis zu drei kapazitive Abtastkanäle können für eine kurze Ansprechzeit parallel erfasst werden.

An analoger Peripherie sind zwei 12-Bit-A/D-Wandler mit einer Abtastrate von bis zu 5 MSamples/s implementiert, mit Oversampling können bis zu 16 Bit aufgelöst werden. Der Wandler ist mit 200 μA/MSample sehr energieeffizient. Zwei 12-bit-D/A-Wandler , zwei Operationsverstärker mit integriertem PGA, zwei Komparatoren mit extrem niedriger Leistungsaufnahme und vier digitale Filter für den Sigma-Delta-Modulator ergänzen das Angebot.

An I/Os stehen je nach Derivat bis zu 114 mit Interruptfunktion, die meisten 5-V-tolerant und bis zu 14 I/Os mit einer unabhängige Versorgungsspannung bis zu 1,08 V zur Verfügung.

Die Versorgungsspannung des Chips reicht von 1,71 V bis 3,6 V, die Betriebstemperatur von -40 °C bis 85/125 °C. Als Gehäuse werden die Ausführungen LQFP48/64/100/144 und UFQFPN48, UFBGA132 und WLCSP81 angeboten (letzteres 2,578 × 1,1716 mm groß). Einen Preis hat ST bis Drucklegung nicht genannt.

Fazit

Fast zeitgleich stellen arms größte MCU-Lizenznehmer neue Mikrocontroller mit Cortex-M33-CPU(s) vor. NXP bietet exklusiv eine Dual-Core-Variante in einer 40-nm-Fertigung mit einer PUF an, ST ist mit seinen STM32-MCUs unangefochtener Marktführer bei den arm-32-bit-Controllern und hat eine neue leistungsfähige Krypto-Engine entwickelt. Viel Peripherie bieten beide, am Ende werden die applikationsspezifischen Bedürfnisse, Skalierbarkeit und vermutlich neben dem Preis das Ecosystem, indem man schon entwickelt, den Ausschlag geben. Der Cortex-M33 mit seiner TrustZone-Technologie bietet gegenüber den herkömmlichen CPUs Cortex-M0+/M3/M4 ein Quantensprung an Sicherheitszuwachs, sodass jeder ernsthafte IoT-Entwickler an dem einen oder anderen M33-Chip schwer vorbeikommen dürfte.

Jobangebote+ passend zum Thema

- arms TrustZone-Technologie bei NXP- und ST-Mikrocontrollern

- Neue STM32-MCUs in zwei Varianten