IEDM 2019

»Die Skalierung geht mindestens zehn Jahre weiter«

Fortsetzung des Artikels von Teil 2

Ganzheitliche Lithographie

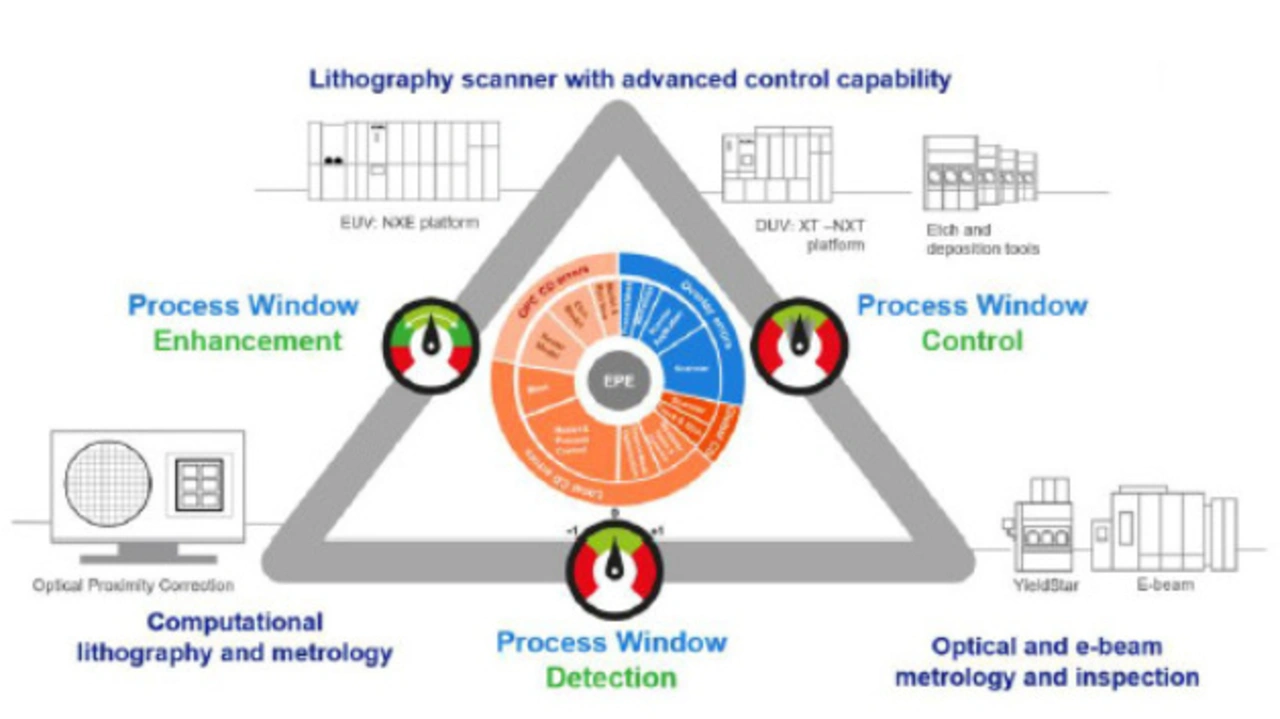

Neben der EUV-Lithographie verfeinert ASML das DUV-Lithografie-Angebot weiter, da die Kunden bei mehr als 80 % ihrer Lithographie-Ebenen weiterhin mit DUV bestreiten. Neben der feinen Auflösung, die durch die gemeinsamen Fähigkeiten von Belichtungswerkzeugen, Fotolack und Maske erreicht wird, können funktionstüchtige Chips nur mit einer exakt aufeinander abgestimmten Abfolge von lithographischen Schichten gebaut werden, von denen Kantenplatzierungsfehler (EPE) eine der wichtigsten Metriken sind.

Zu den Verursachern von EPE zählen Fehler durch die optische Nahfeldkorrektur (OPC), Overlay-Fehler durch das Belichtungswerkzeug, globale und lokale CD-Fehler (Critical Dimension) und die Praxis der ganzheitlichen Lithographie. So kann beispielsweise die lokale CD-Gleichmäßigkeit durch ein größeres Prozessfenster verbessert werden, was durch die Optimierung der Beleuchtung und der Strukturen auf der Maske erreicht werden kann. Mit Deep-Learning-basiertem OPC ist es möglich, genauere Sub-Resolution Assist Features (SRAF) auf der Maske zu platzieren. Dies führt zu einem niedrigeren EPE aufgrund einer besseren CD-Gleichförmigkeit als Folge eines größeren Prozessfensters.

Jobangebote+ passend zum Thema

Die EPE wird auch durch eine Reduzierung des Effekts aufgrund der bereits erwähnten dreidimensionalen Natur der EUV-Maske reduziert. Dieser Masken-3D-Effekt führt zu einem reduzierten Bildkontrast, was wiederum zu einer verschlechterten CD-Gleichmäßigkeit führt. ASMLs Studie kommt zu dem Schluss, dass der Masken-3D-Effekt durch die Verwendung von abgeschwächten Phasenverschiebungsmasken (attPSM) reduziert werden kann. Konkret erreicht attPSM dieses Ziel, indem es eine ausgewogenere Energieverteilung in der nullten und ersten gebeugten Ordnung aufweist und gleichzeitig deren Phasendifferenz minimiert. Auch eine robuste Messtechnik muss Teil dieses Prozesses sein. Schließlich muss die Metrologie zur Inspektion von Defekten, insbesondere auf EUV-belichteten Wafern, entsprechend vorangetrieben werden, da die Halbleiterfertigung auf Sub-10-nm-Generationen voranschreitet. Durch die Auflösung begrenzt, wird die optische Inspektion schließlich mehreren Elektronenstrahlinspektionen weichen. Bei ASML befindet sich derzeit ein Mehrstrahl-Inspektionssystem in Entwicklung, das die erforderliche Empfindlichkeit mit einem produktionsreifen Durchsatz kombiniert.

Langfristige Perspektive der Lithographie

Über die High-NA-EUV-Lithographie und über das nächste Jahrzehnt hinaus kann eine weitere physische Skalierung in der Ebene durch zunehmende Komplexität auf Transistor- und Systemebene in Frage gestellt werden. So kann beispielsweise ein dielektrischer Durchschlag auftreten, wenn der Metall-Pitch 10 nm unterschreitet. Darüber hinaus können sich die Produktionsanlagen zu einer Komplexität entwickeln, die kein gesundes Ökosystem mehr zulassen. Im Falle einer Verlangsamung der physikalischen 2D-Skalierung werden sich die Integration und Dichte der Transistorstrukturen jedoch noch lange Zeit weiter verbessern. Dies steht im Einklang mit den Treibern, die Gordon Moore frühzeitig identifiziert hat. In seinem IEEE-Papier von 1975 sagte er: »Der Beitrag von Transistor- und Schaltungsfortschritten (....) war wichtiger als entweder eine größere Chip-Fläche oder feinere Linien«. Die Fortschritte in diesen Bereichen, die wir heute Architekturskalierung, Schaltungsskalierung und Transistorskalierung (Layout) nennen, werden fortgesetzt und durch die extrem niedrigen Kosten pro Transistor unterstützt. Dies wird das Design-In zusätzlicher Funktionen fördern und Anwendungsinnovationen freisetzen. Heute ist dieser Trend in der Stapelung von Transistorstrukturen in der dritten Dimension sichtbar, wie z.B. bereits eine Form des 3D-Stapelns in Intels FOVEROS-Packaging zu beobachten ist. Dennoch wird die Lithographie gefordert, um Lösungen sowohl in reifen als auch in fortgeschrittenen Knoten zu finden. Wie kann man zum Beispiel eine dünne Scheibe eines bereits bearbeiteten Siliziumwafers auf einem stark verzogenen Substrat mit Nanometergenauigkeit überlagern? Bei ASML glaubt man daran, dass es Lösungen geben wird. Damit die Chipdichte weiter ansteigt, benötigen die meisten Schichten im Stapel die feinste Lithographie, vielleicht über die heutigen Mindestgeometrien hinaus.

- »Die Skalierung geht mindestens zehn Jahre weiter«

- EUV-Lithographie und High-NA-Systeme

- Ganzheitliche Lithographie