KU Leuven und imec

Mit »Schaumstoff« zu kleineren, leistungsfähigeren Chips

Belgische Forscher haben eine neue Technik zur Isolierung von Mikrochips entwickelt. Sie verwenden metallorganische Gerüste, die aus strukturierten Nanoporen bestehen. Langfristig soll dies zu noch kleineren und leistungsfähigeren Chips führen, die weniger Energie benötigen.

Über eine Milliarde Transistoren können heutzutage auf einem Mikrochip verteilt sein. Da diese Schalter und die Leitungen extrem dicht gepackt sind, werden auch die Anforderungen an die Isolierung, die diese Leitungen voneinander trennen soll, immer höher. Auf nanoskaliger Ebene ist dies nicht einfach umzusetzen.

Eine Studie, die Professor Rob Ameloot vom Institut für mikrobielle und molekulare Systeme der Katholischen Universität Leuven leitete, hat einen neuen Weg zur Lösung dieser Herausforderung aufgezeigt. »Als Isoliermaterial verwenden wir metallorganische Gerüstverbindungen (Metal-Organic Frameworks, MOFs)«, erklärt Ameloot. »Diese Werkstoffe bestehen aus Metallionen und organischen Molekülen, die zusammen einen Kristall bilden, der porös und dennoch stabil ist.«

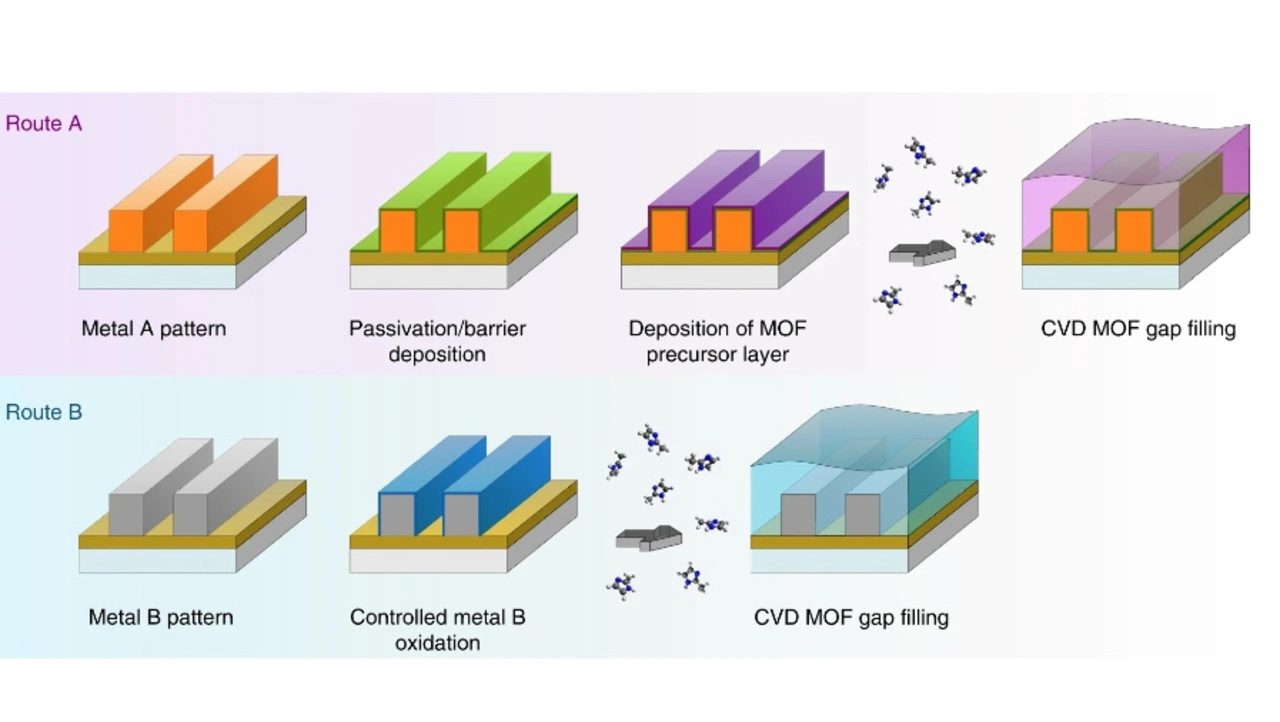

Im Rahmen dieser Studie gelang es dem Forschungsteam gemeinsam mit dem Forschungszentrum Imec, eine MOF-Isolierung auf Elektronikmaterial aufzubringen. Dazu nutzen sie die chemische Gasphasenabscheidung (Chemical Vapour Deposition), erläutert Mikhail Krishtab, Postdoktorand am Institut für mikrobielle und molekulare Systeme und Erstautor der Studie. »Zuerst legten wir einen Oxidfilm über die Oberfläche. Dann ließen wir es mit dem gasförmigen organischen Material reagieren. Dadurch quillt es zu einem hochporösen MOF-Material auf – ähnlich einem Soufflé, das im Ofen aufgeht.«

Jobangebote+ passend zum Thema

»Der wesentliche Vorteil dieser Methode ist, dass sie von unten nach oben erfolgt«, erklärt Krishtab. Das MOF-Material füllt sämtliche Lücken zwischen den Leitern aus, sodass sichergestellt ist, dass diese vollständig und homogen isoliert sind. Bei anderen Methoden, die von oben nach unten erfolgen, bestehe laut Krishtab immer das Restrisiko, dass kleine Spalten in der Isolierung verbleiben.

Die Forschungsgruppe von Professor Ameloot hat einen Proof-of-Concept-Zuschuss des ERC erhalten, um die Technik in Zusammenarbeit mit Silvia Armini aus dem Team des Imec weiterzuentwickeln. Das Imec hat die Aufgabe, solche Technologien vom Labor in die Fabrik zu überführen und den Weg hin zu einer produktionsreifen Lösung für die Mikroelektronikbranche zu ebnen.

»Wir konnten zeigen, dass das MOF-Material die erforderlichen Eigenschaften hat«, so Ameloot weiter. »Jetzt müssen wir noch die Oberfläche feinabstimmen. Derzeit ist die Oberfläche der Kristalle noch unregelmäßig. Um das Material in einen Chip integrieren zu können, müssen wir die Oberfläche glätten.«

Originalpublikation

M. Krishtab, et al., Vapor-deposited zeolitic imidazolate frameworks as gap-filling ultra-low-k dielectrics, Nature Communications 10, 3729 (2019).