Pre-Silicon-Verifikation

Höhere Kapazität und Leistung

Mit der neuen Generation – Palladium Z2 und Protium X2 – verdoppelt Cadence die Kapazität und steigert die Leistung um 50 Prozent gegenüber seinen vorhergehenden Systemen für Hardware-Debugging und Software-Validierung.

Mit der Weiterentwicklung seiner Palladium Z1 Emulations- und Protium X1 Prototyping-Systemen reagiert Cadence auf die exponentiell zunehmende Komplexität bei der SoC-Entwicklung und den weiter steigenden Zeitdruck für die Markteinführung neuer Bausteine. Die neue Generation Palladium Z2 Enterprise Emulation und Protium X2 Enterprise Prototyping bieten einen höcheren Durchsatz beim Pre-Silicon-Hardware-Debugging und der Pre-Silicon-Software-Validierung selbst bei großen System-on-Chip-Entwürfen mit mehreren Milliarden Gattern.

Auf Grund der engen Integration mit einheitlichen Compilern und Schnittstellen nennt Cadence diese beiden Systeme auch »Dynamic Duo«. Die darin enthaltenen Emulations-Prozessoren und FPGAs (UltraScale+ VU19P von Xilinx) bieten gegenüber den Vorgängerversionen Z1 und X1 die doppelte Kapazität und eine um den Faktor 1,5 höhere Leistung. Dadurch lassen sich mehr Validierungszyklen bei größeren SoCs in kürzerer Zeit ausführen. Zusätzlich bieten beide Systeme eine modulare Compiler-Technik, die bis zu 10 Mrd. Gatter in weniger als 10 h auf dem Palladium-Z2-System und in weniger als 24 h auf dem Protium-X2-System compilieren kann.

Das Dynamic Duo mit Palladium Z2 und Protium X2 wurde speziell im Hinblick auf die Herausforderungen beim Entwurf von SoCs für fortschrittliche Anwendungen, wie für den Mobilfunk-, PC- und Hyperscale-Computer-Bereich entwickelt. Mit einem nahtlos integrierten Prozess, einheitlicher Debugging-Umgebung sowie gleichen virtuellen und physikalischen Schnittstellen und systemunabhängig nutzbarer Testinhalte, ermöglicht das Dynamic Duo das schnelle Portieren und Testen von SoC-Entwürfen, von der Emulation bis zum Prototyping.

Jobangebote+ passend zum Thema

»Die Komplexität unserer Highend-Grafik- und Hyperscale-Entwürfe nimmt mit jeder Generation zu, wogegen unsere Time-to-Market-Pläne immer mehr unter Druck geraten«, sagt Narendra Konda, Senior Director, Hardware Engineering der NVIDIA Corporation. »Durch den einheitlichen Eingangsprozess der Palladium-Z2- und Protium-X2-Systeme von Cadence können wir die Arbeitslast für Verifikation, Validierung und Pre-Silicon-Software-Vorbereitung optimal verteilen.«

»Für den Erfolg von AMD ist es entscheidend, dass wir unseren Chip-Entwicklungsprozess beschleunigen und unsere Shift-Left-Strategie optimieren können«, sagt Alex Starr, Corporate Fellow, Methodology Architect bei AMD. »Durch die höhere Leistung der Palladium-Z2- und Protium-X2-Systeme von Cadence können wir den Pre-Silicon-Durchsatz erhöhen und gleichzeitig die funktionalle Kongruenz zwischen Emulation und Prototyping weiter gewährleisten. Kurze Vorbereitungszeiten und schnelle Übergänge von der Palladium-Z2-Emulation auf das Protium-X2-Prototyping möglichen uns eine weitere Optimierung unserer Shift-Left-Strategie für unsere hochkomplexen SoCs.«

»Die Pre-Silicon-Verifikation von fortschrittlichen SoCs erfordert ein System mit einer Kapazität von mehreren Milliarden Gattern, die sowohl höchste Leistung als auch schnelles voraussagbares Debugging bietet«, sagt Paul Cunningham, Senior Vice President und General Manager der System & Verification Group von Cadence. »Unser neues Dynamic Duo erfüllt diese Anforderungen mit zwei voll integrierten Systemen. Palladium-Z2-Emulation ist für ein schnelles voraussagbares Hardware-Debugging und Protium-X2-Prototyping für eine höchste Performance bei der Software-Validierung von mehreren Milliarden Gattern optimiert. Wir sind über das starke Kundeninteresse begeistert und wir freuen uns auf die Zusammenarbeit beim Einsatz dieser neuen Systeme, um unseren Kunden einen höchsten Verifikationsdurchsatz bei ihren Designs zu ermöglichen.«

»ARM nutzt die Emulation zusammen mit der Simulation auf Arm-basierten Servern sehr ausgiebig, um einen höchstmöglichen Verifikationsdurchsatz zu erreichen«, sagt Tran Nguyen, Senior Director of Design Services bei ARM. »Mit dem neuen Cadence-Palladium-Z2-System erreichen wir eine Leistungsverbesserung von bis zu 50 Prozent und eine Verdoppelung der Kapazität bei unseren neuesten Entwürfen. Damit stehen uns die leistungsfähigen Pre-Silicon-Debugging-Fähigkeiten zur Verfügung, die wir für die Verifikation unserer IP und Produkte der nächsten Generation benötigen.«

»Xilinx und Cadence haben sehr eng zusammengearbeitet, um zu gewährleisten, dass der Software-Eingang von Cadence nahtlos mit der Ausgabe der Xilinx-Vivado-Design-Suite funktioniert, was optimale Leistung und Kapazitätsvorteile ermöglicht«, sagt Hanneke Krekels, Senior Director, Core Vertical Markets, bei Xilinx Inc. »Das Cadence-Protium-X2-Enterprise-Prototyping-System wurde entwickelt, um eine Multi-MHz-Leistung für Entwürfe mit einer Milliarde Gattern mit unseren Virtex-UltraScale+-VU19P-Bauteilen erreichen zu können. Der voll integrierte Cadence/Xilinx-Front-to-Back-Flow erlaubt den Softwareentwicklern einen extrem frühzeitigen Einsatz der Plattform im Entwicklungsprozess und eine Konzentration auf die Entwurfsvalidierung und Softwareentwicklung anstatt auf die Prototypenvorbereitung.«

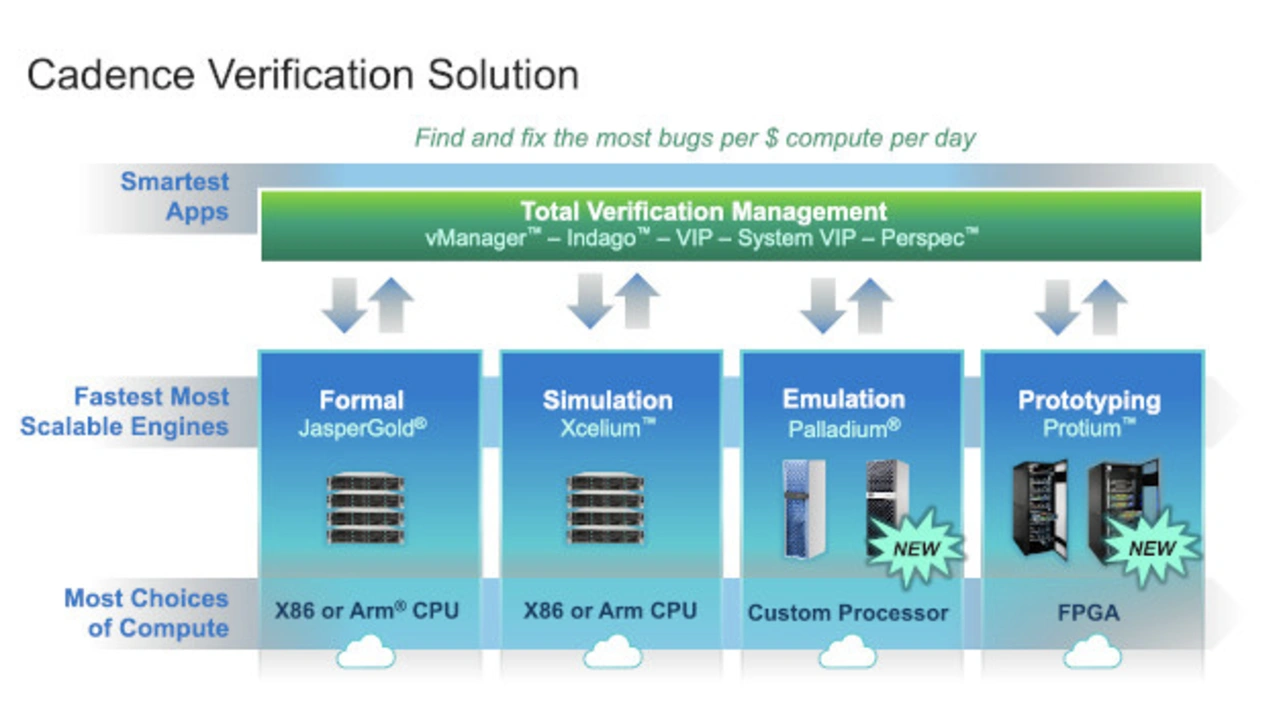

Die Cadence Full Flow Verification, einschließlich Palladium-Z2-Emulation, Protium-X2-Prototyping, Xcelium Logic Simulation, JasperGold Formal Verification Platform und der Cadence-Suite mit intelligenten Verifikationsanwendungen, ermöglicht den höchsten Verifikationsdurchsatz von Fehlern pro Dollar pro Tag. Die neuen Palladium-Z2- und Protium-X2-Systeme sind Teil der umfassenden Cadence Verification Suite und unterstützen die Intelligent System Design Strategie des Unternehmens. Palladium-Z2- und Protium-X2-Systeme sind bereits bei einigen Kunden im Einsatz und werden ab Q2/2021 allgemein erhältlich sein.