Universität Pisa / Picosun

1 µF/mm² bei in Silizium integrierte Mikrokondensatoren

Wie Forscher der Universität Pisa berichten, haben sie mithilfe der weitverbreiteten ALD-Technik (Atomic Layer Deposition) von Picosun in Siliziumwafer Deep-Trench-Mikrokondensatoren integriert. Diese erreichen eine flächenbezogene Kapazität von 1 µF/mm².

Steigende Forderungen an Wirkungsgrad und Leistungsfähigkeit portabler Elektronik und von Wearables sowie deren Schrumpfung nach dem Mooreschen Gesetz stellen auch das Powermanagement solcher Systeme vor neue Herausforderungen. Ein Lösungsansatz besteht darin, die Schlüsselkomponenten solcher Systeme in das gleiche Gehäuse (Systems in Package, SiP) oder auf den gleichen Chip (Systems on Chip, SoC) zu integrieren. Dabei bringt man alle Komponenten – einschließlich der Energiespeicher wie Batterien oder Kondensatoren – in eine einzelne, mikroskopisch kleine Baugruppe unter.

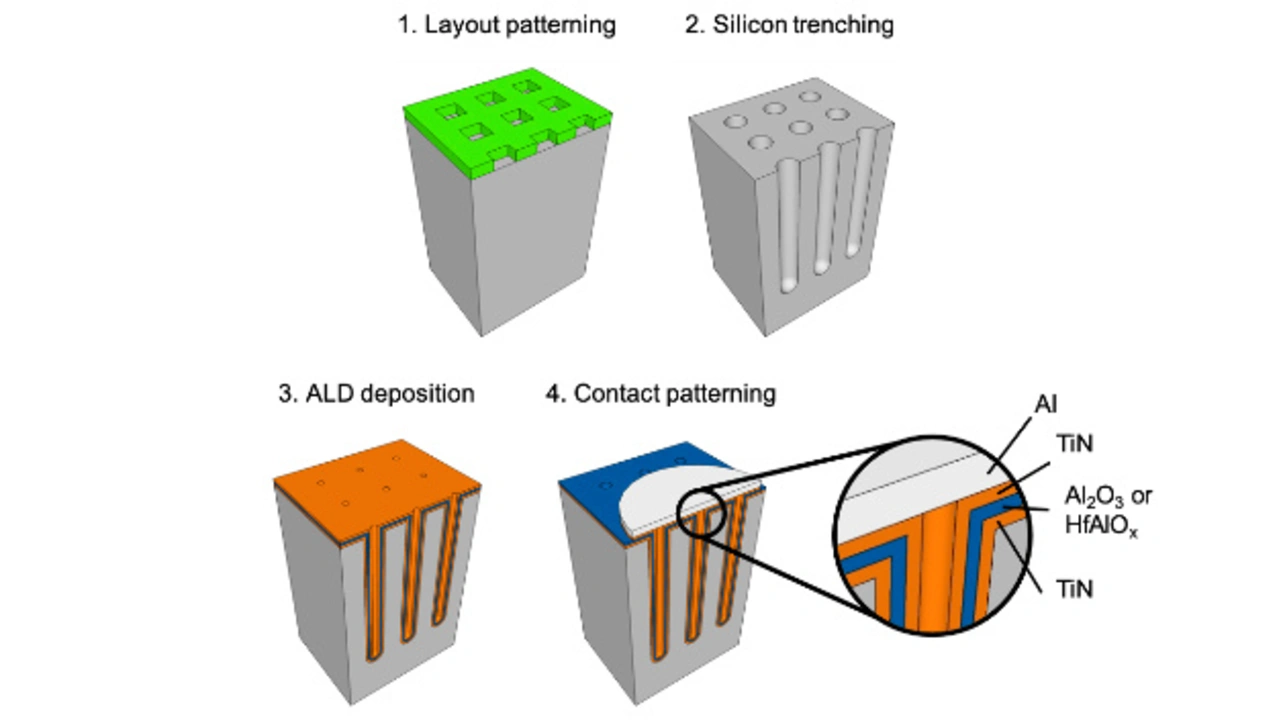

Dafür sind neue Techniken erforderlich, um die Leistungsfähigkeit zu erhöhen und gleichzeitig die Größe der Energiespeichereinheit zu verringern. Dreidimensionale Mikrokondensatoren mit hohem Seitenverhältnis und großer Oberfläche, bei denen ultradünne, abwechselnde Schichten aus leitenden und isolierenden Materialien die Energiespeicherstruktur bilden, stellen eine mögliche Lösung dar.

Jobangebote+ passend zum Thema

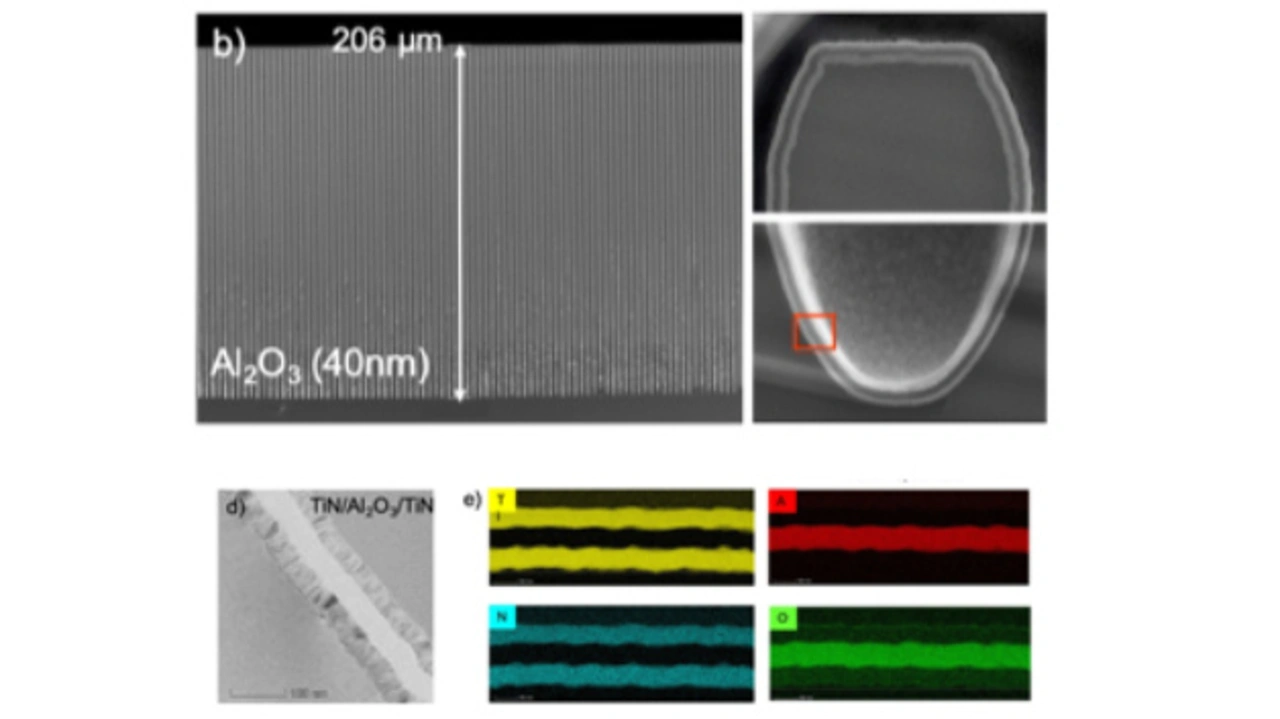

Mit der ALD-Technologie (Atomic Layer Deposition) von Picosun konnten Forscher der Universität Pisa unter Prof. Giuseppe Barillaro nun eine bislang unerreichte Leistungsfähigkeit von 3D-Mikrokondensatoren erreichen. Sie schafften es, in das Silizium geätzte Filmstapel aus leitendem TiN und isolierenden dielektrischen Al2O3- und HfAlO3-Schichten in Gräben mit einem Seitenverhältnis (Aspect Ratio) von bis zu 100 abzuscheiden.

Damit erreicht man eine flächenbezogene Kapazität von bis zu 1 µF/mm², was laut den Forschern einen neuen Rekord für diesen Kondensatortyp darstellt. Die Leistungs- bzw. Energiedichte betragen 566 W/cm² bzw. 1,7 µWh/cm² und übertrafen die Werte, die sich mit den meisten anderen Kondensatortechnologien erzielen lassen. Die ALD-Mikrokondensatoren zeigten nach Aussage der Forscher auch eine hervorragende Spannungs- und Temperaturstabilität bei bis zu 16 V und +100 °C bei 100 Stunden Dauerbetrieb. Dies könnte den Weg zu industriellen Anwendungen dieser Kondensatortechnologie ebnen, zumal ALD in praktisch allen modernen Fertigungslinien für Mikrochips vorhanden ist.

»Wir nutzten den verfügbaren Platz auf der Unterseite von Siliziumwafern, von denen nur wenige Mikrometer Silizium für elektronische Komponenten in integrierten Schaltkreisen verwendet werden, um unsere 3D-Mikrokondensatoren zu realisieren«, erläutert Prof. Giuseppe Barillaro, Gruppenleiter an der Fakultät für Informationstechnik der Universität Pisa, Italien. Er ergänzt: »Durch die elektrochemische Feinstbearbeitungstechnik, die wir in den letzten zehn Jahren an der Universität Pisa entwickelt haben, konnten wir Gräben mit hoher Dichte und einem Seitenverhältnis von bis zu 100 in Silizium zu ätzen. Ein solcher Wert lässt sich mit dem tiefen reaktiven Ionenätzen nicht erreichen. Auf dieser Grundlage konnten wir die flächenbezogenen Kapazitäten unserer 3D-Mikrokondensatoren durch eine gleichförmige Beschichtung mit einem Metall-Isolator-Metall-Stapel mit ALD erhöhen.«

Originalpublikation

Lucanos M. Strambinib, et al.: Three-dimensional silicon-integrated capacitor with unprecedented areal capacitance for on-chip energy storage, accepted for publication in Nano Energy, https://doi.org/10.1016/j.nanoen.2019.104281