Rechenleistung extrem

Das schnellste FPGA der Welt

Fortsetzung des Artikels von Teil 3

Die Vorteile hoher Verarbeitungsleistung

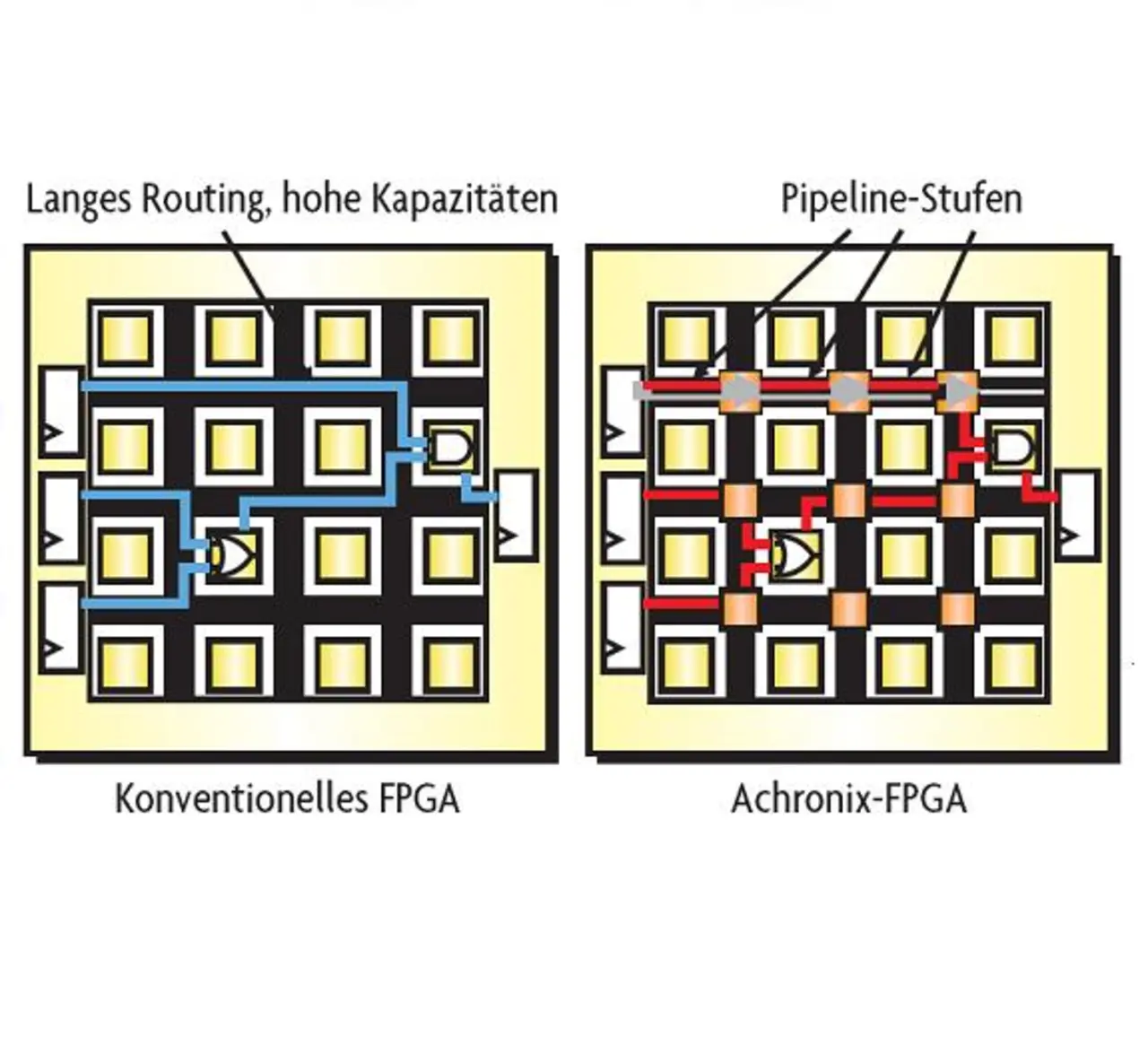

Welche Vorteile hat nun die pico- PIPE-Technologie, was das physische Layout in einem Achronix-FPGA betrifft? In einem herkömmlichen FPGA pflanzen sich die Signale über lange „Leiterbahnen“ fort und durchlaufen dabei zahlreiche Routing-Komponenten (Bild 6). Die Signale haben es dadurch mit sehr großen Kapazitäten zu tun, zumal die zurückzulegenden Wege umso länger werden, je größer das FPGA ist. Hinzu kommt, dass sich zwischen den zustandshaltenden Elementen (Registern) viele Logik-Ebenen befinden. In den Achronix-FPGAs ist durch das eingebaute Pipelining sichergestellt, dass Signale stets nur kurze Wege zurücklegen müssen, so dass sich die Kapazität für die Signale der einzelnen Stufen verringert. Bei größeren Bauelementen kann es aber nach wie vor sein, dass Signale von einer Ecke des Bausteins in die andere laufen müssen sen. Hier kann die Latenz tatsächlich geringfügig höher sein, doch im Unterschied zu anderen FPGAs leidet der Durchsatz nicht, da jede Pipelinestufe ein neues „Data Token“ halten kann. Das eingebaute Pipelining der pico- PIPE-Technologie erlaubt somit die Aufrechterhaltung eines größtmöglichen Durchsatzes, gleichgültig, wie groß das FPGA ist. Außerdem ist durch das Pipelining sichergestellt, dass auf jede Pipelining-Stufe nur eine Logik-Ebene kommt und die Rate der „Data Tokens“ folglich deutlich höher sein kann.

Nicht überall wird ein FPGA benötigt, das mit 1,5 GHz arbeitet – zumindest noch nicht. Doch auch wenn der maximale Durchsatz nicht gefordert ist, wartet die pico- PIPE-Technologie mit weiteren Vorteilen auf. Häufig erweist sich der Stromverbrauch als Problem in FPGAbasierten Systemen. Nicht selten ist ein System mit mehreren FPGAs bestückt, was zu einer übermäßig hohen Leistungsaufnahme führen kann. Achronix-FPGAs zeichnen sich dadurch aus, dass sie ein dynamisches Skalieren der Core-Spannung tolerieren. Die Versorgungsspannung kann so weit abgesenkt werden, dass die geforderte Leistung gerade noch erreicht wird. Dadurch wird entsprechend der reduzierten Leistung die Verlustleistung reduziert. Da die Verlustleistung proportional zum Quadrat der Versorgungsspannung steigt bzw. sinkt, bewirkt bereits eine geringfügige Absenkung der Core-Spannung einen deutlichen Rückgang des Leistungsbedarfs.

Die Dichte ist eine weitere Eigenschaft, die erheblich von der Leistungsfähigkeit der Achronix-FPGAs profitieren kann. Der native Leistungs- Vorteil macht es möglich, die Datenbusbreiten zu verringern – verglichen mit anderen Implementierungen, und häufig sogar gegenüber ASIC-RTLLösungen. Zum Beispiel erfordern existierende FPGAs ein zeitraubendes manuelles Einfügen von Pipelinestufen, Logik-Replikation usw. Diese Arbeitsgänge sind bei Achronix-FPGAs nicht erforderlich, so dass unter dem Strich eine kompaktere Implementierung entsteht. In Achronix-FPGAs passen folglich auch umfangreichere Designs als in traditionelle FPGAs mit gleicher Verarbeitungsleistung und äquivalenter LUT-Anzahl.

Eine höhere Dichte lässt sich mit Achronix-FPGAs auch mithilfe von TDM-Verfahren (Time Division Multiplexing) erzielen. Zum Beispiel können dank der Frequenz von 1,5 GHz bei der 65-nm-Speedster-Familie Logik, Speicher, Multiplizierer usw. per TDM genutzt werden, so dass sich eine höhere effektive LUT-Anzahl ergibt. Es ist z.B. möglich, bestimmte Ressourcen zwei-, vier- oder sogar achtmal pro Taktzyklus zu nutzen, sofern der Takt um denselben Faktor niedriger ist als die vom Baustein maximal unterstützte Taktrate. Da die optimalen Ergebnisse ohne manuelle Modifikationen am RTL-Code erreicht werden, ist – verglichen mit traditionellen FPGAs – deutlich weniger Zeit für die Implementierung eines FPGA erforderlich.

Auf Basis der picoPIPE-Technologie bieten Achronix-FPGAs entscheidende Leistungs-Vorteile gegenüber existierenden FPGAs. Die picoPIPETechnologie weist eine hohe Pipeline- Intensität auf und kann jedes Logikdesign implementieren, das von existierenden Synthese-Tools interpretiert werden kann. Durch das Abbilden auf die picoPIPE-Technologie erfolgt das Pipelining des Designs, ohne dass sich sein Verhalten ändert. Das Pipelining hebt den Durchsatz erheblich an und führt dazu, dass die Taktrate deutlich höher ist, als es mit bestehenden Technologien möglich wäre. Wird nicht der volle Durchsatz (1,5 GHz im Fall der 65-nm-FPGAs der Speedster-Familie) gebraucht, kommen Vorteile wie geringerer Stromverbrauch und mehr Dichte zum tragen.

Abgesehen von der bemerkenswerten picoPIPE-Technologie entscheiden über den Markterfolg noch andere Faktoren. Im Jahr 2006 ist Achronix mit einem 1,93-GHz-Chip gescheitert. Damals nutzte man einen 90-nm-Prozess von Chartered Semiconductor (heute GlobalFoundries), der zu exorbitanter Leistungsaufnahme führte. Zudem konnte man keine 10,3- Gbit/s-SerDes implementieren, da diese damals nur vom Lizenznehmer Snowbush in einem 65-nm- TSMC-Prozess erhältlich waren. Aus diesem Fehler hat man gelernt, bereits mit 20 W ist man dabei. Was ebenso für einen Erfolg spricht, ist die Unterstützung durch Tools wie Mentor Graphics’ Precision oder Synplify Pro von Synopsys. Das von Achronix entwickelte Backend-Tool für Place und Route, Timing und Analyse des kritischen Pfades ist von der Bedienung ähnlich zu den Tools von Altera und Xilinx. Auch für entsprechende IP ist gesorgt: Ein 32-bit-RISC-Prozessor von Cortus SA (Frankreich) wurde ebenso lizenziert wie diverse Blöcke wie Addierer oder FIR-Filter von der indischen Firma Softjin.

Jobangebote+ passend zum Thema

- Das schnellste FPGA der Welt

- Das Konzept der "Data-Tokens"

- Implementierung synchroner Logik

- Die Vorteile hoher Verarbeitungsleistung

- Fertigungspartnerschaft mit Intel macht den Unterschied

- Achronix-CEO detailliert Pläne