Rechenleistung extrem

Das schnellste FPGA der Welt

Wie Anfang der Woche gemeldet, wird Intel die FPGAs des Startups Achronix fertigen. Die Technologie ist bemerkenswert, immerhin sollen die FPGAs den dreifachen Durchsatz existierender Bausteine erreichen und das in der gleichen Prozessgeometrie.

Die Speedster-FPGAs gibt es zurzeit in vier Derivaten (Tabelle), sie stellen bis zu 40 10,3-Gbit/s-SerDes (Serializer/ Deserializer) zur Verfügung. Damit wird quasi alles unterstützt, was für die adressierten Applikationen relevant ist: PCI Express 1 und 2, Gigabit-Ethernet, CEI-6G, 10 Gbit/s Backplane, XAUI, XFI und Infiniband. DDR3 SDRAM wird bis 1066 Mbit/s unterstützt, RLDRAM II ebenso, SPI 4.2. bis 1000 Mbit/s und auch Hypertransport bis 800 Mbit/s.

Achronix will mit diesen FPGAs – nur auf den ersten Blick – überraschend nicht Xlinx oder Altera angreifen; zu tief verwurzelt sind bei den Marktführern Ecosystem, Kundenbeziehungen, und zu viele Produkte sind bereits im Einsatz, als dass diese einfach mal durch ein Startup verdrängt werden könnten. Vielmehr will man in Anwendungen vorstoßen, die relativ geringe Stückzahlen generieren (max. 8000 bis 10 000 pro Jahr), so dass die Entwicklung eines ASIC auf Grund der hohen Einmalkosten im Grunde genommen unwirtschaftlich ist. Es gibt jedoch z.B. Anwendungen im Telekommunikationsbereich, beim Messen und Testen, Militär oder in der Raumfahrt, wo die benötigte Leistung von allen heute verfügbaren FPGAs nicht erbracht werden kann. Die Folge ist, dass die Hersteller zähneknirschend ein ASIC designen müssen, obwohl wirtschaftlich gesehen ein FPGA die bessere Wahl wäre. Dieser Markt wird auf 1,7 Mrd. US-Dollar geschätzt. Verizon und AT&T haben z.B. Anfang 2010 ihre 40- und 100-Gbit/s-Ethernet- Systeme ausgerollt.

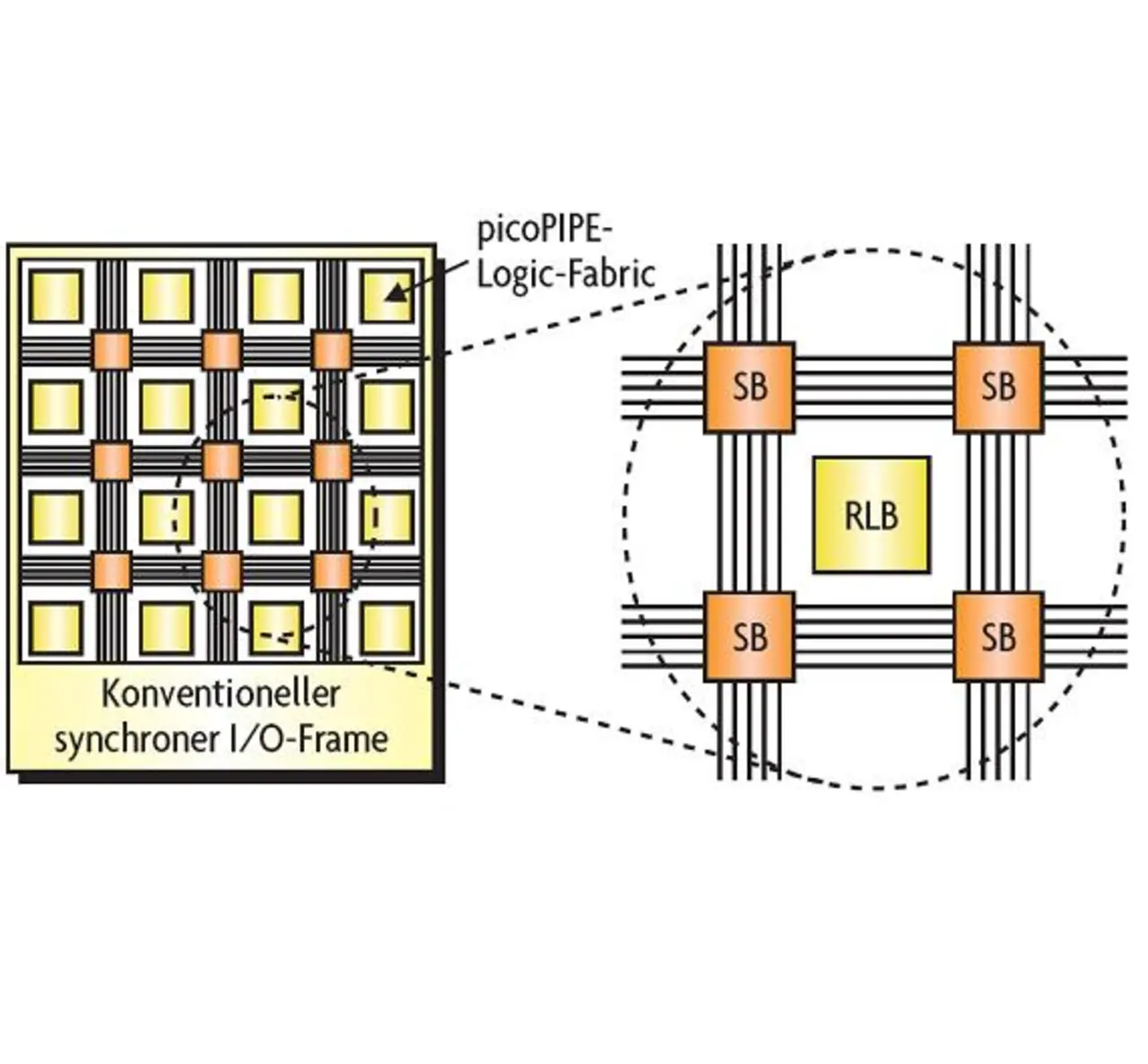

Achronix-FPGAs bestehen aus einem konventionellen I/O-Frame, den eine „picoPIPE- Logic-Fabric“ umgibt (Bild 1). Der Frame ähnelt der Peripherie anderer programmierbarer Bauelemente des High-End-Segments; er besteht aus konfigurierbaren I/Os, SerDes- Einheiten, Taktschaltungen, PLLs usw. Er stellt die Schnittstellen zwischen dem Chip und der Außenwelt zur Verfügung und fungiert gleichzeitig als Grenze zwischen dem picoPIPE-Core und diesen Schnittstellen. Sämtliche Daten, die aus dem Core heraus- bzw. in ihn hineinkommen, müssen somit diesen Frame durchlaufen.

Solange man die interne picoPIPEStruktur als Blackbox betrachtet und ihre Interna unbeachtet lässt, ist sie von einer konventionellen FPGAFabric praktisch nicht zu unterscheiden – wenn man von ihrem erheblich höheren Datendurchsatz absieht. Die picoPIPE-Fabric setzt sich aus rekonfigurierbaren Logik-Blöcken (re-configurable Logic Blocks, RLBs) zusammen, die über eine programmierbare Struktur miteinander verbunden sind. Jeder RLB ist dazu von Schaltblöcken (Switch Boxes, SBs) umgeben (Bild 1), deren Aufgabe es ist, Signale durch die picoPIPE-Fabric zu routen.

Jeder RLB enthält acht Look-Up-Tabellen (LUTs) mit vier Eingängen, Speicher-Elemente und 128 bit RAMSpeicher. Neben den RLBs und den programmierbaren Routing-Ressourcen sind in der picoPIPE-Fabric auch Block-RAMs und spezielle Multiplizierer vorhanden. RLBs und Routing- Funktionen sind mit der picoPIPETechnologie implementiert und kommen dadurch auf wesentlich mehr Durchsatz als FPGAs, die nicht auf picoPIPE basieren. Um der Maximal- Leistung des Bausteins gerecht zu werden, arbeiten Speicher und Multiplizierer mit 1,5 GHz.

Jobangebote+ passend zum Thema

| Baustein | SPD30 | SPD60 | SPD100 | SPD180 |

|---|---|---|---|---|

| Anzahl LUTs |

24576 | 47040 | 93848 | 163840 |

| picoPIPE-Elemente | 1725000 | 3400000 | 720000 | 11700000 |

| Anzahl 18-kbit-Block-RAMs | 66 | 144 | 334 | 556 |

| Block-RAM (kbit) | 1188 | 2592 | 6012 | 10008 |

| Distributed RAM (Kbit) | 384 | 735 | 1232 | 2560 |

| Anzahl Multiplizierer (18x18) | 50 | 98 | 120 | 270 |

| Anzahl 5-Gbit/s-SerDes | - | 8 | - | - |

| Anzahl 10,3-Gbit/s-SerDes | 8 | 20 | 36 | 40 |

| DDR2/DDR3-Controller (1066 Mbit/s) | 2 | 4 | 4 | 4 |

| Anzahl PLLs | 8 | 16 | 16 | 16 |

| Programmierbare I/O (ohne SerDes) | 488 | 768 | 832 | 933 |

| Schätzung Leistungsaufnahme (W) bei 65 nm | <20 | 30 | 35 | >40 |

Die Speedster-FPGA-Familie beinhaltet derzeit vier Derivate, die in einem 65-nm-Prozess gefertigt werden.

- Das schnellste FPGA der Welt

- Das Konzept der "Data-Tokens"

- Implementierung synchroner Logik

- Die Vorteile hoher Verarbeitungsleistung

- Fertigungspartnerschaft mit Intel macht den Unterschied

- Achronix-CEO detailliert Pläne