High-Speed-Steckverbinder

100-Gbit/s-Ethernet auf Backplane-Systemen

Mithilfe der Channel Operation Margin nach IEEE 802.3bj lässt sich der Übertragungskanal und die eingesetzten High-Speed-Steckverbinder neutral bewerten. Letztere liefert z.B. die Firma ERNI mit ihren ERmet-ZDHD-Steckverbindern, welche die Vorgaben für 100-Gbit/s-Ethernet auf Backplanes erfüllen.

Von Stefan Molitor ist Entwickler von High-Speed-Steckverbindern bei ERNI Production und Dr. Thomas Gneiting ist Geschäftsführer von AdMOS.

Der Trend in der Kommunikationstechnik hin zu immer größeren Datenmengen und einer dadurch erforderlichen höheren Bandbreite in den Vermittlungsknoten ist ungebrochen. Daher gibt es für die Ethernet-Datenübertragung mit 100 Gbit/s (GbE) hinreichenden Bedarf von Netzwerkbetreibern und Rechenzentren. Dermaßen hohe Bandbreiten sind unter anderem vonnöten für die Aggregation im Internet-Backbone der nächsten Generation, den Einsatz in Rechenzentren in Host-Bussen bzw. für Inter-Switch-Verbindungen und Cloud Computing (Speicherung).

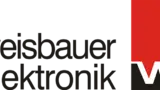

Vor diesem Hintergrund ist der Normentwurf der „IEEE 802.3 100Gb/s Backplane and Copper Cable Study Group“ für einen Standard für Datenübertragungen von 100 Gbit/s auf Backplane-Systemen zu sehen. Für die wichtige Schnittstelle zwischen Backplane und Tochterkarten gibt es verschiedene Produktlösungen; so auch die ERmet-ZDHD-High-Speed-Steckverbinder von ERNI Electronics. Als Antwort auf den steigenden Bandbreitenbedarf wurde von der IEEE P802.3ba Task Force der Standard für Ethernet mit 40 Gbit/s und 100 Gbit/s entwickelt und 2010 verabschiedet. Dieser Standard beinhaltet die Physical-Layer-Spezifikationen für den Betrieb mit 40 Gbit/s über Backplanes und Kupferleitungen wie auch 100 Gbit/s über Kupferkabel und parallele 10-Gbit/s-Links. Die Anforderungen für jede Lane der elektrischen Schnittstelle basieren auf 10GBASE-KR. Allerdings enthält der Standard keine Spezifikation für 100-Gbit/s-Ethernet über die Backplane. Daher wurde 2011 die IEEE P802.3bj Task Force gebildet, um Backplane-Ethernet auf 100 Gbit/s (vier Lanes mit je 25 Gbit/s) zu erweitern. Mit mittlerweile verfügbaren, hoch integrierten PHY-ICs können 100-Gbit/s- Produkte gemäß der IEEE-802.3bj-Norm entwickelt werden, die 100GBASE-CR4/SR4/LR4 auf dem Front Panel und 100GBASE-KR4 auf der Backplane unterstützen.

Die neue Norm IEEE 802.3bj

Der IEEE-802.3bj-Standard für 100-Gbit/s-Ethernet über vier differenzielle Kupferleitungen bringt verschiedene neue Konzepte mit sich – beispielsweise eine umfassende Margen-Abschätzung für die Kanal-Performance oder eine obligatorische Vorwärtsfehlerkorrektur (FEC). So erlaubt die FEC etwa 5 dB an zusätzlichen Einfügungsverlusten, was die Reichweite erhöht. Außerdem wird die Koexistenz von zwei Standards mit derselben aggregierten Bitrate über die Backplane unterstützt, um verschiedene Märkte abzudecken: 100GBASE-KP4 für Multi-Level-Signaling (PAM4) und 100GBASE-KR4 für das herkömmliche PAM2 (NRZ).

Die IEEE-Norm 802.3bj befindet sich zur Zeit im Entwurfsstadium und ist neben speziellen Standards, z.B. für optische Übertragungssysteme, ein Teilaspekt der 100-GbE-Normen. Sie beschreibt das Verhalten von Signalen in Informationssystemen, z.B. in Vermittlungsrechnern, bei denen die 100-GbE-Signale auf Leiterplatten mit Kupferleitungen übertragen werden, die als Backplane-Systeme ausgeführt werden können. Im Standard wird das Verhalten eines Systems beschrieben, bei dem der 100-Gbit/s-Datenstrom eines Kanals zur Weiterverarbeitung durch einen Multiplexer auf vier parallele Kanäle mit je 25 Gbit/s aufgeteilt wird (Bild 1).

Entscheidend hierfür ist eine weitere Miniaturisierung des kritischen Interface zwischen Stecker und Leiterplatte, was wiederum eine technologische Herausforderung für die Hersteller von Steckverbindern und Leiterplatten darstellt. Ein neuer Aspekt ist, dass die Eignung eines Übertragungskanales nicht mehr durch bestimmte Grenzwerte, sondern durch ein komplexes Berechnungsverfahren – der „Channel Operation Margin“ (COM) – definiert wird.

Channel Operation Margin zur Beurteilung des Kanals

Eine wesentliches Kriterium für die Task Force bestand darin, dass sowohl Übertragungskanäle mit Verlusten bis 35 dB bei 12,9 GHz als auch PAM4-Signale mit Kanalvorgaben von 33 dB bei 7 GHz unterstützt werden müssen. Angesichts der vielfältigen adressierten Applikationen lag die Herausforderung darin, dass die Anforderungen aus den verschiedenen Marktsegmenten unter einem oder zwei PAM2- bzw. PAM4-Designs vereint werden mussten. Die Antwort auf diese Herausforderung ist eine Performance-Abschätzung, die eine Abwägung zwischen Verlusten, Reflexionen und Nebensprechen sowie zwischen Kanalumsetzung und den Fähigkeiten der Chips bzw. Komponenten ermöglicht. Mit anderen Worten: Es ist eine Budget-Beurteilung erforderlich, die diese Abwägungen unterstützt.

Das COM-Verfahren zur Abschätzung wird für die Kanalspezifikation und Empfängertests genutzt. Damit ist ein Abgleich zwischen Kanälen mit hohen Verlusten und geringem Rauschen sowie Kanälen mit geringeren Verlusten möglich, die aber rauschbehafteter sind. Außerdem können mit Hilfe von COM die Einflüsse von Gehäusen und Steckverbindungen bewertet werden. Die Berechnung der Channel Operation Margin (COM) erlaubt eine neutrale Bewertung einer Übertragungsstrecke mit Sender, Empfänger und passivem Übertragungspfad. Die IEEE-802.3bj-Norm bezieht sich auf diese COM-Berechnung. Einfache Kriterien wie Reflexionsverluste (Return Loss, RL), Einfügungsverluste (Insertion Loss,IL), Nahnebensprechen (NEXT) oder auch zusammengesetzte Werte wie Insertion Loss Deviation (ILD) beschreiben nur den passiven Teil des Kanals und reichen nicht aus.

Selbst die Auswertung von Simulationen der Datenübertragung im Zeitbereich ist nicht immer aussagekräftig oder dauert unter Umständen sehr lange, wenn die Modelle der Treiber/Empfänger nur als klassische SPICE-Modelle (Simulation Program with Integrated Circuit Emphasis) und nicht z.B. als IBIS-AMI-Modelle (Input/Output Buffer Information Specification Algorithmic Modeling Interface) vorliegen. COM wurde u.a. von Anwendern bzw. Chip-Lieferanten entwickelt und versucht den Worst Case des passiven Kanals abzubilden.

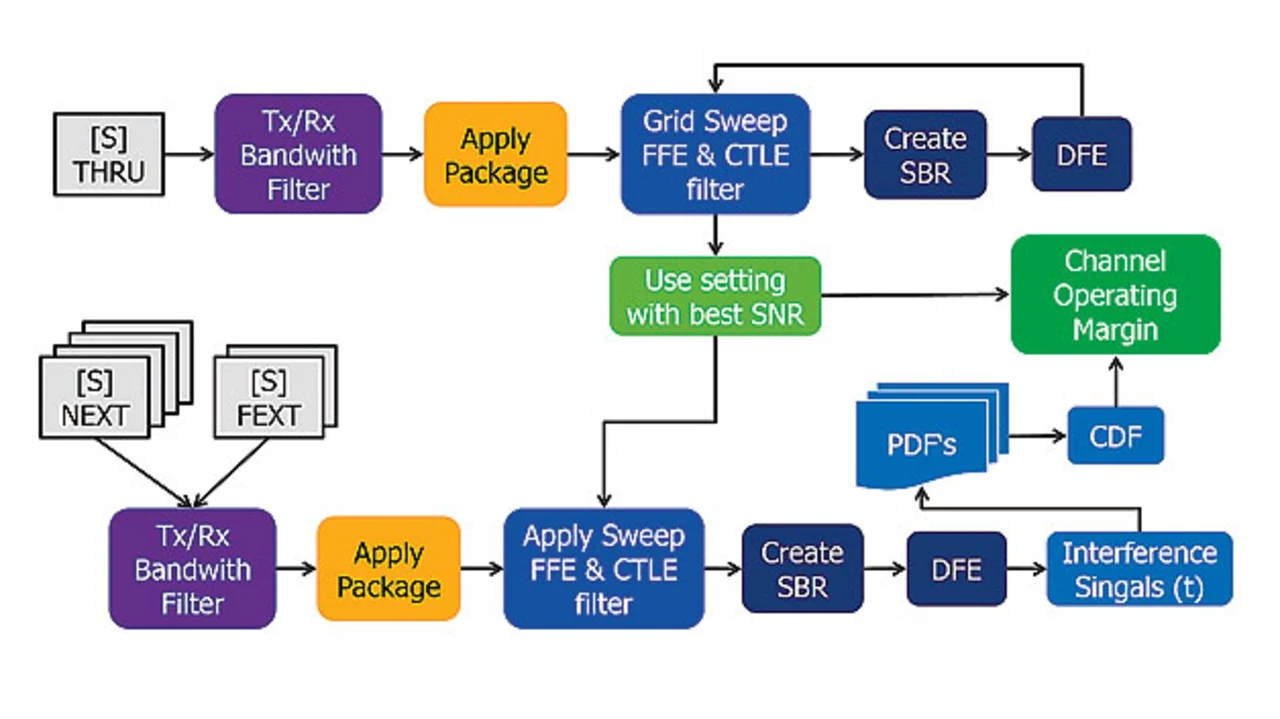

Daher kann das COM-Verfahren als sehr konservative Abschätzung angesehen werden. Für die COM-Berechnung (Bild 2) werden vielfältige Eingangsparameter für den Sender/Empfänger (Spannungspegel, Modulation, Signalrate, TX Equalisation, Rauschen usw.) sowie für das IC-Gehäuse (parasitäre Effekte, Nebensprechen) und den passiven Übertragungskanal (4-Port-S-Parameterdaten für die Durchgangsrate und alle NEXT/FEXT-Aggressoren) herangezogen. Letztendlich gibt COM den verfügbaren Signal-Rausch-Abstand wieder. Die Kanal-Performance wird mit der Frame Loss Ratio (FLR) ausgedrückt.

- 100-Gbit/s-Ethernet auf Backplane-Systemen

- Spezielles Design, kleine Vias