High-Speed-Steckverbinder

100-Gbit/s-Ethernet auf Backplane-Systemen

Fortsetzung des Artikels von Teil 1

Spezielles Design, kleine Vias

Die Erfahrung zeigt, dass die Schnittstelle zwischen Stecker und Leiterplatte den entscheidenden Bereich für den Übertragungskanal darstellt und somit größte Bedeutung für die Übertragungsqualität der Hochgeschwindigkeitssignale hat. Der ERmet ZDHD ist ein High-Speed-Steckverbinder von ERNI für differenzielle Datenübertragungen, der mit kontrollierter Impedanz, Skew-Kompensation und einer hohen Kontaktdichte aufwartet.

Die Simulation des Leiterplattenlayouts diente als Grundlage für das komplette Stecksystem des ERmet ZDHD. Das von ERNI patentierte Layout basiert auf Vias mit einem Fertiglochdurchmesser von 0,46 mm für Schirm und Signal, welche einen Abstand von 1,2 mm haben.

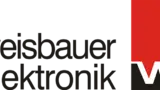

Ein Versatz der Reihen um 1,8 mm zueinander führt dazu, dass die Vias der Signalpaare optimal von Schirm-Vias umgeben sind. Dies resultiert in einem sehr guten Verhalten in Bezug auf das Übersprechen (Crosstalk). Für eine solche Anordnung ist jedoch ein großer Aufwand beim Steckverbinder-Design erforderlich. Bei der Federleiste des ERmet ZDHD (Bild 3) wird das prinzipiell mit zwei sogenannten Wafern oder Federpaketen gelöst, welche abwechselnd aneinandergereiht werden und mit der Front- und Rückseite fixiert sind.

Ein Wafer besteht aus den Federkontaktpaaren, welche in die Kunststoffaufnahmen eingelegt und mit einem Kunststoffdeckel verschlossen sind. Rückseitig ist ein Federschirmblech aufgeklemmt, welches die Federpakete gegeneinander abschirmt. Im Anschlussbereich befinden sind die Einpresszonen für die Vias mit 0,46 mm Durchmesser. Die Messerleiste besteht aus den Signalkontaktpaaren und den L-förmig ausgeführten Schirmblechen. Diese dienen nicht nur der Abschirmung von Paar zu Paar, sie bieten zusätzlich einen mechanischen Schutz für die sensiblen Signalkontakte. Die Kontaktteile werden in das Gehäuse eingeschossen. Auch hier ist der Versatz der Reihen gegeben.

COM-Evaluierung für den ERmet ZDHD

Nach Publikation der COM-Methode wurde mit dieser die Leistungsfähigkeit des Steckverbindungssystems ERmet ZDHD evaluiert. Als Messaufbau diente hierbei ein entsprechendes Übertragungssystem (passiver Übertragungspfad mit 25 Gbit/s je Leitung) in einer Simulationsumgebung.

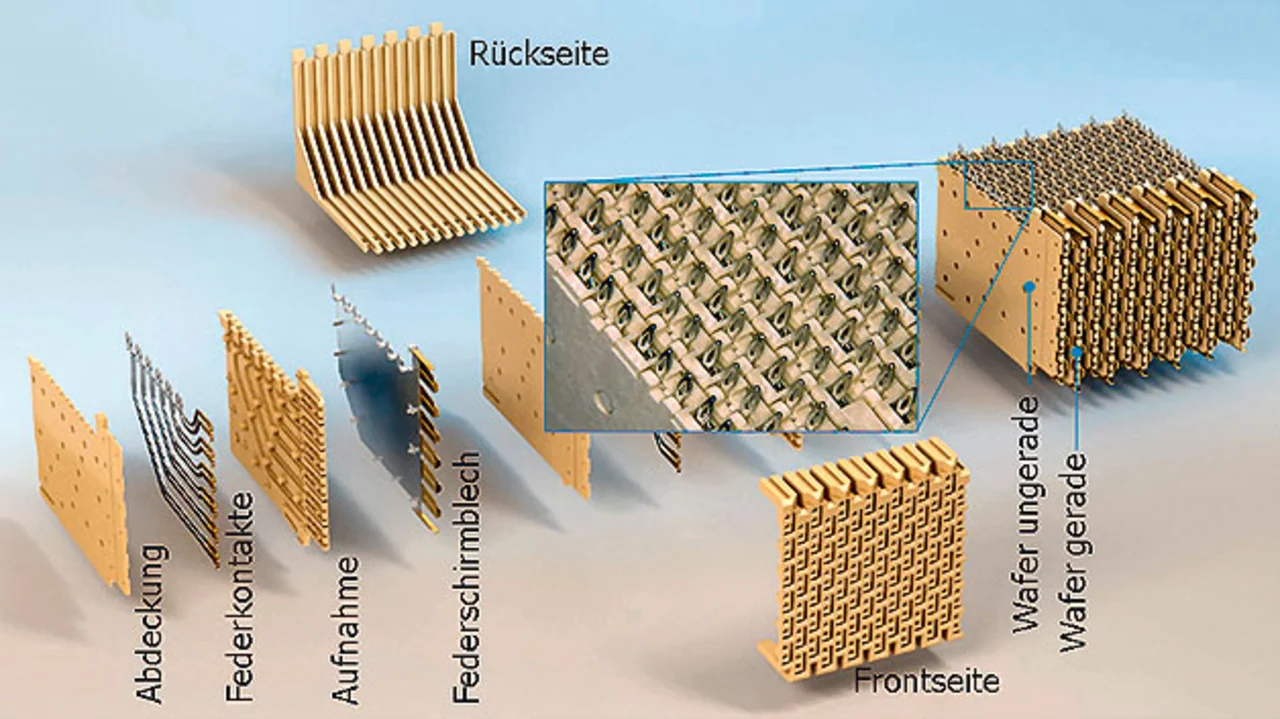

Für die einzelnen Komponenten wie den Übergang vom Stecker in die Backplane mit Backdrilling und Skew-kompensierten Leitungen wurden Touchstone-Dateien aus 3D-Simulationen erstellt. Teilweise konnten diese Daten mit dem gemessenen Hochfrequenzverhalten der Originalbauteile – z.B. des ERmet-ZDHD-Steckverbinders – verifiziert und abgeglichen werden (Bild 4).

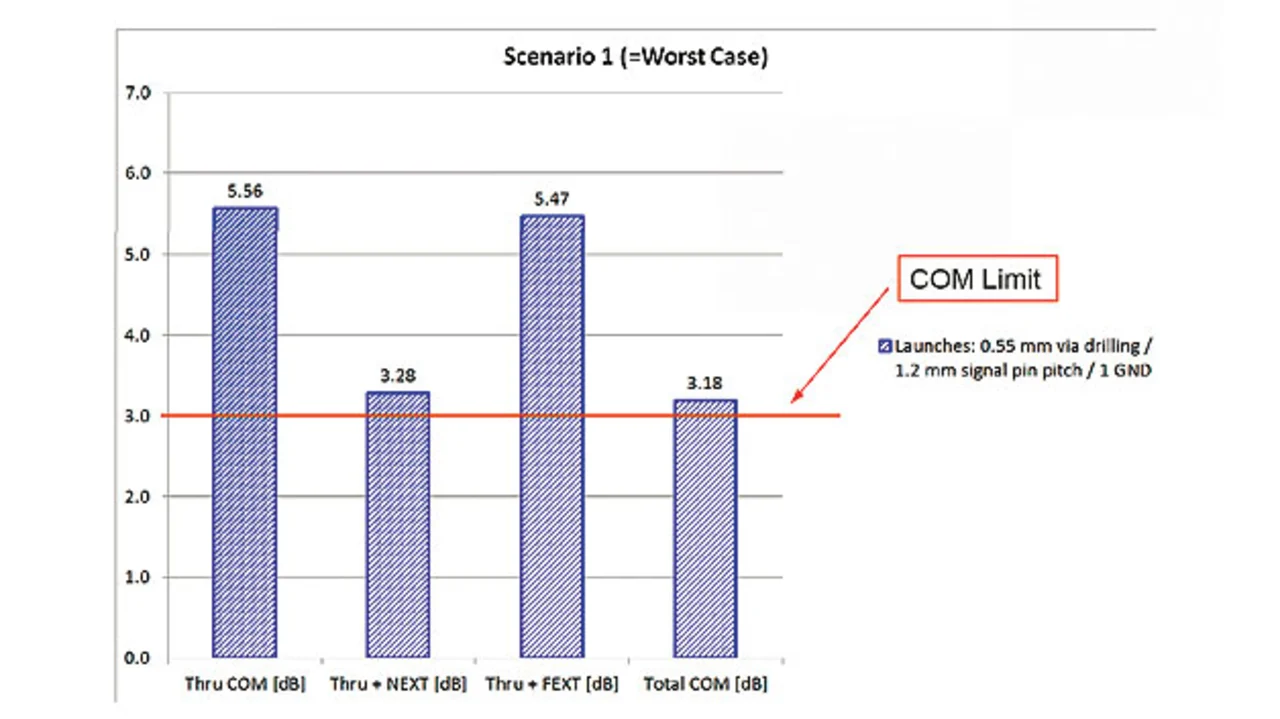

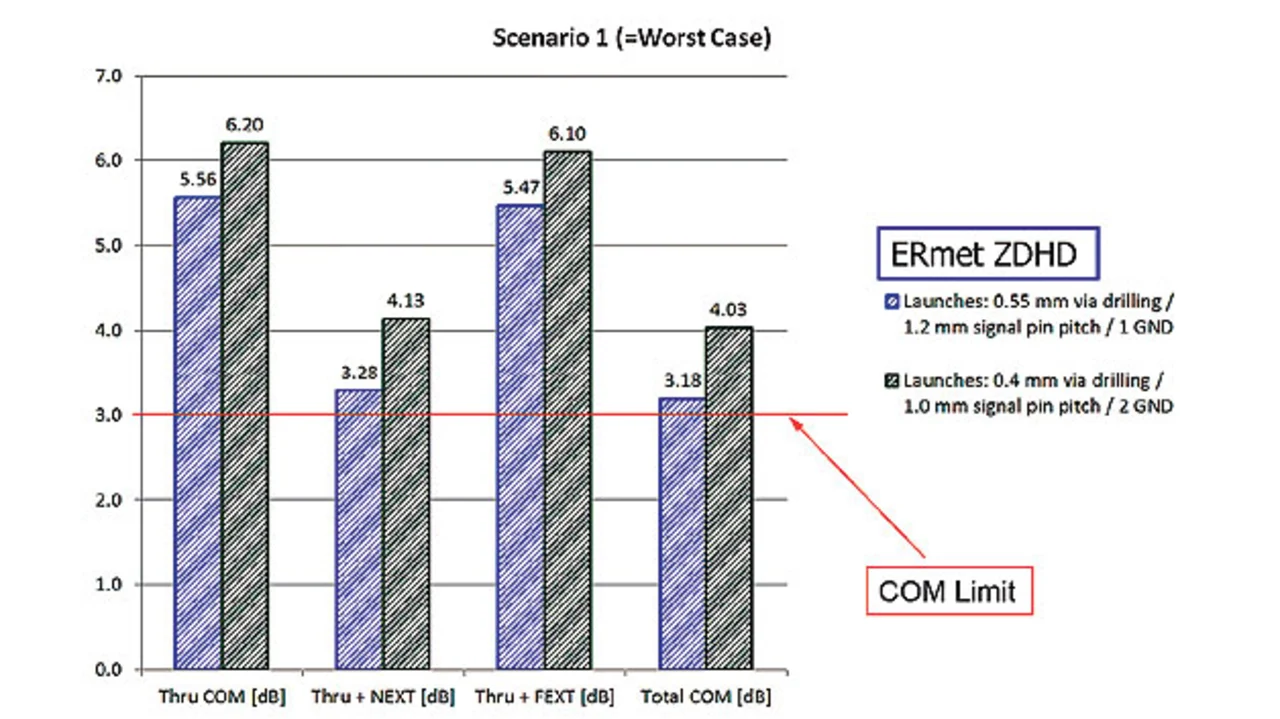

Bei der Definition der Signalanordnung wurde bewusst eine Konfiguration (in Bezug auf das Nebensprechen) gewählt, die nicht optimiert ist, um ein Worst-Case-Szenario zu erhalten. Selbst für die gewählte Worst-Case-Konfiguration wird das erforderliche COM-Limit von 3 dB erreicht (Bild 5).

Weitere Optimierungen waren erforderlich

Aus der COM-Analyse für den ERmet ZDHD ist ersichtlich, dass eine weitere Steigerung der Leistungsfähigkeit vor allem ein besseres NEXT-Verhalten im Anschlussbereich erfordert.

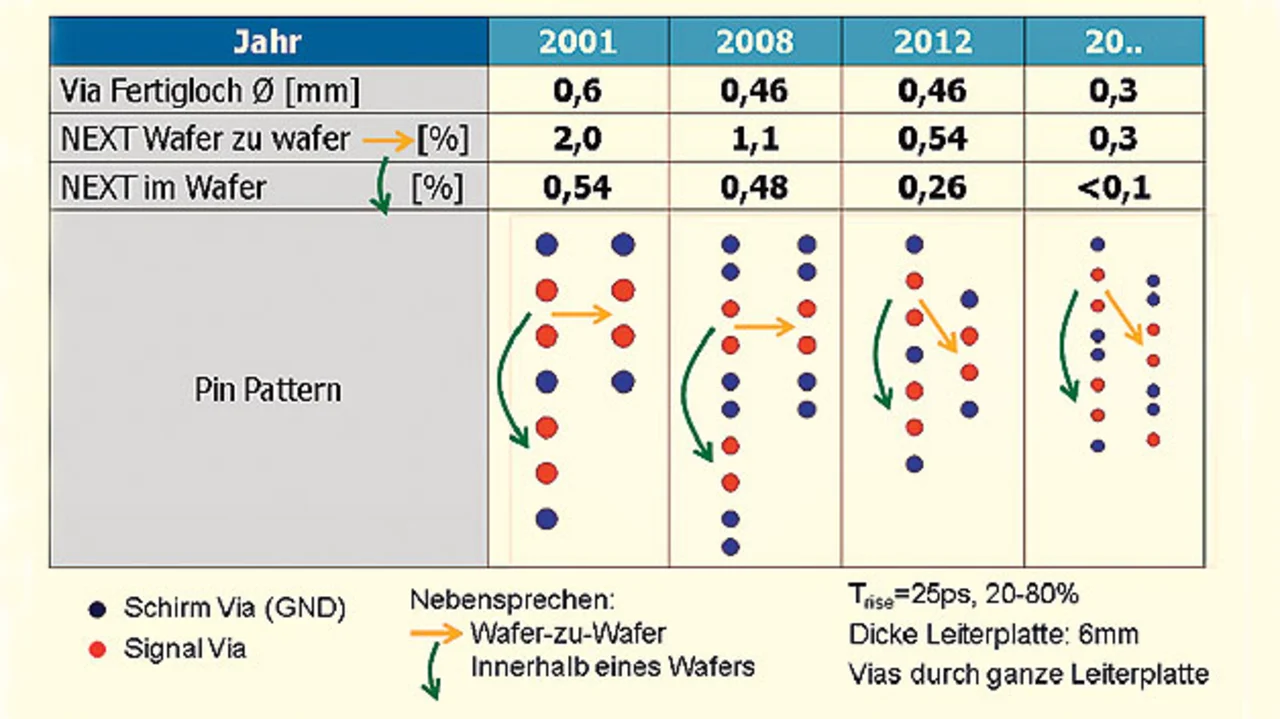

Um dies zu verifizieren, wurde in einer Simulationsstudie das Nebensprechen in einer Leiterplatte als Funktion der Signal/Ground-Via-Durchmesser, der Anordnung und der Anzahl der Ground Vias untersucht. Als Verifizierungsschritte dienten dabei Messungen des Nebensprechens und der charakteristischen Impedanz auf einer Multilayer-Platine mit einer Dicke von 6 mm, bei der verschiedene Anordnungen von Signal/Ground Vias vorhanden waren.

Vom ERmet ZDHD ausgehend, basiert das optimierte Design auf Vias mit einem Fertiglochdurchmesser von 0,3 mm für Schirm und Signal. Der Versatz der Reihen um 1,8 mm zueinander wird beibehalten, damit auch die Verteilung der Schirm-Vias – rund um die Vias der Signalpaare – erhalten bleibt.

Der Abstand der Signal-Vias in der Reihe beträgt jetzt nur noch 1 mm, und durch den so gewonnenen Platz lassen sich zwei Schirm-Vias im Abstand von 0,6 mm platzieren. Die Erkenntnis, dass eine Verkleinerung der Vias das Nebensprechverhalten verbessert, führt konsequenterweise zu einer weiteren Miniaturisierung der Einpresszone. Bild 6 gibt einen aufschlussreichen Überblick über die Entwicklung der Größe der Einpresszonen und die damit einhergegangene Reduzierung des Nahnebensprechens (NEXT).

Die COM-Berechnung wurde mit den optimierten ERmet-ZDHD-Steckverbindern wiederholt und für beide Varianten dargestellt (Bild 7). Dabei sind die Werte für verschiedene Konfigurationen aufgegliedert. „Thru COM“ geht von einem System ohne Nebensprechen aus, während bei „Thru+NEXT“ bzw. „Thru+FEXT“ nur je eine Art des Nebensprechens betrachtet wird. Total COM schließlich umfasst alle parasitären Einflüsse und wird als Worst-Case-Betrachtung des Systemverhaltens angesehen.

Es ist deutlich zu erkennen, dass vor allem das NEXT-Verhalten, aber auch das Durchgangsverhalten (Thru) nochmals verbessert werden kann.

Literatur

[1] COM Update and COM Quick Guide. http://www.ieee802.org/3/bj/public/tools.html [2] Dong,X.; Mo, M.; Rao, F.; Jin, W.; Zhang, G.: Relating COM to Familiar S-Parameter Parametric to Assist 25Gbps System Design. DesignCon 2014, Santa Clara. [3] Mellitz, R.; Ran, A.; Li, M.P.; Ragavassamy, V.: Channel Operating Margin (COM): Evolution of Channel Specifications for 25 Gbps and Beyond. DesignCon 2014, Santa Clara

Die Autoren

|

Stefan Molitor |

|---|

| beendete 2008 das Studium mit dem Abschluss Diplom-Ingenieur (FH) Mechatronik/Feinwerktechnik an der Hochschule Esslingen am Standort Göppingen. Seit 2008 ist er bei ERNI Production im Bereich Entwicklung und Konstruktion von Steckverbindern tätig. Schwerpunktmäßig beschäftigt er sich mit der Neu- und Weiterentwicklung von Steckverbindern für hohe Datenübertragungsraten |

stefan.molitor@erni.com

| Dr. Thomas Gneiting |

|---|

|

studierte an der Hochschule Esslingen und promovierte 1997 an der Brunel University of West London. Seit 1997 ist er Geschäftsführer der Firma AdMOS GmbH in Frickenhausen. Schwerpunkte von AdMOS liegen in der Simulation und Modellierung von CMOS-Transistoren im Nanometer-Bereich sowie von passiven Komponenten auf Board- und Chip-Ebene. Ein besonderer Fokus liegt dabei auf der Unterstützung von Kunden beim Entwurf neuer Steckverbinder durch Simulationen, Machbarkeitsstudien und Messungen an Entwurfsmustern. |

thomas.gneiting@admos.de

- 100-Gbit/s-Ethernet auf Backplane-Systemen

- Spezielles Design, kleine Vias