Digitale Signalverarbeitung

Industrielle Inspektionssysteme erleichtern die Fehlersuche

Fortsetzung des Artikels von Teil 2

Das Prozessor-Arbeitspferd

Die für Inspektionssysteme verwendeten rechenintensiven Algorithmen erfordern hochleistungsfähige Verarbeitungssysteme. Die Multicore-DSPs von TI sind für diese Anforderungen ausgelegt. Der C6678-DSP verfügt über acht Cores, wobei jeder Core mit einer Taktfrequenz bis zu 1,25 GHz arbeitet. Jeder Core verfügt über eine VLIW-Prozessorarchitektur (Very Long Instruction Word) mit zwei Datenpfaden und kann sowohl Gleitkomma-Operationen (Gleitkomma-Zahlen nach IEEE 754 mit 32 bit und 64 bit) als auch Festkomma-Operationen verarbeiten. Da VLIW-Architekturen eine geringere Hardware-Steuerungslogik voraussetzen, bieten sie deutlich weniger Leistungsverlust im Vergleich zu Parallelarchitekturen (z.B. superskalare Architekturen, wie sie in vielen GPUs verwendet werden).

Jeder DSP-Core verfügt über eine Rechenrohleistung von 32 Festkomma-MAC-Operationen pro Taktzyklus und 16 FLOPS (Gleitkomma-Operationen pro Sekunde) pro Taktzyklus. Die Kerne sind optimal für die vektororientierte Verarbeitung geeignet. Geräte kommen auf eine Gesamtleistung von 320 GMAC/s für Festkomma- und 160 GFLOPS für Gleitkomma-Operationen.

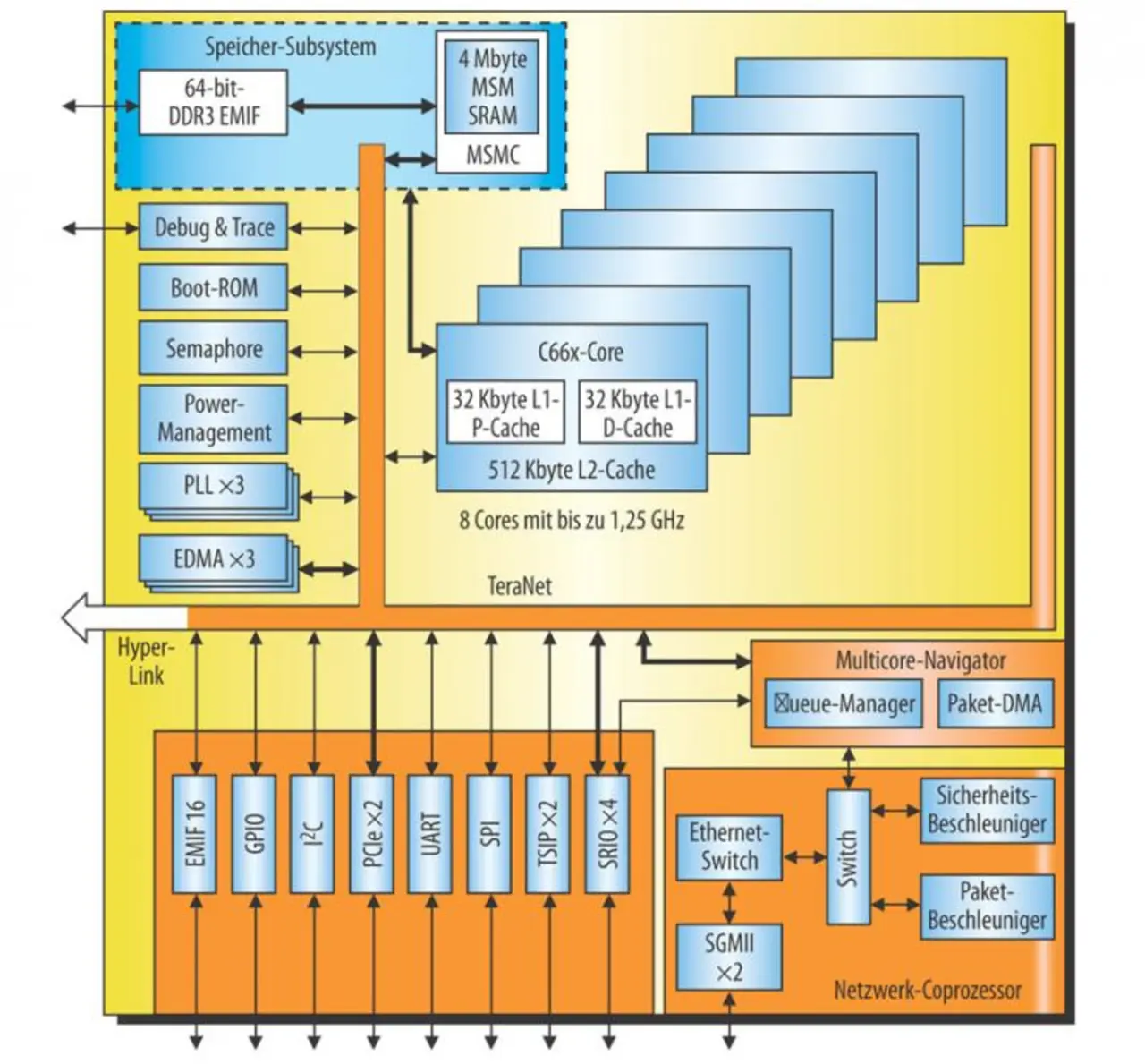

Bild 3 zeigt ein detailliertes Diagramm der internen Architektur des C6678. Jeder Core verfügt über einen Level-1-Programmspeicher (L1P) mit 32 KB und einen Level-1-Datenspeicher (L1D) mit ebenfalls 32 KB. Beide Speicher können als Cache und/oder als adressierbares SRAM konfiguriert werden. Zusätzlich hat jeder Core einen lokalen Level-2-Speicher (L2) mit 512 KB. Wie der Level-1-Speicher kann auch der Level-2-Speicher als Cache und/oder als adressierbares SRAM konfiguriert werden. Der C6678-DSP verfügt zudem über ein separates, 4 MB großes SRAM, das von allen acht Cores genutzt wird. Damit ein schneller Zugriff auf den externen Speicher gewährleistet ist, wird ein 64-bit-Multicore-Speichercontroller (MSMC) eingesetzt, der bis zu 8 GB eines externen DDR3-Speichers mit 1,6 GHz und ECC-Unterstützung adressieren kann.

Dank der geteilten Speicherarchitektur können die Cores die verschiedenen Ausschnitte eines Bildes parallel verarbeiten oder verschiedene Verarbeitungsfunktionen im selben Ausschnitt des Bildes nacheinander durchführen. Das Entwicklerteam profitiert dadurch von mehr Flexibilität im Hinblick auf die Architektur des Systems und kann das gleiche Erfassungssystem für mehrere Inspektionsanwendungen verwenden. Die Speicherarchitektur erlaubt zusammen mit einer intelligenten erweiterten Direktspeicherzugriffssteuerung (EDMA, Enhanced Direct Memory Access Controller), die von allen Cores verwendet wird, die Übertragung von Daten über externe Speicher, speicheradressierte Peripheriegeräte und Speicher auf dem Chip. Die Datenübertragung findet durch doppelte Pufferung statt, was zu einer enormen Leistungsverbesserung führt.

Die modernen Multicore-DSPs bieten eine hohe Systemintegration bei reduzierter Stromaufnahme und kleinem Formfaktor. Dies führt zu weniger Prozessoren, kleineren Stromversorgungsgeräten, geringeren Kühlungsanforderungen und weniger Gesamtkosten für das System. Der TMS320C6678 unterstützt zusätzliche Funktionen, um die Multicore-Leistung zu verbessern und den Benutzer bei der effizienten Nutzung aller Cores zu unterstützen.

Zu den zusätzlichen Funktionen gehören Multicore-Navigator, TeraNet und HyperLink. Multicore-Navigator ist ein paketbasierter Manager, der bis zu 8192 Warteschlangen steuert. In die Warteschlange eingereihte Tasks werden durch die hardware-beschleunigte Verteilung des Multicore-Navigator an die geeignete und verfügbare Hardware geleitet. Der Multicore-Navigator verschiebt Pakete ohne den sonst erforderlichen Software-Overhead und stellt dadurch mehr CPU-Bandbreite für die Bildverarbeitung bereit.

HyperLink stellt eine Chip-Level-Verbindung mit 50 Gbit/s bereit, wodurch mehrere SoCs nebeneinander arbeiten können. Der geringe Protokoll-Overhead und die hohe Durchsatzrate machen HyperLink zur idealen Schnittstelle für Chip-to-Chip-Zwischenverbindungen. In Zusammenwirken mit Multicore-Navigator verteilt HyperLink Tasks transparent an andere SoCs und führt Aufgaben so aus, als würden sie auf lokalen Ressourcen ausgeführt.

Dank Hyperlink können zwei C6678s nahtlos verbunden und so kann die Rechenleistung verdoppelt werden. Hyperlink kann auch mit externer Logik verbunden werden, was die Verwendung von Hochgeschwindigkeitskameras und analogen Frontend-Geräten erlaubt.

Neben Hyperlink unterstützt der TMS320C6678-Multicore-DSP auch Standard-Highspeed-Schnittstellen, einschließlich Serial-RapidIO (Version 2), PCI-Express Gen2, Gbit-Ethernet und einen integrierten Ethernet-Switch. Darüber hinaus sind die Schnittstellen I2C, UART, TSIP und 16-bit-EMIF sowie eine allgemeine CMOS-E/A-Schnittstelle enthalten.

Die Netzwerkfähigkeit des Gerätes wird durch einen Netzwerk-Co-Pro-zessor mit Paket- und optionalem Sicherheitsbeschleuniger gewährleistet.

Der Paketbeschleuniger kann bis zu 1,5 Mio. Pakete/s verarbeiten und erlaubt die Verwendung einer einzigen IP-Adresse für das gesamte Multicore-C6678-Gerät. Dadurch können mehrere Geräte effizienter im Netzwerk verbunden werden. Mit Multicore-DSPs können Verarbeitungsprozesse besser verteilt werden.

Indem der Prozessor näher an das Datenerfassungssystem herangerückt wird, kann der Datendurchsatz im System gesenkt werden. Dies steht im Gegensatz zu Systemen mit einem großen Zentralprozessor, in denen alle erfassten Daten zum Prozessor geleitet werden müssen. Sowohl die Komplexität von Systemen wie auch der Datenverkehr auf dem Bus über mehrere Teilsysteme hinweg nehmen ab, wodurch die Stromaufnahme enorm reduziert wird.

Die Autoren:

Murtaza Ali betreut im System- and Anwendungs-Entwicklungszentrum von Texas Instruments die Forschungs- und Entwicklungsarbeiten zu Hochleistungs-Signalverarbeitungsanwendungen mit dem Hauptaugenmerk auf DSP-Anwendungen. Er erwarb seinen Ph.D. an der University of Minne-sota, hält15 Patente in den USA und hat über 30 Artikel in moderierten Foren und Einladungsforen veröffentlicht. Darüber hinaus ist er leitendes Mitglied des IEEE. (epic@ti.com)

Kenneth Nesteroff hat die Bradley University in Peoria, Illinois, mit einem Bachelor in Elektrotechnik abgeschlossen. Er ist Business Development und Marketing Manager für medizinische und industrielle Bildgebung bei Texas Instruments. Dieser Bereich ist Teil der Multicore-DPS-Lösungsgruppe. In seiner Funktion ist er zuständig für das Unternehmenswachstum, die strategische Entwicklung sowie die Stärkung und Pflege der Beziehungen mit Kunden aus dem Bereich medizinischer und industrieller Bildgebungssysteme. (epic@ti.com )

- Industrielle Inspektionssysteme erleichtern die Fehlersuche

- Signalverarbeitung mit Multicore-DSP

- Das Prozessor-Arbeitspferd