Si vs. SiC

Wie leistungsfähig sind SiC-MOSFETs?

Fortsetzung des Artikels von Teil 1

Überlegungen zur EMV

Den elektromagnetischen Störaussendungen sollten bei rein SiC-bestückten Designs mit entsprechend höheren Schaltfrequenzen mehr Beachtung geschenkt werden. Im vorliegenden Design wurden einige praxisgerechte Konzepte angewandt, um die aus den hohen Frequenzen resultierenden Störaussendungen in Grenzen zu halten.

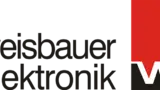

Die hohen Schaltfrequenzen und das schnelle Schalten von SiC-MOSFETs haben zur Folge, dass die Drain-Spannung viel leichter ins Schwingen gerät; das ist hauptsächlich auf die parasitäre Kapazität der Drossel zurückzuführen. Beim Ein- und Ausschalten der schaltenden Bauelemente kommt es zu hochfrequenten Resonanzen zwischen der parasitären Kapazität der Drossel und der Streuinduktivität des geschalteten Stromkreises, als deren Folge sich starke Oszillationen einstellen. Um das Schwingen bei hohen Frequenzen einzudämmen, ist es empfehlenswert, die Drossel mit einer einlagigen Wicklung anzufertigen. Bild 3 offenbart die unterschiedlichen parasitären Kapazitäten von Drosseln mit ein- und zweilagigen Wicklungen. Die einlagige Wicklung kann die parasitäre Kapazität drastisch verringern, ohne die induktive Kopplung zu beeinträchtigen. Die Folge ist eine geringere Schwingneigung an Uds, woraus reduzierte elektromagnetische Störaussendungen resultieren.

Minimieren der Stromschleifen-Fläche beim Leiterplatten-Layout

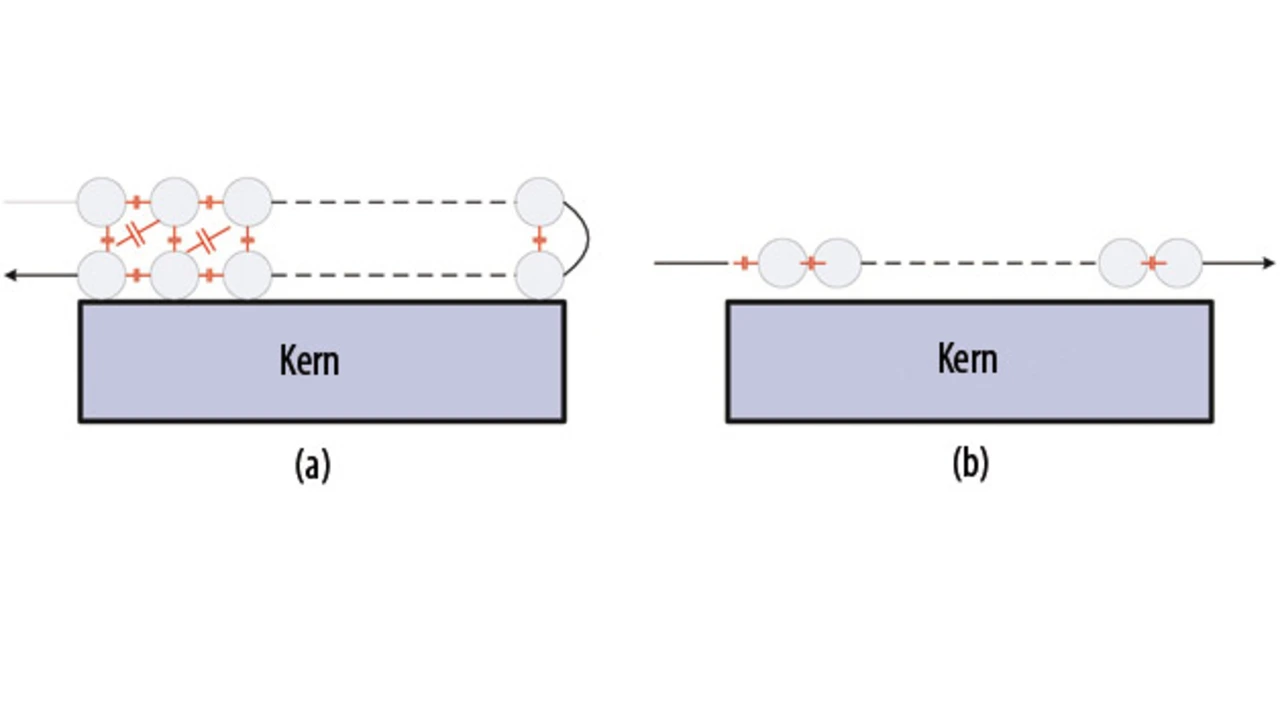

Bild 4 zeigt die wichtigsten Stromkreise eines Aufwärtswandlers. Insbesondere die mit Loop 1 und Loop 3 bezeichneten Stromkreise weisen hohe Spannungs-Anstiegsgeschwindigkeiten auf, d.h. hohe dU/dt-Werte. Minimiert man beim Leiterplatten-Layout die von diesen Stromkreisen umschlossene Fläche, so erreicht man eine minimale Streuinduktivität, was wiederum die Schwingneigung am Schaltknoten verringert. Im vorliegenden Design wird die Drossel unter der Leiterplatte angeordnet. Dies lässt kurze Verbindungen zum SiC-MOSFET und zur Ausgangsdiode zu und minimiert die von Loop 1 und Loop 3 umschlossene Fläche. Da ein SiC-MOSFET sehr schnell schaltet, ist auch der für die Gate-Ansteuerung dienende Stromkreis Loop 2 wichtig für das Leiterplatten-Layout. Die Verwendung einer Vierleiter-Verbindung mit separater Source-Rückführung wird dringend empfohlen.

Die Gate-Treiber-Tochterkarten sind für eine möglichst direkte Ansteuerung der SiC-MOSFETs in der Nähe des MOSFET-Kühlkörpers angeordnet. Die Masse-Anschlüsse der Gate-Treiber-Karten sind außerdem eigenständig mit der Source des SiC-MOSFET verbunden. Verglichen mit Silizium-Schaltbausteinen weisen SiC-MOSFETs eine geringe Transkonduktanz auf. Die Ein- und Abschaltzeiten und Schaltverluste des SiC-Bausteins stehen deshalb in engem Zusammenhang mit der Übergangszeit der Gate-Spannung. Ein härteres Ansteuern des Gate durch Reduzieren des externen Gate-Widerstands führt direkt zu geringeren Schaltverlusten und einem höheren Wirkungsgrad. Um die Auswirkungen kurzer Anstiegs- und Abfallzeiten auf das Gate abzumildern, kann ein externer Gate-Widerstand als Dämpfungswiderstand verwendet werden. Allerdings muss bei der Dimensionierung dieses externen Gate-Widerstands zwischen EMI-Eigenschaften und Wirkungsgrad abgewogen werden: Ein niedrigerer Widerstandswert kommt zwar dem Wirkungsgrad zugute, hat aber eine geringere Dämpfungswirkung.

Minimieren der leiterplattenbedingten parasitären Kapazität

Besonderes Augenmerk muss den Koppelkapazitäten zwischen den Gate- und Drain-Leiterbahnen auf der Leiterplatte gewidmet werden, denn schnell schaltende MOSFETs können extrem hohe du/dt-Werte erreichen. Jegliche Kopplung der Spannungsanstiege am Drain-Anschluss in die Gate-Schaltung kann die korrekte Ansteuerung des Bausteins über die Gate-Elektrode beeinträchtigen. Bei den SiC-MOSFETs sind außerdem die internen Miller-Kapazitäten Cgd - im Datenblatt als Crss bezeichnet - extrem gering. Das Design sorgt deshalb Layout-seitig für geringe, unter der internen Kapazität des Bausteins liegende Koppelkapazitäten, damit die Steuerbarkeit des Bausteins über die Gate-Schaltung gewahrt bleibt. Drain- und Gate-Pin sind unter Verzicht auf parallel verlaufende Leiterbahnen separat auf der Ober- und Unterseite der Leiterplatte angeordnet (Bild 5), so dass übermäßige parasitäre Kapazitäten zwischen Drain und Source vermieden werden.

- Wie leistungsfähig sind SiC-MOSFETs?

- Überlegungen zur EMV

- Zweikanaliger Aufwärtswandler im Interleaved-Betrieb

- Vorteil SiC