GaN-Transistoren in Stromversorgungen

Neue Stufe der Leistungsfähigkeit

Fortsetzung des Artikels von Teil 1

Zero Voltage Switching (ZVS)

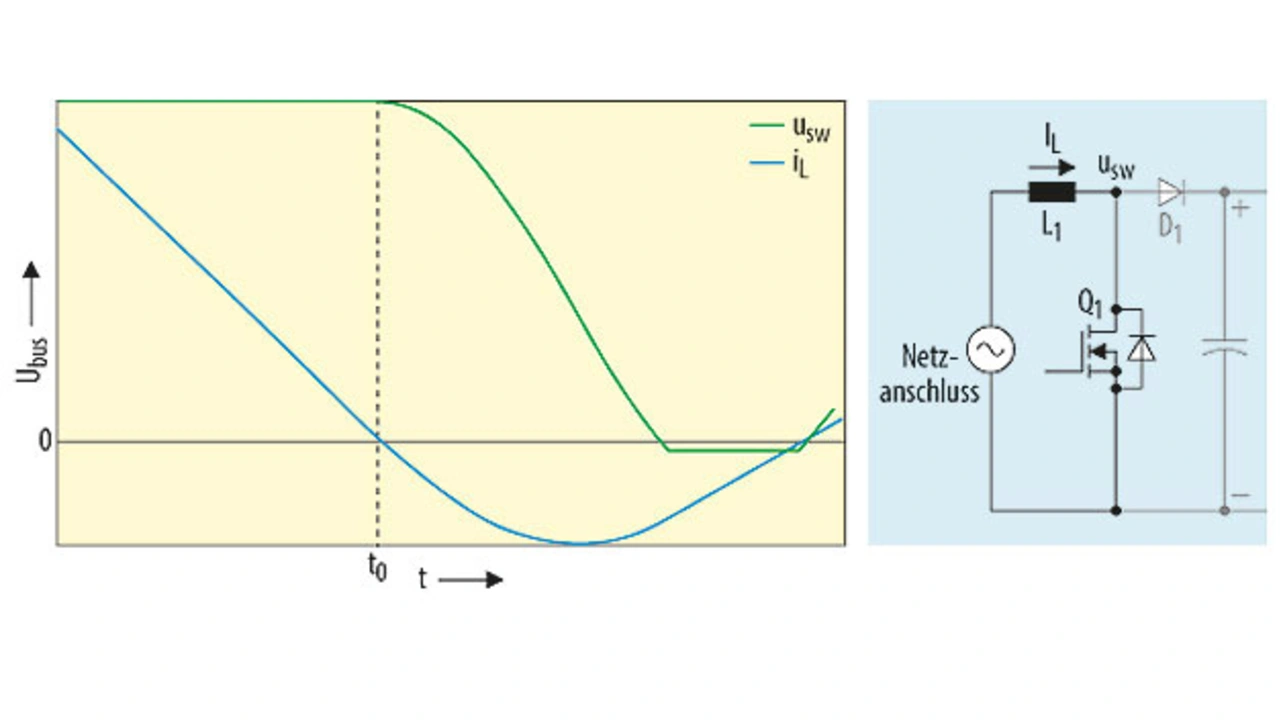

Als ein einfaches Beispiel für Zero Voltage Switching kann wieder der vorherige PFC-Aufwärtswandler betrachten werden – nur ist dieses Mal die Regelung anders: Anders als im Continuous Conduction Mode (CCM) kann der Strom in der Induktivität in jedem Schaltzyklus Null werden. Das bedeutet natürlich, dass die Restwelligkeit (Ripple-Strom) der PFC-Stufe deutlich größer ist und damit auch der Effektivstrom (RMS-Strom) sowie die entsprechenden Leitungsverluste. Allerdings kann so der Induktor vollständig entladen werden – die Voraussetzung für eine verlustfreie Kommutierung der Diode, also ZVS.

Das Beispiel in Bild 2 verdeutlicht den Prozess. Wenn der Induktor-Strom Null erreicht, ist die entsprechende Ersatzschaltung ein LC-Schwingkreis, wobei sich die Kapazität aus der Ausgangskapazität des Schalters plus der parasitären Kapazität der Diode und der Induktivität zusammensetzt – und nicht aus dem Zwischenkreis-Kondensator des DC-Busses (dieser ist durch die Diode gesperrt). Im initialen Zustand der Schaltung ist der Kondensator C mit der Zwischenkreis-Spannung geladen und bei t0 (Resonanz) wird er auf die negative Zwischenkreis-Spannung einschwingen. Der Schalter wird allerdings die Spannung begrenzen, da 0 V überschritten werden. Dieser Betriebsmodus der PFC-Schaltung wird als Critical Conduction Mode (CrCM) bezeichnet.

Das Konzept, die kleinen, in den Parasiten der Schaltung, z.B. der Spule, oder im Leistungsschalter gespeicherten Energien zu nutzen, ist weit verbreitet, um ZVS in unterschiedlichen Topologien und Regel-Strategien zu implementieren.

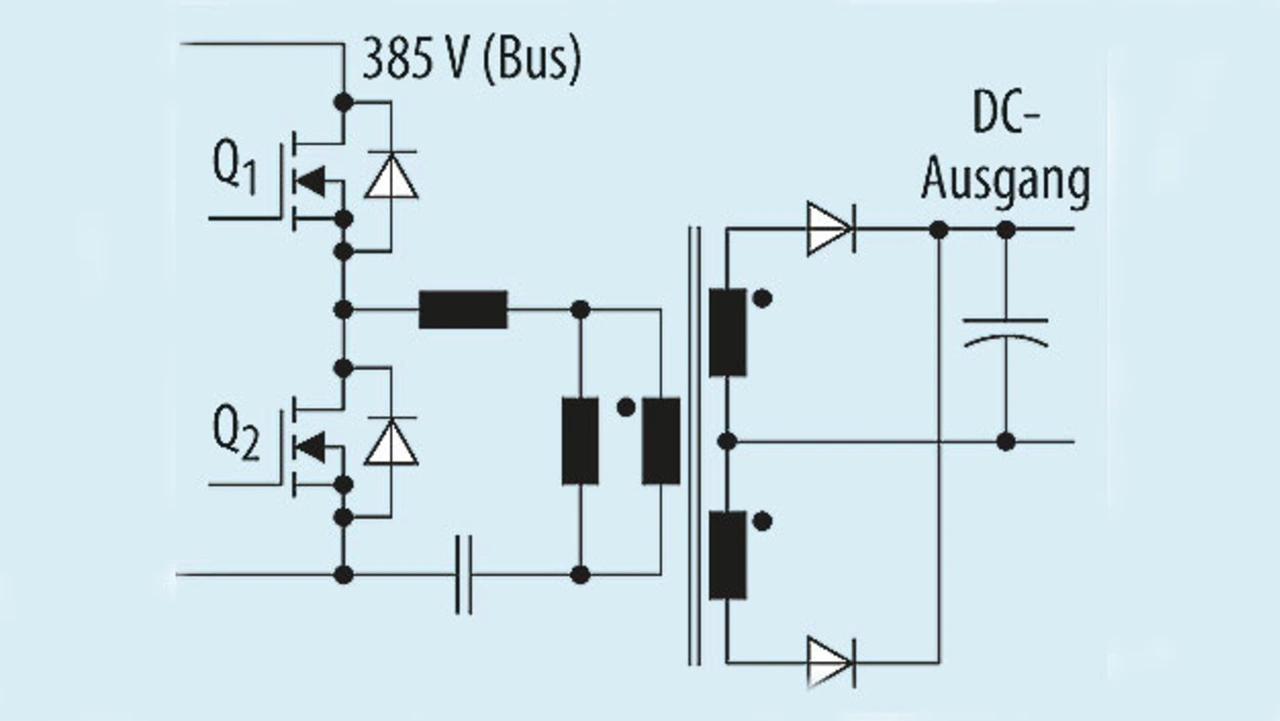

Der LLC-Konverter (Bild 3) ist ein gutes Beispiel für eine DC/DC-Stufe, die Resonanz nutzt, um ZVS auf der Sekundärseite einer Stromversorgung zu erreichen. Wie bereits erwähnt, kann ZVS grundsätzlich mit jeder Art Schalter durchgeführt werden; allerdings gibt es hier einen wichtigen Unterschied zwischen konventionellen Silizium-FETs und GaN-HEMTs. Die wesentlich kleinere Kapazität und dadurch wesentlich kleinere Ladung eines GaN-HEMT erfordert weniger Energie und ermöglicht kürzere Totzeiten im Vergleich zu Silizium-FETs, um ZVS zu erreichen. Die kürzere Totzeit ist der Hauptgrund dafür, dass ein LLC-Konverter mit deutlich höheren Frequenzen betrieben werden kann und zwar ohne zusätzliche Verluste in Kauf nehmen zu müssen.

Normalerweise benötigt die ZVS-Wandlung in einer LLC-Schaltung nur einen sehr kleinen Anteil an der gesamten Resonanzperiode – wie beispielsweise etwa 330 ns für eine typische Betriebsfrequenz von 150 kHz, also etwa 5 % der Periode. Wird aber die Frequenz vervierfacht, also auf 600 kHz erhöht, dann werden aus den 5 % (je Flanke) schon 20 %. Die Zeit für die Kommutierung (auch bekannt als Totzeit) ist eine »nichtproduktive« Zeit der Leistungswandlung – also mehr oder weniger die Wartezeit. Nimmt die Totzeit einen größeren Anteil an der gesamten Periode ein, dann verringert sich der produktive Anteil der Resonanzperiode, wobei der Effektivstrom aufgrund des Verhältnisses höherer Spitzenwert/Durchschnittswert deutlich ansteigt.

Anders ausgedrückt: Um die Frequenz in einer ZVS-Schaltung deutlich zu erhöhen, muss die zirkulierende Energie, die für ZVS erforderlich ist, proportional reduziert werden. Andererseits schränkt die Erhöhung des Effektivstromes auf der Primär- und Sekundärseite den Wirkungsgrad wieder ein und die Leistungsdichte kann nicht erhöht werden. Allerdings sind die Wechselwirkungen zwischen Kapazität, Ladung und Energie in modernen Hochvolt-MOSFETs (Superjunction) sehr komplex, da die Bauteilkapazität nichtlinear ist. Das gestaltet es schwierig, Bausteine allein anhand der im Datenblatt angegebenen Kapazitätswerte zu vergleichen, denn diese können sich um drei Größenordnungen abhängig von der Spannung ändern. Darüber hinaus gibt es auch einen großen Unterschied zwischen Bausteinen, die für hartes Schalten (geringe Eoss) oder ZVS-Soft-Switching (geringe Qoss) optimiert sind.

Die Grafik in Bild 4 zeigt diesen Unterschied deutlich auf. Ein leistungsfähiger Superjunction-FET mit 650 V/70 mΩ (hier in blau dargestellt) wird hier mit einem GaN-HEMT mit dem gleichen Kanal-Durchlasswiderstand (RDS(on), in rot) verglichen. Die gestrichelten Linien stehen für die Ladung (linke Achse) und die durchgezogenen Linien repräsentieren die Energie (rechte Achse) – beides gegenüber der Spannung Uds auf der x-Achse.

Es ist klar erkennbar, dass die Ladung des Superjunction-Bauteils (gestrichelte blaue Linie) steil bis zu etwa 90 % des finalen Wertes innerhalb der ersten 20 V ansteigt. Dann ändert sich der Verlauf abrupt und für die letzten 10 % der Ladung werden die verbleibenden 380 V benötigt. Dieses Verhalten ist darin begründet, wie sich die Ladung in der spaltenartigen Struktur des Superjunction-FET verteilt. Daraus ergibt sich ein interessanter Effekt: Da die erforderliche Energie, um Coss zu laden, bei kleinerer Spannung ebenfalls kleiner ist (E = ½ ∙ CU²), wird während der ersten 20 V ein sehr kleiner Anteil der Energie benötigt, selbst wenn die Kapazität bis zu diesem Punkt bereits 90 % geladen ist. Diese Nichtlinearität ist Grund dafür, dass Superjunction-FETs bei einem gegebenen Qoss relativ geringe Eoss-Werte aufweisen können – was sie gegenüber anderen Silizium-Alternativen für hartes Schalten prädestiniert. Im starken Gegensatz dazu ist ein GaN-HEMT ein lateraler Baustein, der einen nahezu linearen Verlauf für die Kapazität gegenüber der Spannung zeigt. In Bild 4 ist das als gestrichelte rote Linie erkennbar, mit einem flachen Anstieg auf einen um Größenordnungen geringeren Qoss-Wert im Vergleich zu den Superjunction-FETs. Da diese Ladung aber gleichmäßig entlang der Spannungsachse verteilt ist, erhält man für die Integration der Ladungszeiten nahezu den gleichen Endwert für Eoss im Vergleich zu den Superjunction-FETs. Dieser Zusammenhang wird im Vergleich der Tabelle deutlich.

Bestwert für einen | E-mode GaN-HEMT | |

|---|---|---|

| Qg (typ.) | 68 nC | 6 nC |

| Qoss (typ.) | 420 nC | 44 nC |

| Eoss (typ.) | 8 μJ | 7 μJ |

| Qrr (typ.) | 6000 nC | 0 nC |

Die typischen Parameter für einen 600-V-Superjunction-FET im Vergleich zu einem 600-V-GaN-HEMT. RDS(on) = 55 mΩ (nominal).(Quelle: Infineon)

Der HEMT weist eine um den Faktor 10 reduzierte Ausgangsladung Qoss auf und ist bezüglich Eoss sogar noch etwas besser als der Vergleichstyp. Um den Effekt bezüglich der Gate-Ladung Qg und der Ausgangsladung Qoss weiter zu verdeutlichen und die ZVS-Performance für beide Baustein-Typen zu evaluieren, wird die bekannte LLC-Schaltung (Bild 3) herangezogen. Auf Basis der Schaltung werden ein Si-SJ FET und ein GaN-HEMT verglichen, wobei beide mit etwa 350 kHz auf der Primärseite arbeiten, eine nominelle Zwischenkreisspannung von 385 V besitzen und bei einer Leistung von 750 W operieren.

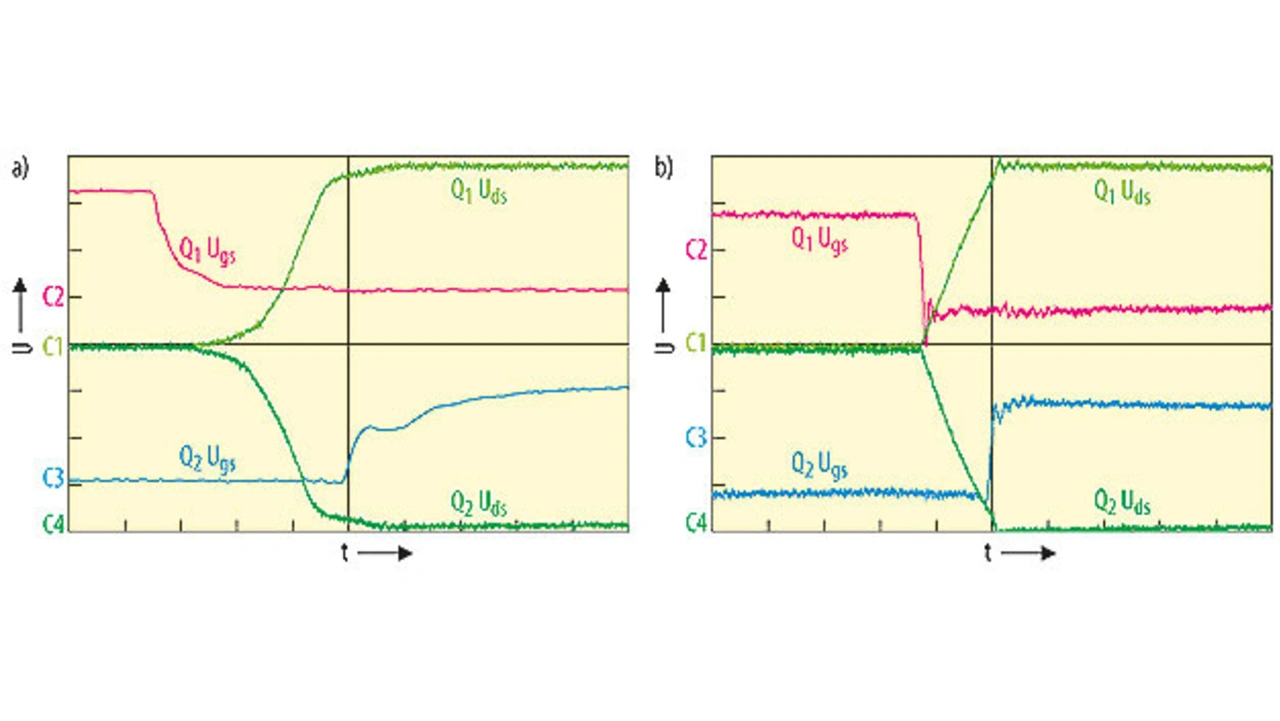

Bild 5a zeigt die Signalverläufe für den Superjunction-FET auf der Primärseite der LCC-Schaltung und Bild 5b die entsprechenden Signale für den GaN-HEMT unter gleichen Bedingungen. In Bild 5a schaltet das obere Gate aus, und die Drain-Spannung benötigt mehr als 350 ns, um von der Busspannung auf Null zu gehen.

Die nichtlineare Superjunction-Ladung erzeugt lange, flache Spannungsverläufe – auch bekannt als »Tails« –, was zu der langen Totzeit führt. Wie Bild 5a zeigt, beträgt die Totzeit 350 ns, und selbst dann, wenn das untere Gate einschaltet, ist die Spannung noch immer nicht null.

Das Einschalten, kurz bevor die Spannung null erreicht, scheint auf den ersten Blick ein kleiner Kompromiss zu sein. Tatsächlich ist es das nicht: Die Hälfte von Eoss entfällt auf 20 V der Drain-Spannung (aufgrund der in Bild 4 dargestellten Nichtlinearität). Mit anderen Worten: Die dargestellte Totzeit sollte so klein wie möglich sein, um ein möglichst optimales Verhalten ohne signifikante Einschränkungen bei Leistungsverlusten und Wirkungsgrad zu erreichen. Bild 5b zeigt die entsprechenden Signalverläufe für den GaN-HEMT. Die Gate-Spannung weist hier deutlich schnellere Abfall- und Anstiegs-Zeiten auf. Das liegt darin begründet, dass der Gate-Treiber das Gate des GaN-Bausteins aufgrund der geringeren Gate-Ladung wesentlich leichter treiben kann. Außerdem verläuft die Drain-Spannung aufgrund der geringen Qoss des HEMT wesentlich schneller und außerdem annähernd linear. Daher kann auch die Totzeit um bis zum Faktor 3 kürzer ausgelegt werden.

- Neue Stufe der Leistungsfähigkeit

- Zero Voltage Switching (ZVS)

- Ein Beispiel aus der Praxis