Testlösungen für Smart Devices

Große Herausforderungen

Fortsetzung des Artikels von Teil 1

Anforderungsspektrum der Bauteiltests

Hohe Genauigkeit und großer Spannungsbereich

Viele der vernetzten Endprodukte sind portabel. Daher ist eine lange Batterielebensdauer entscheidend. Neben sinkenden Versorgungsspannungen ist das Design auf minimale Leckströme ausgelegt. Integrierte intelligente Standby-Funktionen verlängern weiterhin die Betriebsdauer. Dass Trimmen von Bausteinreferenzen wird durch diese Gegebenheiten für ATE immer kritischer. Forcier- und Messgenauigkeiten müssen kleiner als 100 µV sein; gleichermaßen liegen zu messende Ströme im Bereich von einzelnen nA. Zugleich ist ein weiter Spannungsbereich der Quellen nötig. Zum einen sollen dadurch kleine Core-Spannungen bereitgestellt und zum anderen sehr hohe Spannungen geliefert werden, um verschiedene Parameter an den Halbleiterprozessgrenzen (zum Beispiel bei 80 V) messen zu können.

Digital-I/O und Gleichspannungs- versorgung am selben Bauteilpin

Neuartige smarte Sensoren weisen häufig nur einen einzigen Bauteilpin auf. Dieser dient der Versorgung des Chips und gleichzeitig als Datenschnittstelle, um den Sensor zu konfigurieren beziehungsweise Messergebnisse vom Sensor zu lesen. Das Testsystem legt eine stabile Spannung an, sendet über ein moduliertes Signal in der Bausteinversorgung Daten an den Baustein und empfängt strommodulierte Datensignale vom Chip. Während des kompletten Testvorgangs ist entscheidend, dass die Versorgungsspannung nicht einbricht, da ansonsten die Konfigurations- und Kalibrierdaten gelöscht würden. Daher ist es zwingend erforderlich, im µs-Bereich Glitch-frei zwischen Versorgungs- und Datenbetrieb umzuschalten. Um strommodulierte Daten vom Prüfling zu empfangen, mussten bisher mehrere ATE-Kanäle per komplexer Loadboard-Beschaltung zusammengefasst werden. Der Einsatz eines Strom-Komparators im digitalen Pattern vermeidet diesen zusätzlichen Aufwand und spart wertvolle Testsystemressourcen ein.

Hochstromfähigkeit und Zeitmessungen

Integrierte Treiberschaltungen für Aktuatoren sind über Push-Pull-H-Brücken realisiert. Entweder handelt es sich um Gate-Treiber zur Ansteuerung von externen MOSFETs oder um voll integrierte Leistungsschalter. Die Testanforderungen liegen für Gate-Treiber bei Messungen von Strömen unter 1 A. Integrierte FET-Schalter können bis zu 4 A Spitzenströme treiben. Typische Tests, die an diesen Komponenten durchgeführt werden, sind RDSon-Messungen zur Bestimmung des Drain-Source-Einschaltwiderstands oder Überstromtests zur Überprüfung von Abschaltschwellen integrierter Sicherheitsschaltungen.

Zum Prüfen von High-Side-Schaltern, die keinen Massebezug haben, ist auf dem Testsystem eine Hochstromeinheit erforderlich, die potenzialfrei (floating) realisiert ist und über den gesamten maximalen Versorgungsspannungsbereich des Prüflings referenziert werden kann. Über ein ebenfalls floatend ausgelegtes Differenzvoltmeter können sehr kleine Spannungsabfälle, die an den Schaltern auftreten, gemessen werden. Die Bestimmung der Flankensteilheit integrierter Treiberstufen wird über Pro-Pin-Hochspannungs-Zeitmesseinheiten (HV TMUs) mit zwei separaten Triggerschwellen realisiert. Über eine derartige HV-TMU-Architektur lassen sich Signalflanken im ns-Bereich an mehreren Schaltern parallel messen. Zur Ermittlung von Verzögerungszeiten vom Schreiben eines Registerinhalts bis zum Reagieren einer Treiberstufe ist ein kalibriertes Zeitsystem der beteiligten ATE-Funktionen, -Domains und -Karten nötig.

Pattern-kontrollierter Test

Jobangebote+ passend zum Thema

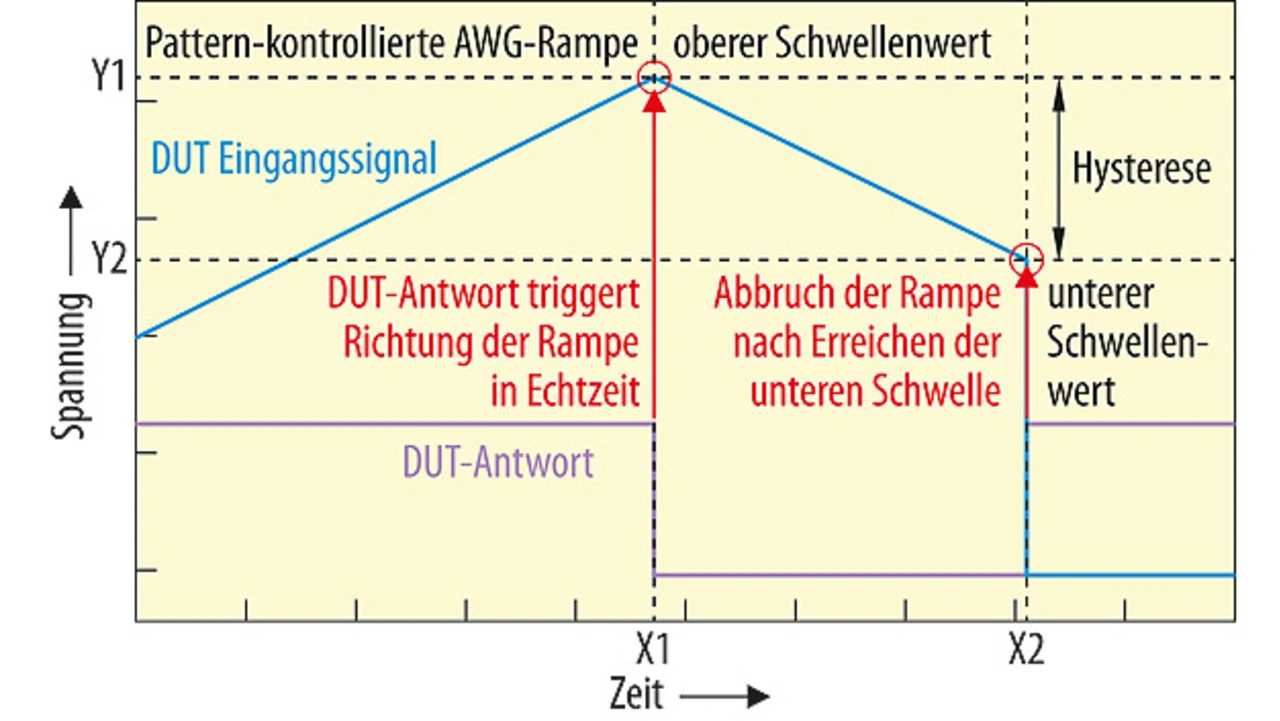

Weitere häufig vorkommende Messungen dienen der Ermittlung von Schaltschwellen. Hierzu werden üblicherweise diskrete Spannungswerte in Form von Rampenschritten an den Prüfling angelegt und die Reaktion an einem anderen Anschluss oder einem wechselnden Registerinhalt überprüft. Diese Methodik ist sehr langsam, da eine ständige Interaktivität zwischen neu zu programmierenden Spannungen und Auswerten der daraus resultierenden Bausteinantworten erforderlich ist. Eine wesentliche Testzeitreduktion kann durch eine automatische Feedback Loop erzielt werden. Die Bausteinantwort wird im digitalen Pattern ausgelesen. Das Pattern verzweigt in Echtzeit, je nach Antwort, entweder in die eine oder andere Richtung. Mit Hilfe dieser Methodik lassen sich unterschiedliche Abläufe realisieren, um Schaltschwellen auch mit Hysterese zu ermitteln. Dies geschieht entweder über lineare Rampenverfahren oder über Binary-Search-Algorithmen zur Annäherung an einen Zielwert. Viele der in den Bausteinen eingesetzten Bussysteme sind differenziell ausgeführt, wie zum Beispiel der CAN- oder PSI5-Bus. Daher ist eine differenzielle Treiber- und Empfängerfähigkeit der Digitalfunktionen von Vorteil, um die Beschaltung auf dem Loadboard zu minimieren.

Test integrierter ADCs und DACs

Gerade im Bereich von integrierten A/D-Umsetzern ist in den letzten Jahren ein großer Fortschritt zu verzeichnen. Auf dem Markt verfügbare und integrierbare Bibliotheksblöcke etablieren sich. Bei der Auflösung ist ein Trend von 10 bis 12 bit in Richtung 16 bis 18 bit zu erkennen. Die LSB-Größe liegt oftmals im Bereich von unter 10 µV, mit Genauigkeitsanforderungen im Bereich von 1 bis 4 LSB. Dies hat den entscheidenden Vorteil, dass ein hoher Dynamikbereich erzielt wird und aufwändige Vorstufen zur Konditionierung der Eingangssignale vermieden werden. Dies resultiert in einer Vereinfachung des Chipdesigns und reduziert die Kosten deutlich. Für den Halbleitertest bedeutet dies, dass eine Bereitstellung von hochlinearen Signalgeneratoren nötig wird, die zum einen eine hohe DC-Genauigkeit zur Ermittlung von Gain- und Offset-Fehlern benötigen und zum anderen eine gute Signaltreue mit hoher THD, SNR und SFDR zur Bestimmung von AC-Parametern aufweisen. Zur Bestimmung von Wandlerlinearitäten kommt entweder ein Rampen- oder das Sinushistogramm-Verfahren zum Einsatz. Der AC-Histogramm-Methode kommt zugute, dass sich über die relativ einfache Tiefpassfilterschaltung sehr reine Sinussignale erzeugen lassen und gerade bei höheren Genauigkeitsanforderungen meist bessere Ergebnisse erzielt werden.

- Große Herausforderungen

- Anforderungsspektrum der Bauteiltests

- Unsicherheiten im Markt und deren Auswirkung auf ATE-Systeme