Design-Praxis: Systemsimulation (Teil 2)

Auslegung der High-Speed-Signalleitungen

Fortsetzung des Artikels von Teil 3

Feldberechnung der Signalintegrität

Die vorherige Diskussion wurde hauptsächlich aus der Darstellung einer Übertragungsstrecke als Leiternetzwerk abgeleitet. In der Praxis werden die S-Parameter jedoch aus Feldberechnungen, unter Berücksichtigung des geometrischen Aufbaus der Leiterbahnen, bestimmt. Hierbei werden die Maxwellschen Gleichungen unter Berücksichtigung von dielektrischen und metallischen Materialeigenschaften gelöst. Bild 1 zeigt die Ausbreitung von Strömen (mitte) bzw. elektrischen Feldern (unten) entlang einer Mikrostreifenleitung. In Analogie zum Leiternetzwerk sind das die Ströme entlang der Serieninduktivitäten und die elektrischen Felder in den Parallelkapazitäten. Die Wirbelstromeffekte haben zur Folge, dass sich Stromverteilungen mit möglichst geringen Induktivitäten einstellen. Damit wird Wirbelstromeindringtiefe in Kupfer sehr klein, z.B. 2 µm bei 1 GHz, der Widerstandsbelag in den Leiterbahnen steigt. Weiterhin laufen Hin- und Rückströme möglichst nah beieinander.

Jobangebote+ passend zum Thema

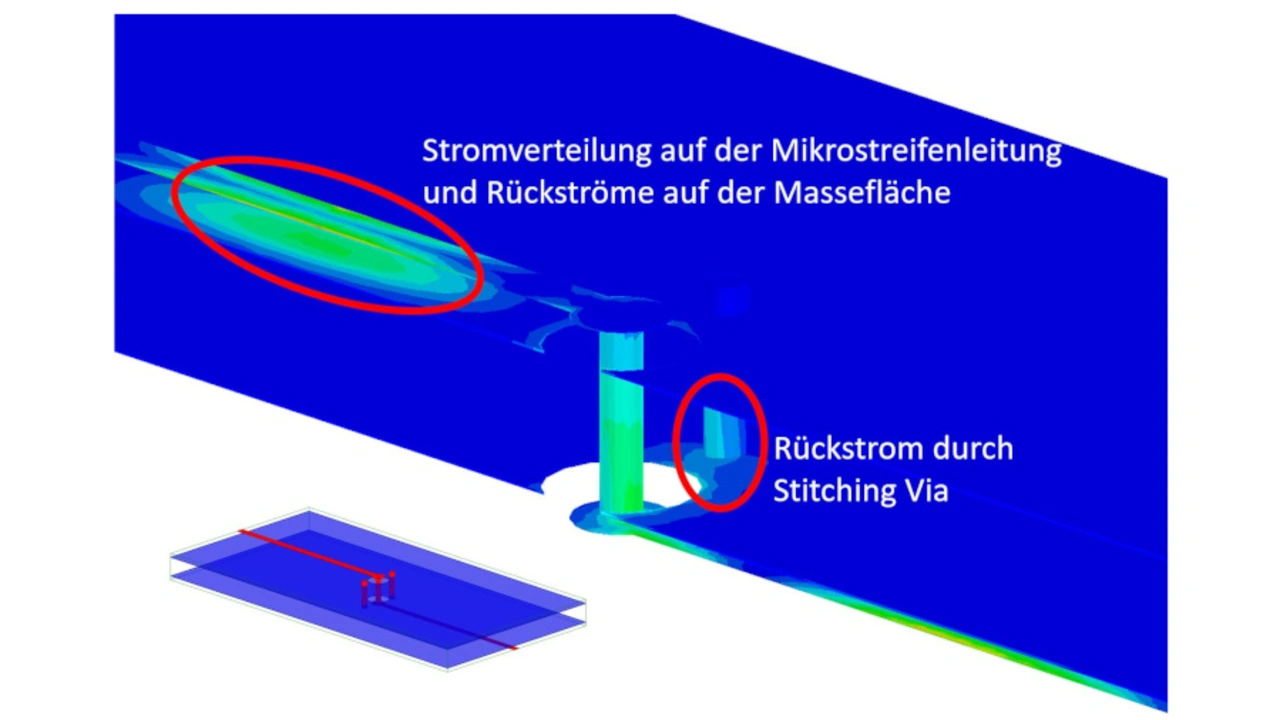

Bild 5 zeigt erneut die Stromverteilung bei einer Mikrostreifenleitung mit Viadurchführung durch zwei Masseebenen. Die Rückströme auf der Massefläche konzentrieren sich in direkter Nähe der Mikrostreifenleitung. Dort ist die Stromdichte auf der Unterseite, die der Massefäche zugewandt ist, und an den Kanten am größten. An der Oberseite in Mitte der Leitung fließen hingegen kaum Ströme.

Dieses Verhalten der Hin- und Rückströme muss natürlich auch bei dem Via selbst berücksichtigt werden. Es werden Stitching Vias zwischen den Masseflächen benötigt. Der Abstand der Stiching Vias zum Via der Signalleitung führt zu einem erhöhten induktiven Belag im Via-Bereich. Die Radien der Viabohrungen, der Pads und der Antipads, also der Aussparungen in der Masseebene, bewirken gemeinsam mit der Permittivität des Substrats die kapazitiven Kopplungen im Via-Bereich.

In Plots für TDR-Impedanzen lassen sich Vias relativ leicht identifizieren und bewerten. Der Zusammenhang mit kapazitiven und induktiven Belägen sowie ein Verständnis der Stellschrauben erlauben es, mit Hilfe von Feldsimulationen sehr schnell und zuverlässig Designs zu verbessern. Ohne dass reale Prototypen gefertigt und vermessen wurden.

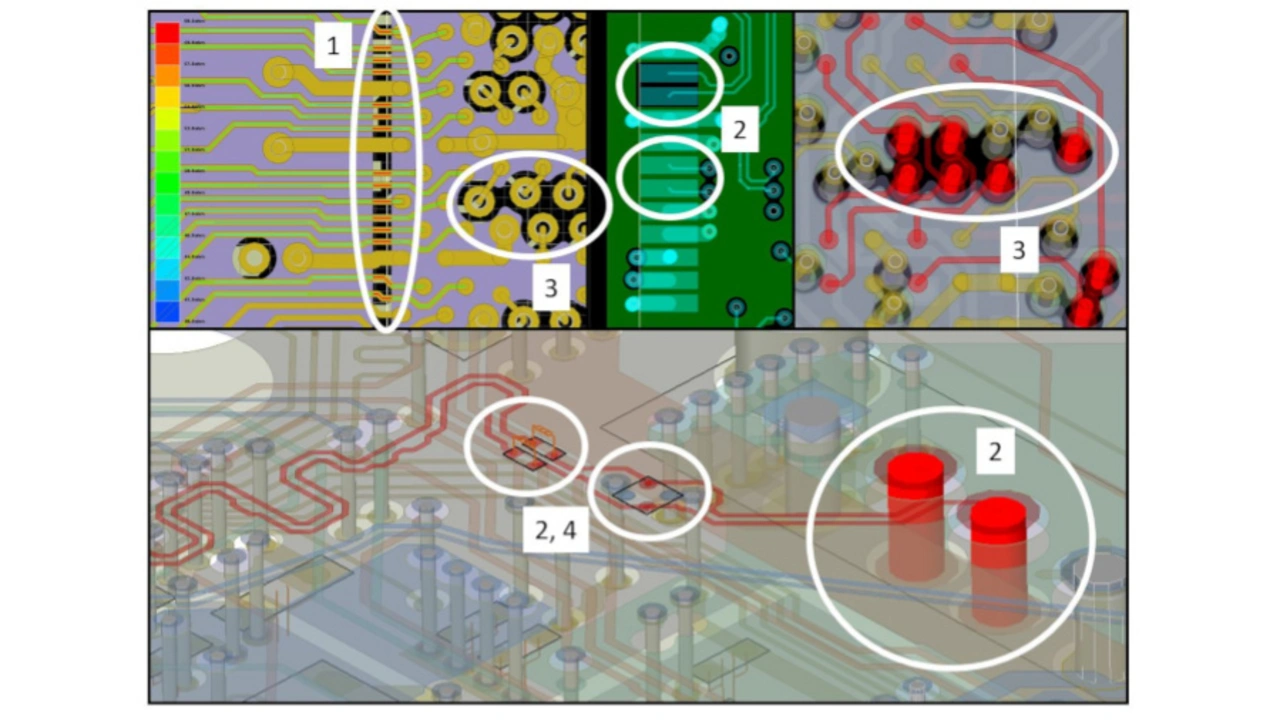

Mit Ansys SIwave lassen sich diese Art von Untersuchungen sehr effizient durchführen. Etwa ein Impedanz-Scan für Signalleitungen der, wie (Bild 6, oben links) zeigt, die charakteristische Impedanz von Leiterbahnen aufgrund der Querschnittsgeometrie bestimmt. Diese Analyse zeigt deutlich, wann Referenzebenen gewechselt werden. In Bild 6 sind Signalleitungen über einen Schlitz verlegt, was zu einer stark erhöhten Impedanz an dieser Stelle führt. Auf diese Weise können schnell kritische Leiterbahnbereiche identifiziert werden. Für detailliertere Analysen werden in SIwave zuerst die S-Parameter der zu untersuchenden Übertragungsstrecken bestimmt. Hierbei werden alle wichtigen Beiträge wie z.B. Kopplungen benachbarter Leiterbahnen, Viadurchführungen, Rückstrompfade, kapazitive Kopplungen von Pads an Ebenen und Resonanzen in den Versorgungsebenen berücksichtigt.

Anhand dieser S-Parameter können dann auch TDR-Impedanzen und transiente Signalformen bestimmt werden. Dies reicht bis zur Einbindung von IBIS-Modellen (Input/Output Buffer Information Specification) für eine realitätsnahe Beschreibung zur Signalerzeugung durch den IC: dann wird das Design mit Hilfe von Augendiagrammen und Bit-Fehlerraten beurteilt.

Bild 6 zeigt dazu einige typische Szenarien, die auf einer Leiterplatte vorkommen können:

- Wenn Leiterbahnen die Referenzebene wechseln, z.B. bei der Überquerung eines Schlitzes, wird der Rückstrompfad unterbrochen. Falls sich dies aus bestimmten Gründen nicht vermeiden lässt, sollten nach Möglichkeit Stitching-Kondensatoren verwendet werden, um hochfrequente Rückströme zu ermöglichen. In einem ähnlichen Szenario wechselt eine Leitung mit einem Via die Lage und dabei von einer Referenzierung auf Masse zu einer Referenzierung auf VCC.

- Viele Bauteile und auch Steckverbinder für Schnittstellen haben ein Landing, das große Pads oder Bohrungen für Einpresskontakte benötigt. An diesen Stellen liegen oft zu hohe kapazitive Kopplungen, die z.B. durch Aussparungen in der Referenzlage darunter verringert werden sollten (Bild 6, oben Mitte).

- Oft werden mehrere Leitungen mit benachbarten Vias durch eine große Aussparung in den Referenzebenen geführt. Dies führt häufig zu erhöhten Induktivitäten und dem Verlust der Referenzebene. Hier muss auf nahe gelegene Rückstromvias und nicht zu große Abstände zur Referenzfläche geachtet werden.

- Bauteile zur Entstörung und zum Schutz wie Gleichtaktdrosseln oder DC-Blockkondensatoren stören auch die Signalausbreitung und müssen geschickt ausgewählt werden.

- Nicht hier abgebildet sind Mikrovias und vergrabene Vias sowie Testpunkte. Diese haben alle Auswirkungen auf die Signalübertragung. Die Untersuchung der Einfüge- und Reflexionsdämpfung sowie der TDR-Impedanzen mit Hilfe von Feldsimulationen hilft, alle diese Szenarien zu verbessern, oder die Grenzen solcher Designmaßnahmen auszuloten. Oft führt dies zu einer Abwägung zwischen ökonomischen Aspekten und technischen Notwendigkeiten. Um das Thema der Rückströme besser zu beherrschen werden bei sehr hohen Datenraten, Taktsignalen und langen Datenleitungen, die Übertragungsleitungen symmetrisiert: es werden also differentielle Paare aus Hin- und Rückleitung gebildet, wie (Bild 6, unten) zeigt. (speziell für periphere Schnittstellen wie USB, PCIe, SATA, LVDS) Damit muss der Rückstrom nicht in den Referenzflächen fließen und die Übertragung wird robuster, allerdings unter dem Mehraufwand einer zusätzlichen Leiterbahn.

Bei peripheren Schnittstellen ist zu beachten, dass das Dämpfungsbudget auf der Seite des eingebetteten Systems eingehalten wird. Auch hier ist die Impedanzanpassung der Leitung notwendig. Bei entsprechender Terminierung wird der Verlust dann durch die Einfügedämpfung beschrieben. Ein wesentlicher Aspekt ist hier natürlich wieder ein gutes, angepasstes Landing des Steckverbinders auf der Platine. Es entstehen aber auch Verluste im FR-4 der Platine und aufgrund der Materialschwankungen bei FR-4 kann es zu leichten Fehlanpassungen kommen, die Reflexionen verursachen und somit das Dämpfungsbudget negativ beeinflussen.

Eine weitere Thematik sind energieeffiziente Terminierungsschemen mit Spannungsreferenznetzen sowie Fly-By-Topologien, bei denen mehrere Empfänger an einer Leitung sitzen. Diese sind meist hochohmig abgeschlossen, um das passierende Signal nicht zu stören. Oft sitzen diese aber an kurzen, abgezweigten Leiterstücken: dies bewirkt Reflexionen, die wiederum die Signale verfälschen.

- Auslegung der High-Speed-Signalleitungen

- Signalleitungen als elektrische Leiternetzwerke

- Das Übertragungsverhalten quantifizieren

- Feldberechnung der Signalintegrität

- Fazit & Ausblick