Toolchain

Designflow für IoT-Edge-Sensoren

Fortsetzung des Artikels von Teil 1

Notwendigkeit integrierter Designflüsse

Unabhängig von der Unternehmensgröße nutzen Designer die Vorteile intelligenter Sensoren und bringen neue Ideen auf den IoT-Markt. Diese neue Entwicklergeneration fokussiert erneut auf Hardware-Design: sie gestaltet die Designabläufe neu und stellt progressive Erwartungen an das Gesamtsystem. Typischerweise wird in kleinen Teams entwickelt: um schnell, einfach und kosteneffizient ein funktionierendes Gerät herzustellen werden integrierte Designabläufe notwendig.

Auf dem IoT-Markt ist die Entwicklung eines Proof-of-Concept zur Systemvalidierung gefordert. Zur schnellen Implementierung von Produkten verwenden Designteams integrierte Designabläufe, mit denen sie alle für das sensorgesteuerte IoT-Edge-Device notwendigen Teile entwickeln können. Dazu gehören: Sensorelemente, analoge Schaltungsschnittstellen, Analog-Digital-Logik, digitale Logik und HF. Und das alles zu geringeren Kosten als im herkömmlichen IC- und Systemdesign.

Um intelligente, sensorbasierte IoT-Systeme zu entwickeln, verwenden viele Designteams, darunter auch Knowles und InvenSense (TDK) die integrierte IC-Design- und Verifikationslösung von Tanner.

Jobangebote+ passend zum Thema

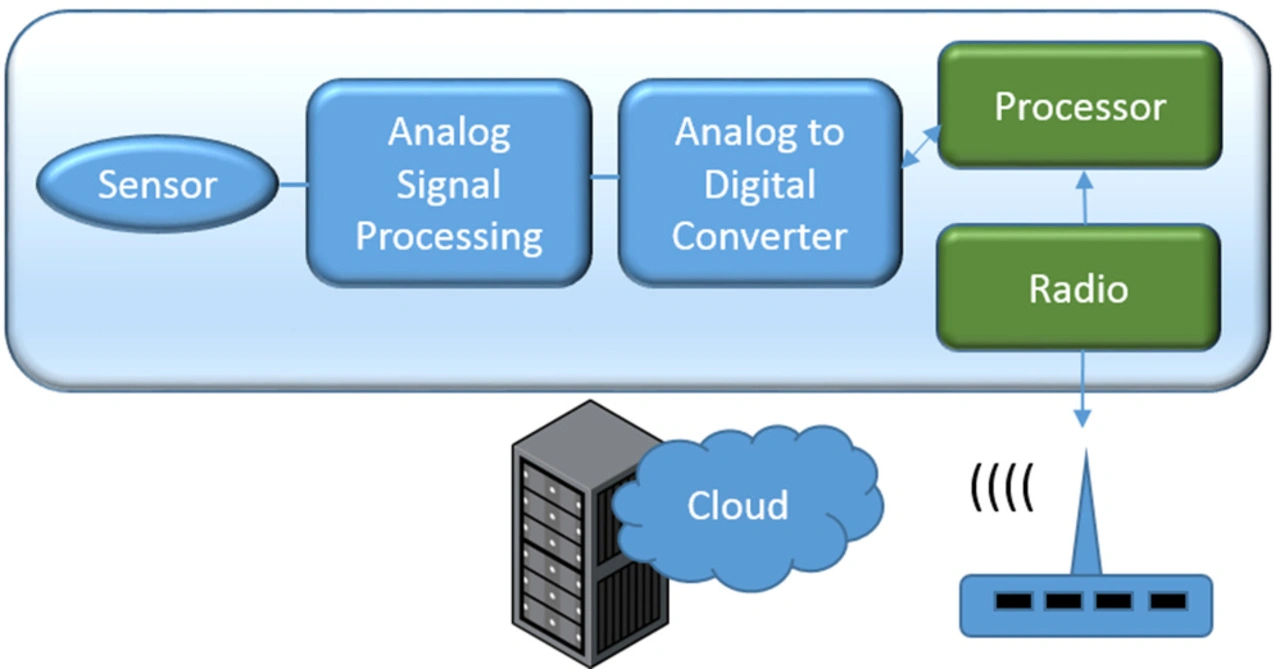

Ihre Motivation: Der Entwurf eines sensorbasierten IoT-Edge-Devices (Bild 3) ist aufgrund der vielen beteiligten Designdomänen anspruchsvoll. Die Entwicklung eines Edge-Devices, das die Elektronik des traditionellen CMOS-IC-Flows und MEMS-Sensoren auf einem Silizium-Die kombiniert, scheint jedoch unmöglich: tatsächlich vereinen viele IoT-Edge-Bausteine mehrere Dies in einem Gehäuse und trennen so die Elektronik vom MEMS-Design.

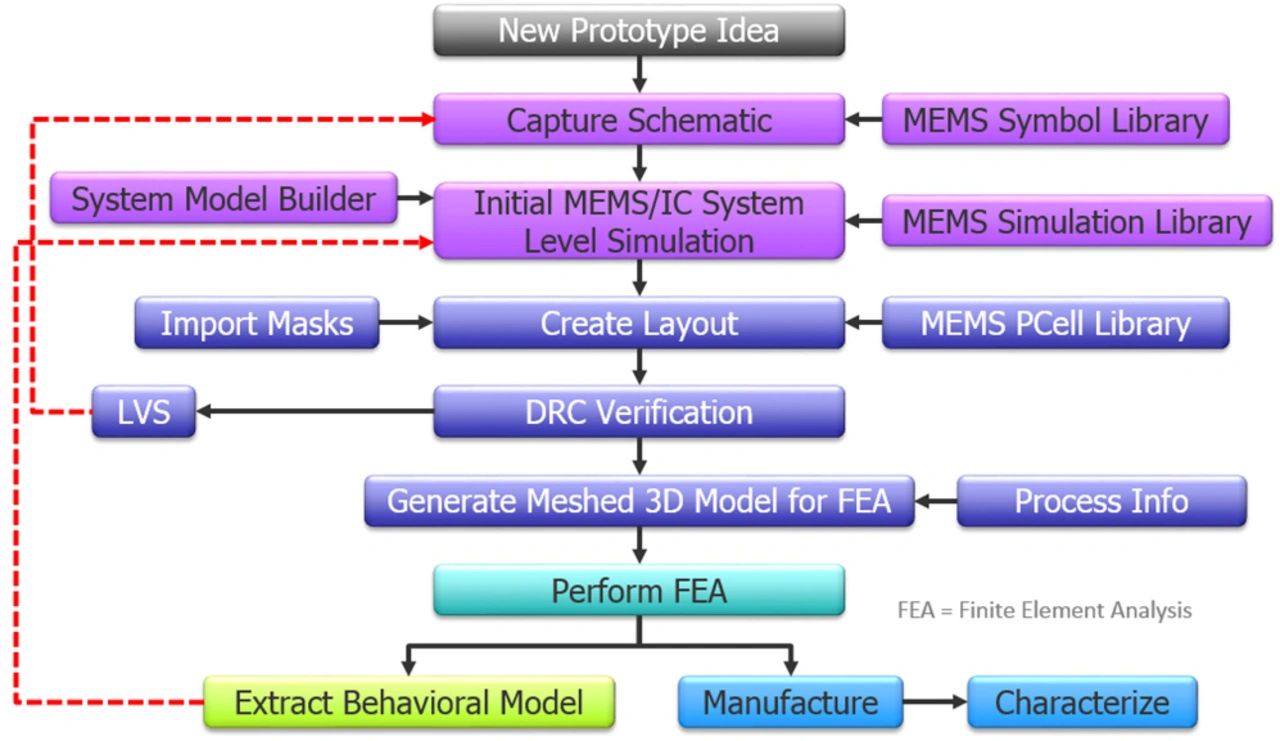

Der in Bild 4 dargestellte Designablauf beinhaltet Techniken für die Entwicklung von IoT-Edge-Devices und die Verifizierung intelligenter sensorbasierter Designs mit einem oder mehreren Dies.

Das Design von IoT-Edge-Devices erfordert, dass analoge, digitale, HF- und MEMS-Designdomänen gemeinsam entwickelt werden und zusammenarbeiten, insbesondere wenn sie sich auf dem gleichen Die befinden. Auch wenn die Komponenten auf einzelne Dies abzielen, die zusammen gebondet werden sollen, müssen sie während des Layouts und der Verifikation zusammenarbeiten. Das Designteam muss ein gemischtes Analog- und Digital-, HF- und MEMS-Design erfassen, den Chip layouten und sowohl Komponenten- als auch Top-Level-Simulationen durchführen.

Das Design von Elektronik und MEMS auf einem Die beinhaltet folgende interessante Punkte (aus Bild 3):

- Schaltpläne können ICs und MEMS enthalten. ICs werden mit SPICE-Modellen modelliert. MEMS verwenden Verhaltensmodelle, die direkt in den physikalischen Domänen wie Mechanik, Elektrostatik, Fluidik und Magnetik modelliert werden. Das Erfassen der MEMS wird von der MEMS-Symbolbibliothek innerhalb der Schematic-Capture-Domäne unterstützt.

- Um die erste Simulation von MEMS und IC zu unterstützen, erstellt der System-Model-Builder ein MEMS-Modell mit analytischen Gleichungen in SPICE oder Verilog-A. In Kombination mit der MEMS-Simulationsbibliothek kann der Designer zunächst verifizieren, ob das gesamte Design wie erwartet funktioniert.

- Mit Hilfe der MEMS-PCell- (parametrisierte Zelle) Bibliothek können Designer dann das Design in einer Layout-Umgebung erstellen. Die Bibliothek bietet für viele MEMS grundlegende Layout-Generatoren, die als Ausgangspunkt verwendet werden können. Die Bibliothek enthält aktive, passive, thermische, optische, Test-, Fluidik- und Resonator-Elemente.

- Die Designer können anschließend ein 3D-Geometriemodell zur Ansicht, zum virtuellen Prototyping sowie zum Export in Finite-Elemente-Analyse- (FEA) Tools erstellen.

- Mit dem Compact-Model-Builder, der Modellierungstechniken mit reduzierter Ordnung verwendet, erstellen Designer aus den FEA-Ergebnissen Verhaltensmodelle für die endgültige Simulation auf Systemebene.

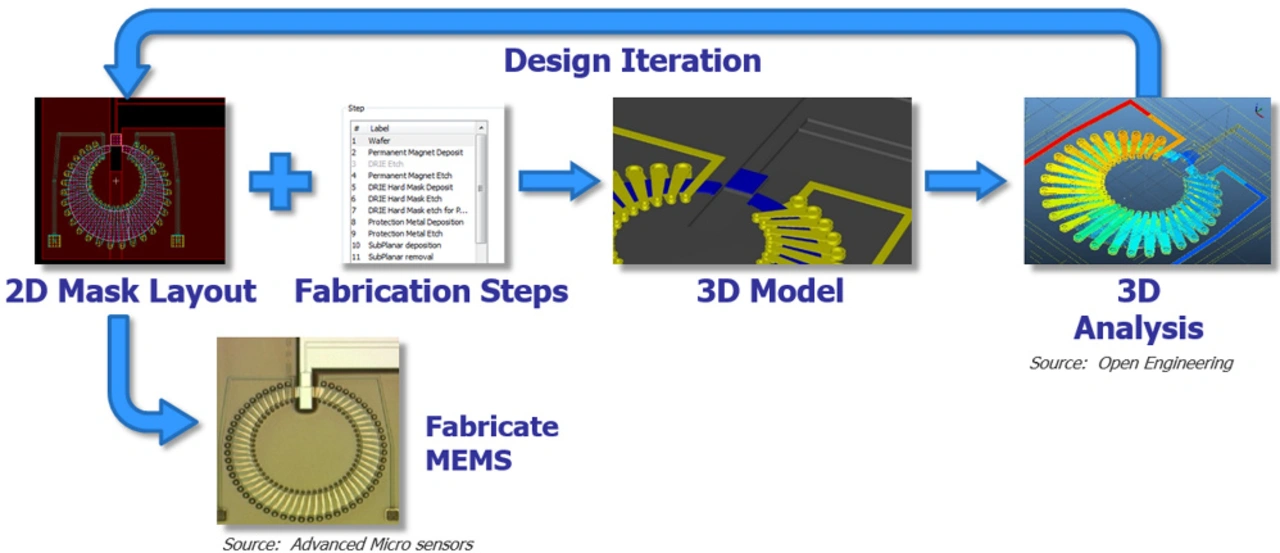

Traditionell beginnt die Entwicklung eines MEMS mit der Erstellung eines 3D-Modells des MEMS. Anschließend werden die physikalischen Eigenschaften in einem Finite-Elemente-Analyse-Tool (FEA) eines Drittanbieters analysiert, bis ein zufriedenstellendes Ergebnis erreicht ist. Zur Herstellung des MEMS benötigt das Team jedoch eine 2D-Maske. Um die 2D-Maske aus dem 3D-Modell abzuleiten, folgt das Team dem in Bild 5 dargestellten Mask-Forward-Designablauf.

Zuerst wird ein 2D-Maskenlayout erstellt. Der 3D-Solid-Modeler übernimmt dann das Layout und eine Reihe von 3D-Fertigungsprozessschritten, um automatisch ein 3D-Solid-Modell des Geräts zu generieren. Danach wird das 3D-Modell exportiert und eine 3D-Analyse mit einem bevorzugten Finite-Elemente-Werkzeug durchgeführt. Falls Probleme auftauchen, muss der Vorgang wiederholt werden. Dazu werden die entsprechenden Änderungen am 2D-Maskenlayout vorgenommen und der Ablauf wiederholt. Mit diesem Mask-Forward-Designablauf können die Designteams auf ein funktionierendes MEMS konvergieren, da direkt Masken für die Fertigung erstellt werden. Es wird nicht mehr vom 3D-Modell rückwärts gearbeitet.

Anm. der Redaktion: intelligent ist branchenübliches Synonym für selbst regulierend geworden.

- Designflow für IoT-Edge-Sensoren

- Notwendigkeit integrierter Designflüsse