Bisherige Ansätze stoßen an Grenze

Multi-Chip-Technologien für Leistungssteigerung?

Fortsetzung des Artikels von Teil 1

Mit welchen Maßnahmen lassen sich Rechenleistung weiter steigern?

Su glaubt, dass viele der bisher verwendeten Ansätze – außer die Skalierung – an ihre Grenzen stoßen, nur Innovationen auf Systemebene würden zu einer weiteren Leistungssteigerung führen. So sei beispielsweise eine weitere Vergrößerung der Die-Fläche schwierig. Su: »Mit jedem Sprung auf den nächsten Technologieknoten steigt die Komplexität, sodass die Kosten pro mm² in modernen Technologien kontinuierlich gestiegen sind. Hinzu kommt noch, dass die Fertigungsausbeute für sehr große Die-Flächen ziemlich schlecht ist und dass auch die Grenzen der Masken erreicht sind.«

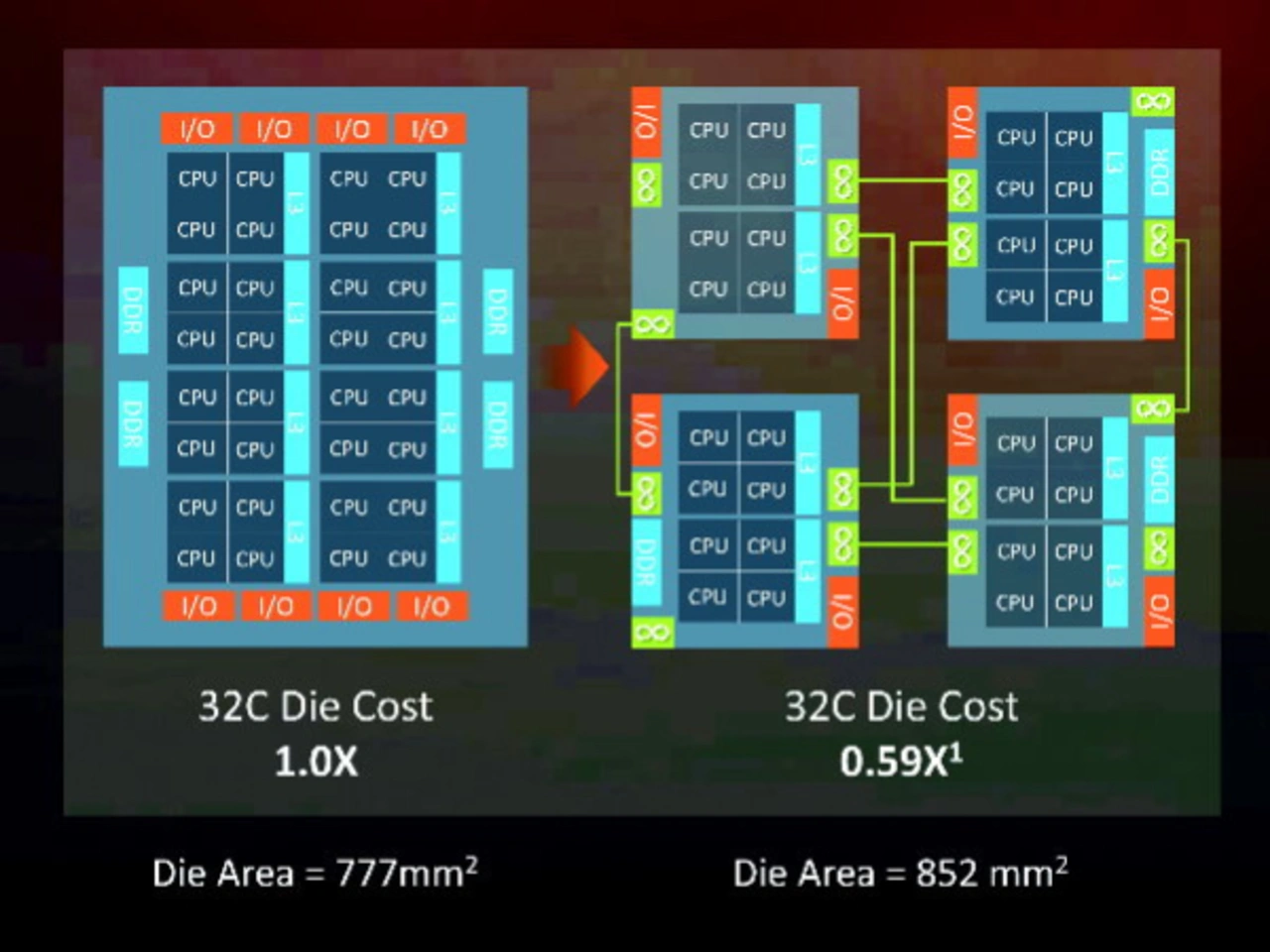

Deshalb setzt AMD nicht mehr auf eine monolithische Integration, sondern auf eine Chiplet-Architektur, die in den Epyc-Server-Produkten zum Einsatz kommt. In dem Fall hat AMD ein 32-Core-Server-Die mit Hilfe von vier diskreten Chiplets in einem Multi-Chip-Modul mit einer Gesamtfläche von 852 mm² realisiert, eine Fläche, die mit herkömmlichen Belichtungsverfahren nicht möglich wäre. Im Vergleich zu einem monolithischen Ansatz war es AMD damit möglich, nicht nur die Funktionalität zu erhöhen, sondern auch die Fertigungsausbeute. Su: »Aufgrund der kleineren Die-Flächen und der damit erhöhten Fertigungsausbeute schätzen wir, dass die Fertigungskosten um rund 40 Prozent reduziert werden konnten.« Und das trotz des 10-prozentigen Overheads, der für die Verbindung der Dies notwendig ist.

Su ist überzeugt, dass Multi-Chip-Module zukünftig in HPC-Anwendungen (HPC: High Performance Computing) einen wichtigen Beitrag leisten werden, um die Rechenleistung zu erhöhen. Mit diesem Ansatz könnten auch verschiedene Technologieknoten für verschiedene Elemente wie analoge I/Os oder Speicher genutzt werden. Ein weiteres Beispiel für Innovationen auf Systemebene stellt für Su die Nutzung von HBMs (High Bandwidth Memories) mit GPUs dar. AMD hat diese Technik zum ersten Mal bereits 2015 genutzt und seitdem sein Produktportfolio entsprechend ausgebaut, einschließlich der kürzlich vorgestellten Vega-Produkte. Speicherbandbreite ist ein kritischer Faktor, wenn es um eine Leistungssteigerung auf Systemebene geht. Su: »Werden die Distanzen zwischen Speicher und GPU von 40 mm und mehr auf 1 mm reduziert, wird auch der Energiebedarf pro Zugriff auf den Speicher gesenkt. Hinzu kommt noch, dass die größere Dichte der Micro-Bumps und der Interposer-Verbindungen eine niedrigere Frequenz und ein einfacheres elektrisches Protokoll ermöglichen als traditionelle GDDR5-Speicher. Diese Verbesserungen führen in der Summe zu einem um den Faktor 4 reduzierten Energieverbrauch beim Speicherzugriff.«

Aus Sus Sicht könnte außerdem die 3D-Stacking-Technologie in Zukunft viel Potenzial für Innovationen auf Systemebene bieten. 2D- und 2.5D-Techniken hätten viele Vorteile, aber auch ihre Grenzen. So würden 2D-MCMs zwar insgesamt die funktionale Die-Fläche verbessern, aber es wäre aufgrund der High-Speed-I/Os zum Verbinden der Chiplets zusätzliche Power notwendig. Ähnlich verhält es sich mit dem 2.5D-HBM-Ansatz. Er bietet zwar eine deutliche Verbesserung der Speicherbandbreite, bringt aber Einschränkungen im Schnittstellenbereich, in der Dichte und bei den Kosten mit sich. Su: »3D ist vielversprechend, um einige dieser Probleme zu adressieren.« Das vertikale Stapeln von Prozessor, Speicher und anderen Komponenten könne die Stromaufnahme, die auf den I/O-Interconnect entfällt, reduzieren und eine deutlich höhere Integration auf Systemebene ermöglichen. Problematisch dabei ist aus Sus Sicht, dass diese Techniken zwar schon häufig demonstriert wurden, aber bislang nur in einer Laborumgebung. Su fordert: »Diese Ansätze müssen sich aber für die Hochvolumenproduktion eignen, und hier müssen noch Probleme mit der TSV-Technik, der Wärmeentwicklung und dem kosteneffektiven hochvolumigen Assembly gelöst werden.«

Darüber hinaus seien auch Bausteintechnologien notwendig, die weniger Energie pro Operation benötigen, ohne die Performance negativ zu beeinflussen. Auch hier betont Su, dass die Innovationen in diesem Bereich auch in Zukunft ein Schwerpunktthema bleiben müssen. Su: »Wir haben uns viele Jahre lang auf Verbesserungen auf Transistorebene verlassen; es gibt keine Design- oder Systemtechniken, die diese ersetzen können.« Für vielversprechende Ansätze hält sie SiGe-Trigate- und GAA-Transistoren (Gate all around). Außerdem seien Verbesserungen im analogen I/O-Bereich notwendig, denn auf die Kommunikation nach außen entfiele ein Großteil des Leistungs-Budgets. Nur dann können Leistungsaufnahme reduziert und höhere Geschwindigkeiten ermöglicht werden.

Und schließlich stellen auch die Speichertechnologien ein zunehmendes Problem für die Leistungsaufnahme und die Rechenleistung dar. Hier können 2.5D- und 3D-Integration-Ansätze zwar helfen, aber sie stellten nur einen Schritt in die richtige Richtung dar. Su abschließend: »Die zugrunde liegende Technologie muss verbessert werden und zwar in Hinblick auf Dichte, Kosten pro Bit und Energie pro Bit. Eine Reihe nichtflüchtiger Technologien wie PCM, MRAM und ReRAM zeigt durchaus Potenzial, sie müssen aber noch ausgereift werden.«

Jobangebote+ passend zum Thema

- Multi-Chip-Technologien für Leistungssteigerung?

- Mit welchen Maßnahmen lassen sich Rechenleistung weiter steigern?