IEDM 2019

»Die Zukunft von Moore’s Law ist besser als jemals zuvor«

Fortsetzung des Artikels von Teil 2

Jenseits von CMOS

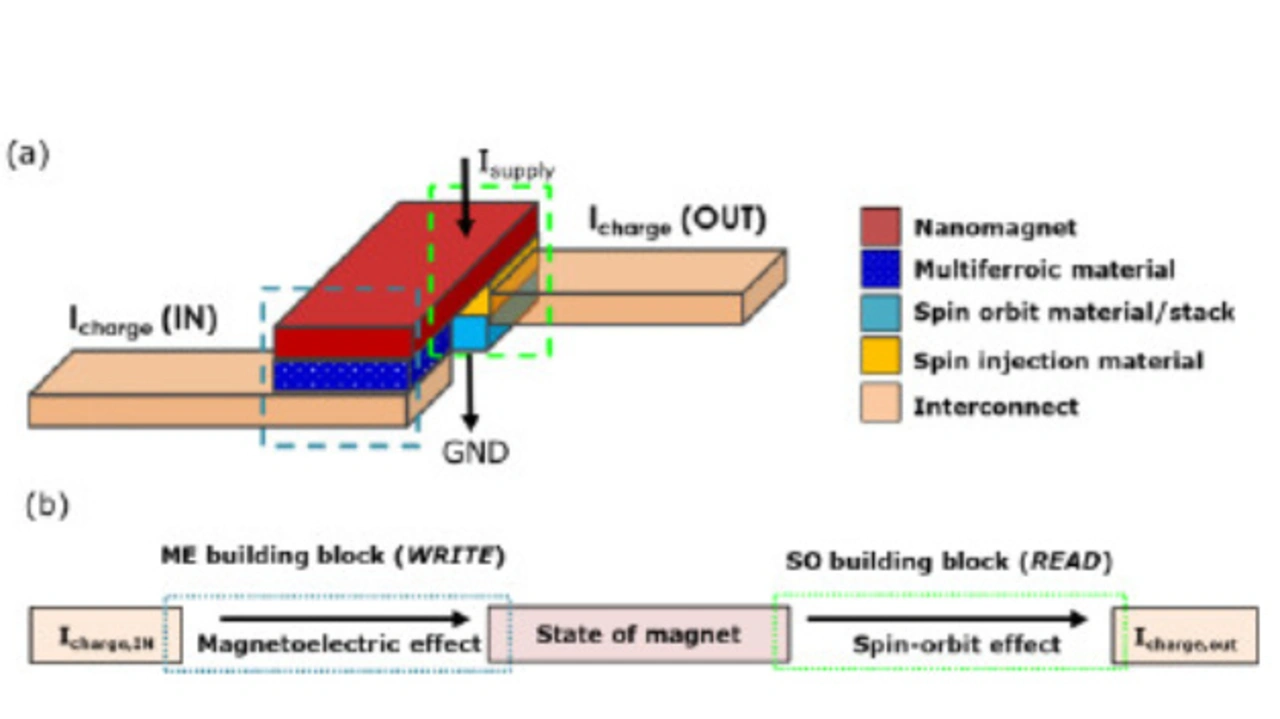

Die Skalierung der CMOS-Elektronik nach Moore's Law steht nicht nur vor Herausforderungen bei der Strukturierung kleinerer Bauteile, sondern auch bei der Verlustleistung auf dem Chip. Ein wichtiger zukunftsweisender Forschungsvektor für Transistoren ist die Identifizierung eines energieeffizienten Schalters jenseits von CMOS für zukünftige energieeffiziente Logik und integrierte Schaltungen. Die Methodik des Benchmarkings von Transistorstrukturen jenseits von CMOS führte zu dem Ergebnis, dass sich magnetoelektrische Spin-Orbit Logikschaltungen (MESO) als der vielversprechendste Kandidat mit den besten Energie/Laufzeit-Eigenschaften (energy-delay) unter allen untersuchten über CMOS hinaus gehenden Kandidaten herausstellten. MESO ist ebenfalls ein eigenes Paper gewidmet.

Jobangebote+ passend zum Thema

Dichte Speicher-Logik-Integration

Die enge Speicher-Logik-Integration für zukünftige Compute-Nearmemory- und KI-Anwendungen ist ein wichtiger Faktor bei der Fortführung des Moore's Law und darüber hinaus, der durch heterogene 3D-System Integration mit Hybrid-Bonding und ODI realisiert werden kann. Mit der Weiterentwicklung der Schichtübertragungstechnologie und der Speichermaterial-Abscheidung lassen sich mehrschichtige/stapelbare Speicherelemente auf Si-CMOS über eine heterogene 3D-Integration umsetzen. Ein Low-Voltage-Single-Transistor-Speicherelement, das aus stapelbaren Materialien per Niedertemperaturverarbeitung hergestellt wird, hat das Zeug zu einem attraktiven Kandidaten für ein solches System. Darüber hinaus kann das Aufkommen von Spin Orbit Torque MRAM (SOT), das eine potenziell höhere Dichte mit einer Geschwindigkeit in der Nähe von 6T-SRAM kombiniert, für zukünftige Last-Level-Cache-Anwendungen mit monolithischem Integrationsschema verwendet werden.

- »Die Zukunft von Moore’s Law ist besser als jemals zuvor«

- Verbindungsstrukturen, Direkte Selbstanordnung und heterogene 3D-Systemintegration

- Jenseits von CMOS