Intel Manufacturing Day 2017

Dem Ende von Moore's Law von der Schippe gesprungen

Fortsetzung des Artikels von Teil 2

Auf dem 14-nm-Pfad zu „Ice Lake“

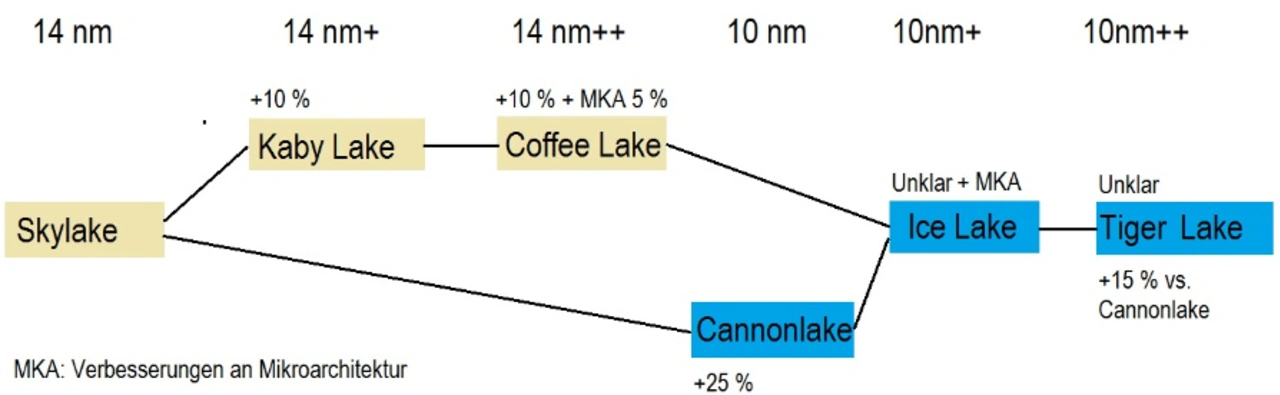

Da man es sich nicht nochmal erlauben kann, ewig auf einem Design festzusitzen (diesmal „Skylake“), hat sich Intel parallel zu dem Ramp-Up von 10 nm über „Cannonlake“ dazu entschieden, parallel einen 14-nm-Weg zu beschreiten, der von zwei Optimierungen des ursprünglichen 14-nm-Prozesses gekennzeichnet ist. Als erstes wurde „Kaby Lake“ vorgestellt, das eine identische Mikroarchitektur wie „Skylake“ aufweist und in einem 14-nm-Plus-Prozess gefertigt wird. Dieser bringt, wie heute verkündet wurde, einen um 12 % höheren Treiberstrom für PMOS und NMOS, was reale Geschwindigkeitszuwächse von rund 10 % gegenüber Skylake erklärt. Damit allerdings nicht genug: Eine weitere Prozessoptimierung führt zu 14-nm-Plus-Plus, das nochmals 11 bzw. 12 % (NMOS/PMOS) höhere Treiberströme als 14-nm-Plus bringt. Das Design, das darin gefertigt wird, heißt „Coffee Lake“ und wird zeitgleich mit „Cannonlake“ Ende 2017 vorgestellt. Laut Intel soll die Rechenleistung gegenüber „Kaby Lake“ um 15 % steigen, was nur durch zusätzliche Verbesserungen an der Mikroarchitektur zu erreichen ist.

Klar wurde jetzt auch, daß der 14-nm-Plus-Plus-Prozess absolut gesehen höhere Taktfrequenzen – bei allerdings höherer Leistungsaufnahme – als der 10-nm-Prozess (ohne Plus oder Plus-Plus) ermöglicht. Dies macht ja auch Sinn, wenn man die Zielanwendungen betrachtet.

„Ice Lake“ führt 10-nm und 14-nm zusammen

Wenn dann einmal die Ausbeute-Probleme der neuen 10-nm-Fertigung behoben sein werden (hoffentlich), können wir im 2. Halbjahr 2018 mit „Ice Lake“ rechnen, einem Design, das „Cannonlake“ und „Coffee Lake“ wieder auf eine Linie zusammenführt. Da die Mikroarchitektur-Veränderungen mangels Transistor-Budget bei „Coffee Lake“ wohl eher gering ausfallen werden, ist bei „Ice Lake“ dank weiter sinkender Transistorkosten ein größerer Schritt zu erwarten, um z.B. die IPC zu erhöhen.

Jobangebote+ passend zum Thema

Neuer Foundry-Prozess greift Globalfoundries an

Neben dem IDM für CPUs hat Intel ja auch ein nicht unerhebliches Foundry-Geschäft ausgebaut, u.a. weil man ein substantielles Eco-System aufgebaut hat. Hier hat Intel offenbar aus seinen Fehlern gelernt, nämlich zu glauben, man könne alles aus einer Hand anbieten. Seit 10 Monaten ist jetzt auch ARM an Bord, andere Player sind u.a. Cadence, Synopsys, Mentor Graphics oder Imagination.

Der neue Prozess heißt 22FFL und basiert auf Intels bewährten 22- und 14-nm-FinFET-Prozessen. Er adressiert den Massenmarkt und soll kostenmäßig mit planaren Prozessen wie Globalfoundries‘ 22nmFDX mithalten können – bislang galten FinFET-Prozesse als zu teuer für kostensensitive Anwendungen.

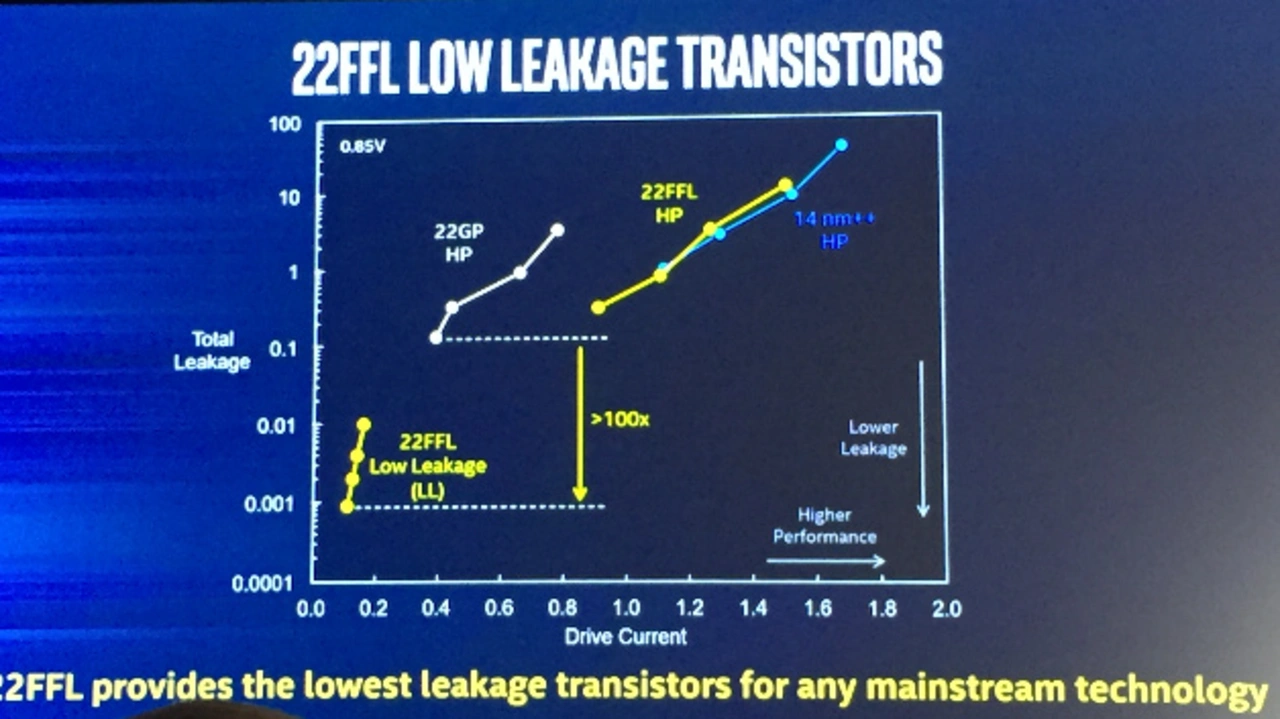

Neben High-Performance-Transistoren, deren elektrische Eigenschaften erstaunlicherweise nahe an dem 14-nm-Plus-Plus-Prozess liegen, hat Intel Ultra-Low-Leackage-Transistoren für Always-On-Schaltkreise entwickelt, deren Leckströme (und zwar alle 3 Arten zusammengerechnet, also Subthreshold-Leckstrom, Gate-Leckstrom und Band-To-Band-Tunneling (BTBT)-Lec kstrom) hundertmal kleiner sind als beim 22-nm-Prozess (Bild). Der Prozess ist auch für Analog-Designs geeignet, da entsprechende Komponenten wie Kapazitäten, Widerstände, Induktivitäten, Hochspannungs-I/O-Transistoren, Leistungstransistoren u.a. zur Verfügung stehen.

In einer Panel-Diskussion wurde nicht nur der neue Prozess u.a. von ARM-Manager Will Abbey, sondern auch Cadence-CEO Lip-Bu Tan und Synopsys‘ CEO Aart de Geus gelobt. Natürlich stellt sich die Frage, welcher ARM-Lizenznehmer, der im Wettbewerb mit Intel steht, Interesse an einer Fertigung in der Intel-Foundry hat – Qualcomm sei hier nur als ein Beispiel genannt.

Fazit

Intel hat aus der an sich üblen Situation, nämlich dem Verzug der Einführung des 10-nm-Prozesses vermutlich durch schlechte Chipausbeuten, das Beste gemacht. Wenn er denn kommt, ist er wieder einmal Top und lässt Samsung, TSMC & Co. alt aussehen. Wann und ob überhaupt ohne EUV die Konkurrenz derartige Transistordichten wird liefern können, ist unklar – es dürfte weitere Jahre dauern, bis Samsung und TSMC diese Flächen erreichen. Bis dahin „beglückt“ Intel seine Kunden mit weiteren optimierten 14-nm-Designs, welche viel Geld kosten dürften, jedoch verhindern, daß die Kunden festsitzen, wie es seinerzeit bei Haswell der Fall war.

Im Foundry-Geschäft gibt es neben den herkömmlichen FinFET-Prozessen (Ende 2017 soll es das erste 10-nm-Tapeout geben) jetzt einen hochinteressanten Low-Cost-FinFET-Prozess, der auf FD-SOI und andere Planar-Prozesse zielt. Nach dem Aufbau eines Ökosystems a la ARM ist Intel eine ernstzunehmende Alternative geworden, die aus politischen Gründen für direkte Konkurrenten jedoch kaum attraktiv erscheinen dürfte. Der restliche Foundry-Markt ist im High-End-Bereich schon 23 Mrd. Dollar groß, insofern dürfte es genug Möglichkeiten für Intel geben.

- Dem Ende von Moore's Law von der Schippe gesprungen

- Quad-Patterning und Innovationen bringen Intel zurück in die Moore's-Law- Spur

- Auf dem 14-nm-Pfad zu „Ice Lake“