Intel Manufacturing Day 2017

Dem Ende von Moore's Law von der Schippe gesprungen

Fortsetzung des Artikels von Teil 1

Quad-Patterning und Innovationen bringen Intel zurück in die Moore's-Law- Spur

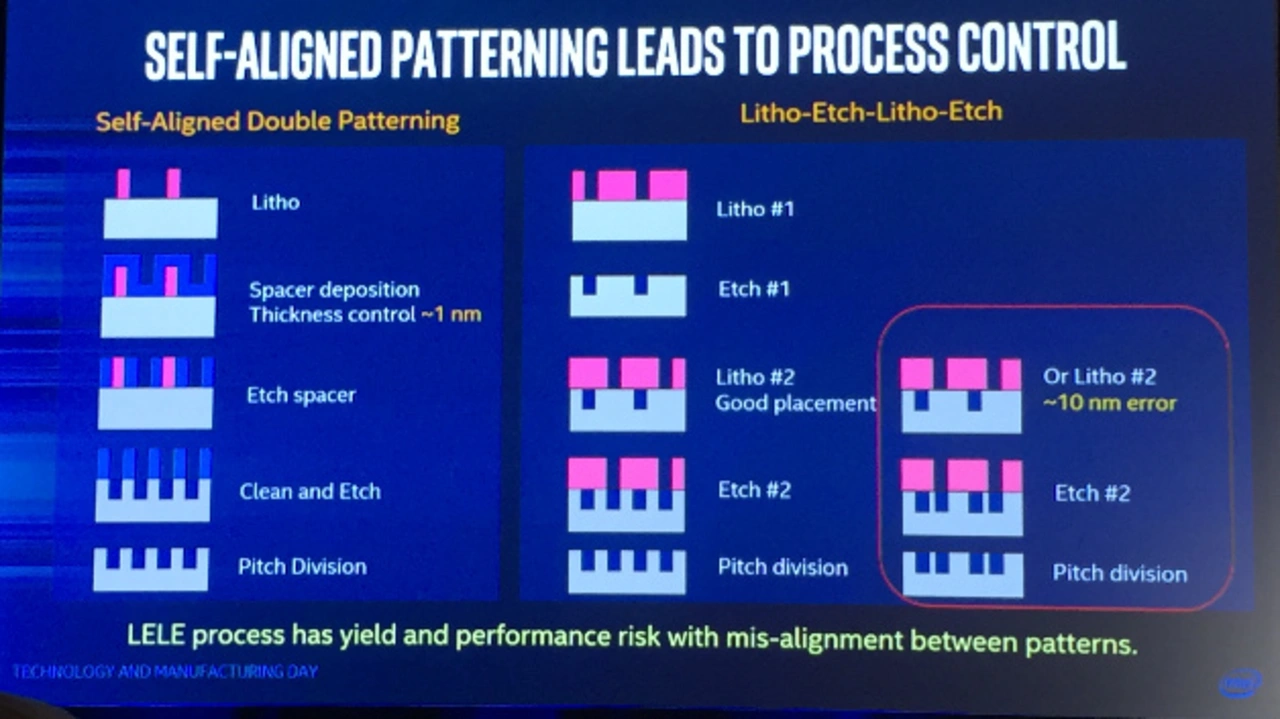

Die Frage, wie man diese feinen Geometrien überhaupt bei einer hinreichenden Chip-Ausbeute erstellen kann, beantwortete Intel auch gleich mit: Das weltweit erste Self-Aligned-Quad-Patterning kommt zum Einsatz. Im Gegensatz zu dem von Samsung eingesetzten LELELE-Verfahren (Belichten-Ätzen-Belichten-Ätzen-Belichten-Ätzen) bietet dies den Vorteil, daß es Strukturen bis herunter zu einem Metal-Pitch von 20 nm erlaubt, während LELELE bereits bei über 40 nm an seine Grenzen stößt. Noch wichtiger ist aber die Frage des Risikos für Chipausbeute und Fehlstellungen von Strukturen auf dem Chip.

Der grundsätzliche Unterschied beider Verfahren besteht darin, daß bei LELELE mehrere Masken zum Einsatz kommen, die mit höchster Genauigkeit für jeden Durchlauf des Lithographie-Scanners positioniert werden müssen. Die Toleranzen bewegen sich im Bereich von nur 2-3 nm. Wird eine Maske fehlpositioniert (Bild), wird die Struktur falsch hergestellt. Beim Self-Aligned-Patterning wird nur 1 Maske eingesetzt und dann chemische Verfahren genutzt, um das Material um das von der Maske definierte Element quasi herumzuwickeln.

Jobangebote+ passend zum Thema

Innovationen bringen Moore‘s Law in die Spur

Eine Skalierung um Faktor 2 wäre ohne sogenanntes „Hyperscaling“ nicht möglich gewesen. Diese erstmals 2015 in einem White-Paper von Intel beschriebene Technologie bedeutet, daß man zusätzlich zur „normalen“ Skalierung durch weitere Techniken noch mehr Dichte herausholt.

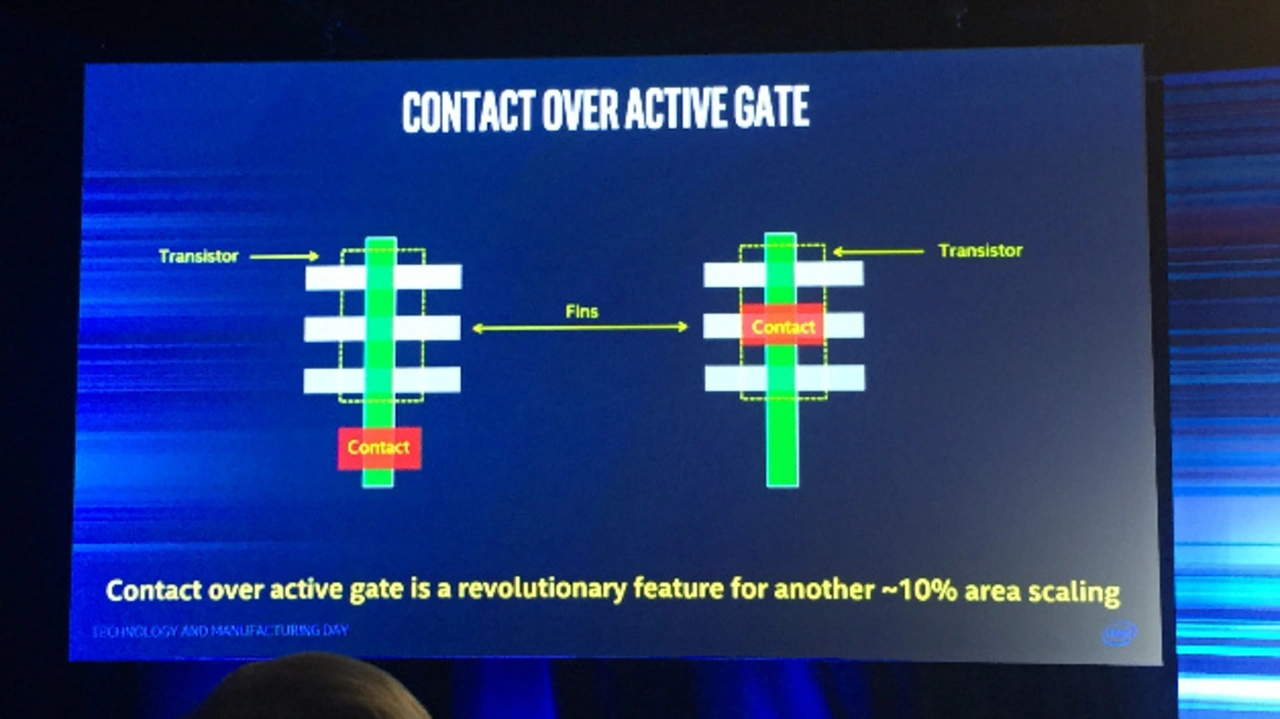

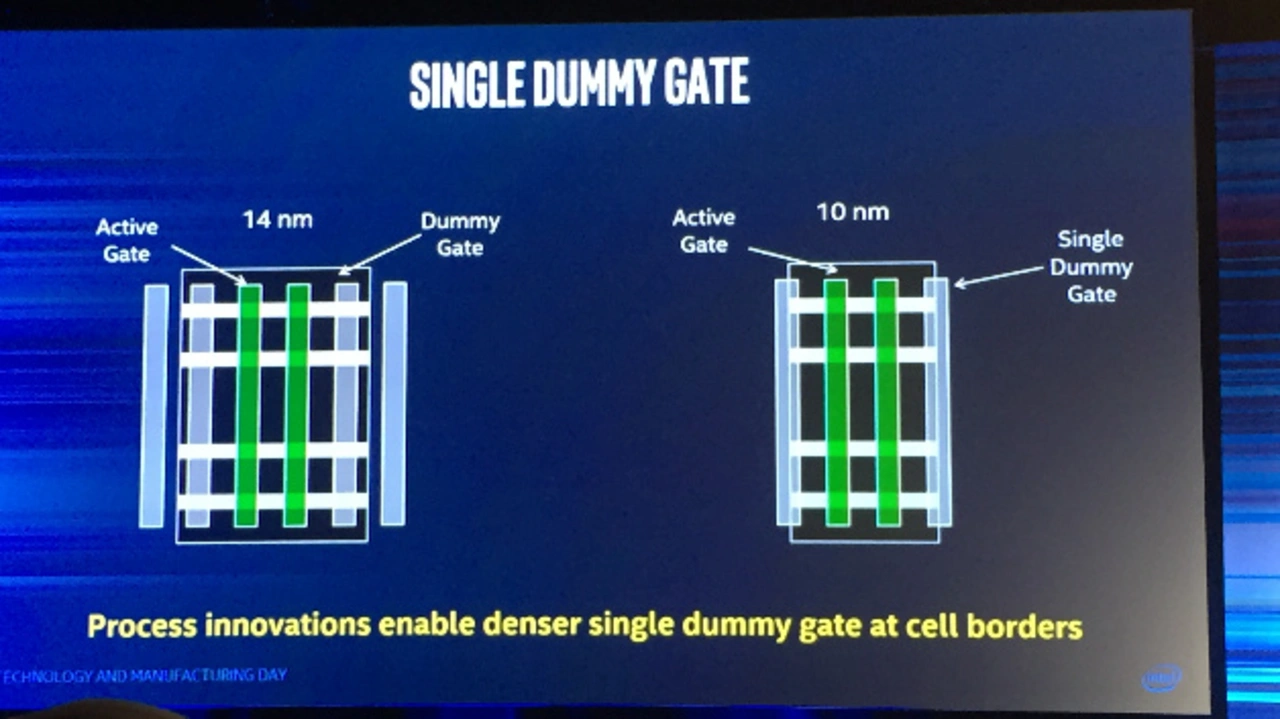

Als erstes ist das sogenannte „Contact over Gate“ zu nennen, das eine Flächenreduktion von 10 % bringt, indem der Kontakt außerhalb des Transistors eingespart wird (Bild oben). Als zweite Innovation konnten die bislang zwei Dummy-Gates durch ein Dummy-Gate an den Transistorgrenzen ersetzt werden (Bild unten). Dummy-Gates müssen beim Gate-Last-Ansatz von Transistoren mit High-K-Metal-Gates eingebracht werden. Beim Gate-Last-Prozess wird die metallische Gate-Elektrode erst nach der Implantation und Aktivierung der Source- und Drain-Gebiete hergestellt. Hierzu wird zunächst ein konventionelles Polysilicium-Gate hergestellt und die Implantation/Aktivierung der Source- und Drain-Gebiete durchgeführt. Nun wird das Polysilicium der Gate-Elektrode selektiv entfernt, quasi eine Opferschicht (im englischen eben Dummy-Gate genannt). Anschließend wird das nun „leere“ Gate mit dem gewünschten Schichtstapel (High-k-Dielektrika, Anpassungsmetalle und Gate-Elektrode) gefüllt.

- Dem Ende von Moore's Law von der Schippe gesprungen

- Quad-Patterning und Innovationen bringen Intel zurück in die Moore's-Law- Spur

- Auf dem 14-nm-Pfad zu „Ice Lake“