Neuer Xilinx-CEO Victor Penn in München

Vision und Strategie für eine adaptierbare Welt

Fortsetzung des Artikels von Teil 1

Neue Generation programmierbarer Logik »ACAP« kostet mehr als 1 Mrd. Dollar

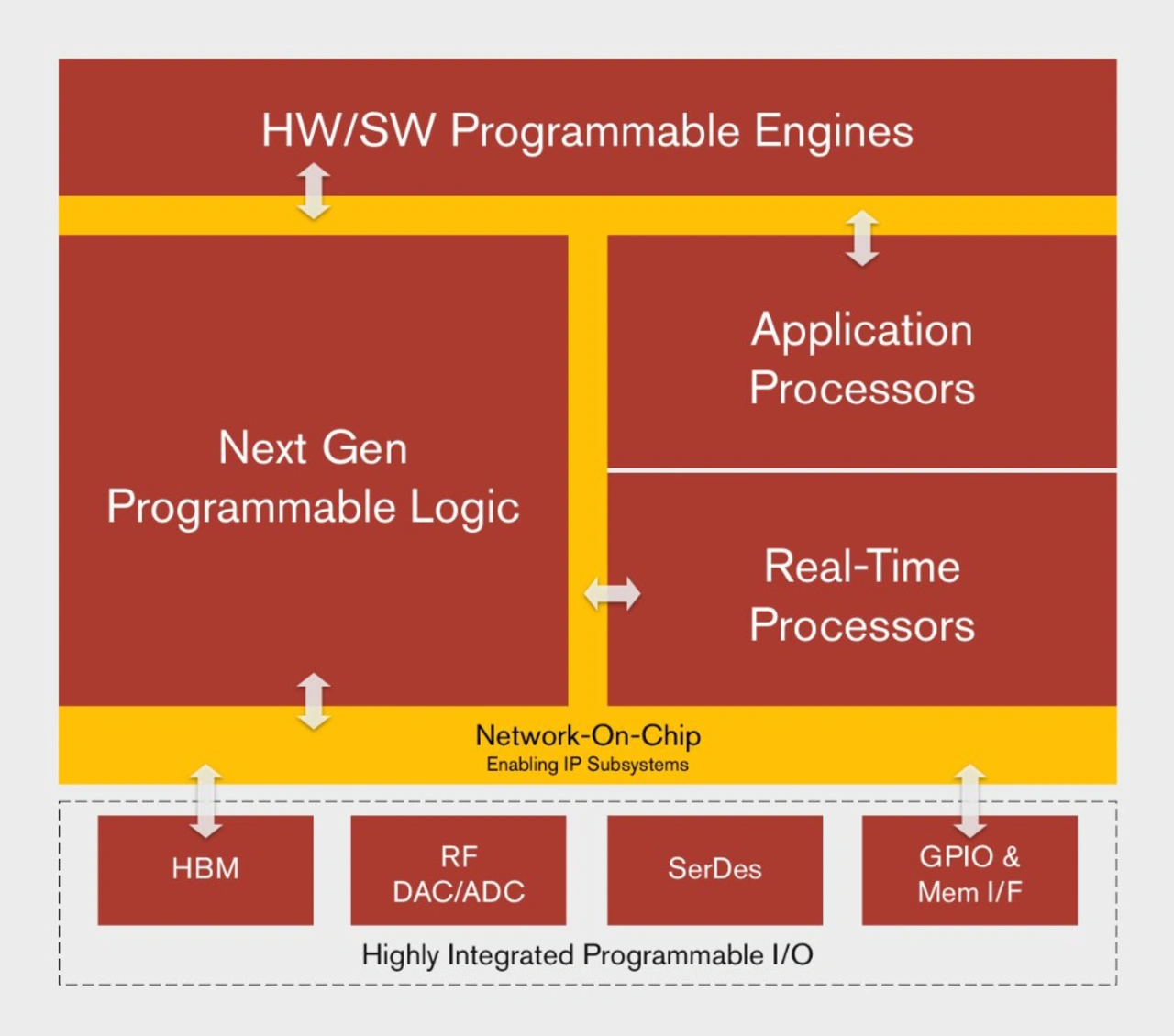

Mit einer neuen Generation von programmierbarer Logik möchte Peng die Grundlagen für das adaptierbare Computing legen. »ACAP« (Adaptable Compute Acceleration Platform) heißt die völlig neue Generation von programmierbaren Logik-Chips, die Hard- und Software programmierbare Engines, IP-Subsysteme und ein Netzwerk auf einem Chip umfasst und diese mit programmierbaren I/O-Blöcken kombiniert. Unter dem Codenamen »Everest«, der für die erste 7-nm-ACAP-Familie steht, arbeiteten 1500 Ingenieure vier Jahre an Chips mit bis zu 50 Mrd. Transistorstrukturen. Das Entwicklungsbudget überschreitet dabei eine Milliarde Dollar. Von der neuen Architektur verspricht sich Xilinx eine bessere Adaptierbarkeit mit dynamischer Optimierung für Rechenlasten, eine 20-fache Steigerung der KI-Rechenleistung sowie eine Vervierfachung der Kommunikationsbandbreiten in 5G-Mobilfunk-Systemen. Das Tape-out des ersten ACAP-Chips soll im laufenden Jahr stattfinden und die Bemusterung dann 2019.

Jobangebote+ passend zum Thema

- Vision und Strategie für eine adaptierbare Welt

- Neue Generation programmierbarer Logik »ACAP« kostet mehr als 1 Mrd. Dollar