On-Chip-Peripherie

Mehr Flexibilität durch programmierbare Logik

Fortsetzung des Artikels von Teil 1

Hardwarebeschleunigte Paritätsberechnung

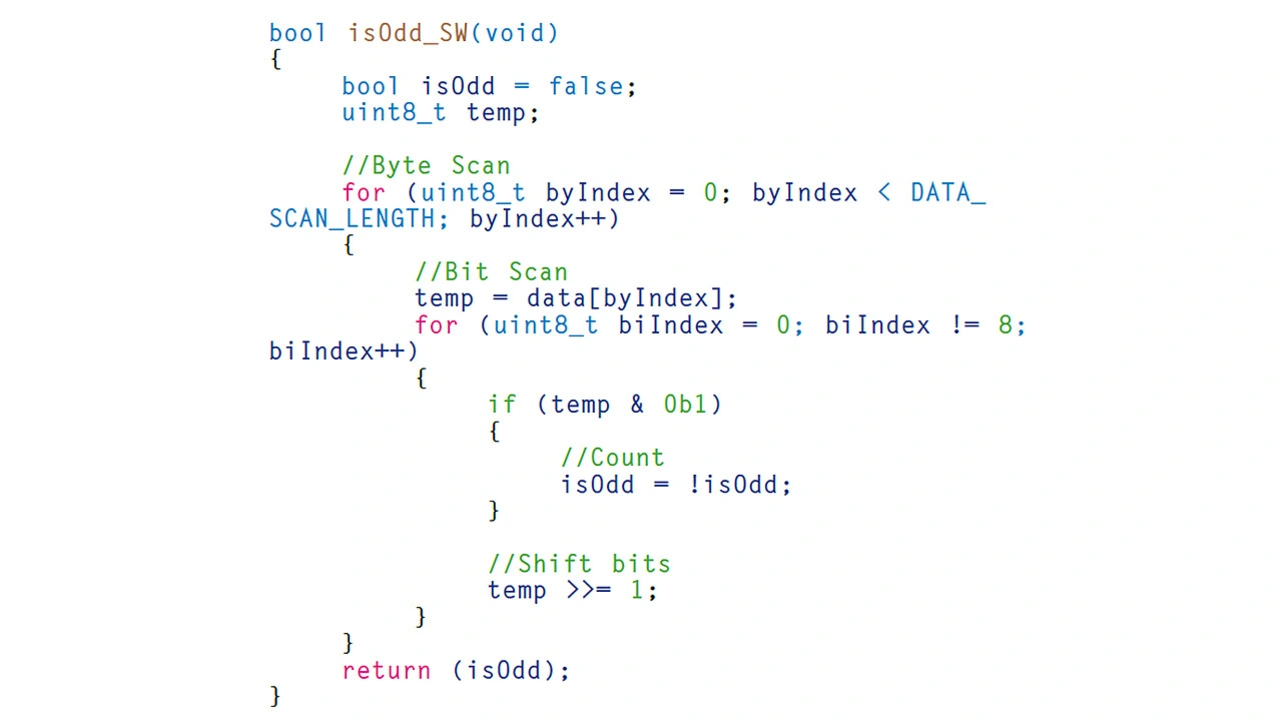

Manchmal ist es notwendig, ein Paritätsbit für die Datenübertragung oder Kommunikation zu generieren. Die Berechnung der Parität in Software ist trivial, aber langsamer als in Hardware. Nachfolgend wird eine einfache Funktion gezeigt (Listing 3).

Hinweis: Für diese einfachen Beispiele wird das ausgewertete Testmuster global gespeichert.

Jobangebote+ passend zum Thema

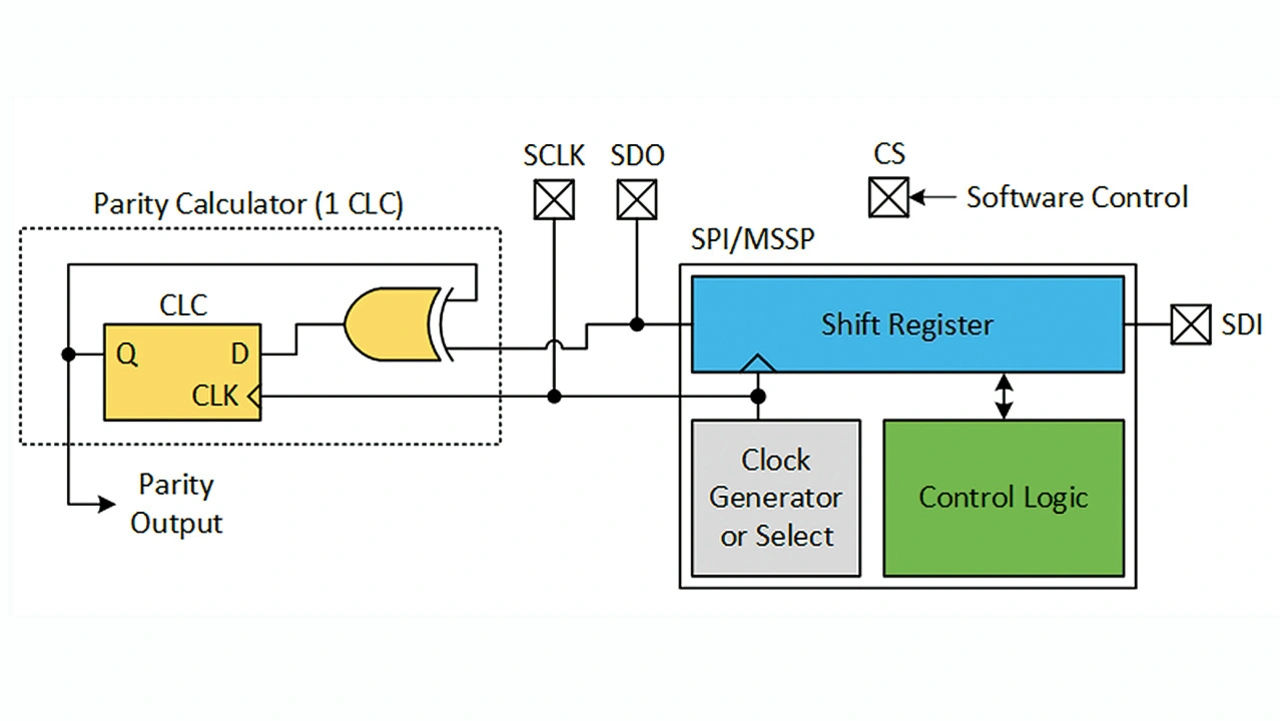

Zur Beschleunigung der Berechnungen kann eine SPI-Peripherie mit einem CLC verwendet werden, um einen Hardware-Paritätsrechner aufzubauen. Die SPI-Hardware (Bild 5) enthält ein serielles Schieberegister zum Senden und Empfangen von Daten. Das Ausgangssignal der SPI-Hardware (das Schieberegister) kann in einen CLC eingespeist werden, um einen Paritätsrechner aufzubauen, der wesentlich schneller arbeitet als die Softwareversion.

Diese Implementierung kann auch ein vorhandenes SPI-Peripheriegerät wiederverwenden, was die Implementierungskosten weiter senkt. Das liegt daran, dass die Chip-Select-Leitung (CS) normalerweise aktiviert sein muss, um mit anderen SPI-Bausteinen kommunizieren zu können. Ist diese nicht aktiviert, wird die Kommunikation ignoriert.

Zur Ausführung der hardwarebeschleunigten Version muss man zunächst den aktuellen gelatchten Wert im CLC erfassen. Anschließend werden die Daten zur Paritätsberechnung übertragen, wobei CS nicht aktiviert ist. Als nächstes wird der neue im CLC gespeicherte Wert betrachtet. Stimmt der neue Wert mit dem vorherigen überein, so wurde eine gerade Anzahl von Einsen gezählt. Wenn die Werte nicht gleich sind, wurde eine ungerade Anzahl von Einsen gezählt. Nachfolgend ist die Software zur Berechnung einer ungeraden Parität dargestellt.

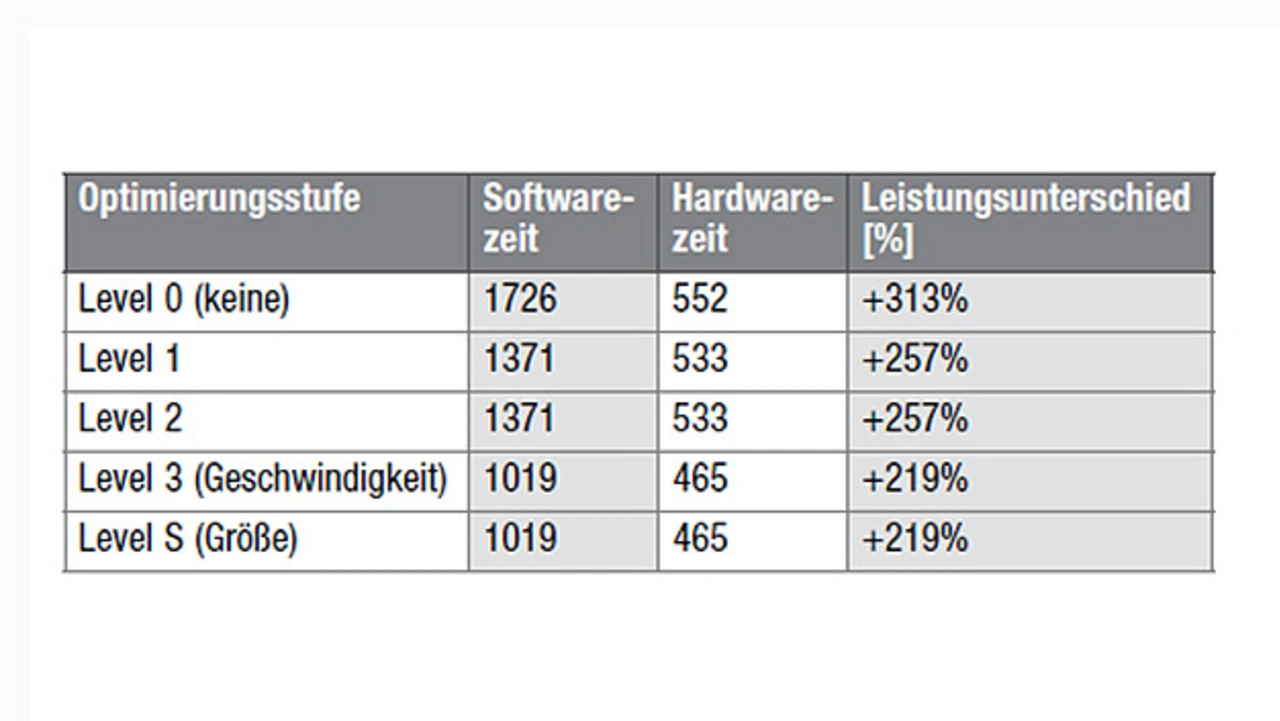

Um den Geschwindigkeitsvorteil zu demonstrieren, wurde ein kleines Demoprogramm auf der Microcontrollerfamilie PIC16F18146 von Microchip erstellt. Einer der internen Timer, Timer 1, wird zum Zählen der Taktzyklen (FOSC/4) verwendet, die zur Durchführung der Hardware- und Software-Paritätsberechnungen erforderlich sind. Das Ergebnis wird zur Analyse an ein serielles Terminal ausgegeben. Die Leistungswerte für verschiedene Compiler-Optimierungsstufen sind in der Tabelle aufgeführt.

Deutliche Steigerung der Leistung

Die hier gezeigte Leistungssteigerung ist abhängig von der Taktfrequenz des Mikrocontrollers und der SPI-Peripherie. Der Quellcode dieses Programms ist auf Github verfügbar.

Hardware-Peripheriegeräte sind ein wichtiger Bestandteil von Embedded-Systemen. Ihr Einsatz kann Mikrocontroller performanter, effizienter und leistungsfähiger machen. Logikelemente und flexible Peripheriemodule sind besonders leistungsfähige Werkzeuge, um einfache Aufgaben wie Entprellung oder Quadraturdecodierung durchzuführen. Der kreative Einsatz von Hardware-Peripheriegeräten verbessert Designs und erweitert die Grenzen dessen, was mit einem Mikrocontroller möglich ist.

Der Autor

Robert Perkel

erwarb 2019 einen Bachelor-Abschluss in Computer Engineering am Virginia Polytechnic Institute and State University. Er ist Application Engineer bei Microchip in Chandler, Arizona, und beschäftigt sich mit Hardware-/Softwareentwicklung u. a. mit Altium-Tools für Mikrocontroller

- Mehr Flexibilität durch programmierbare Logik

- Hardwarebeschleunigte Paritätsberechnung