Xilinx Versal ACAP

Genaue Synchronisierung in nur einem Chip

Fortsetzung des Artikels von Teil 2

Transceiver-FIFOs beeinflussen die Genauigkeit

Beide dieser Einflüsse müssen getrennt evaluiert werden, denn sie beeinflussen die Genauigkeit in unterschiedlicher Weise.

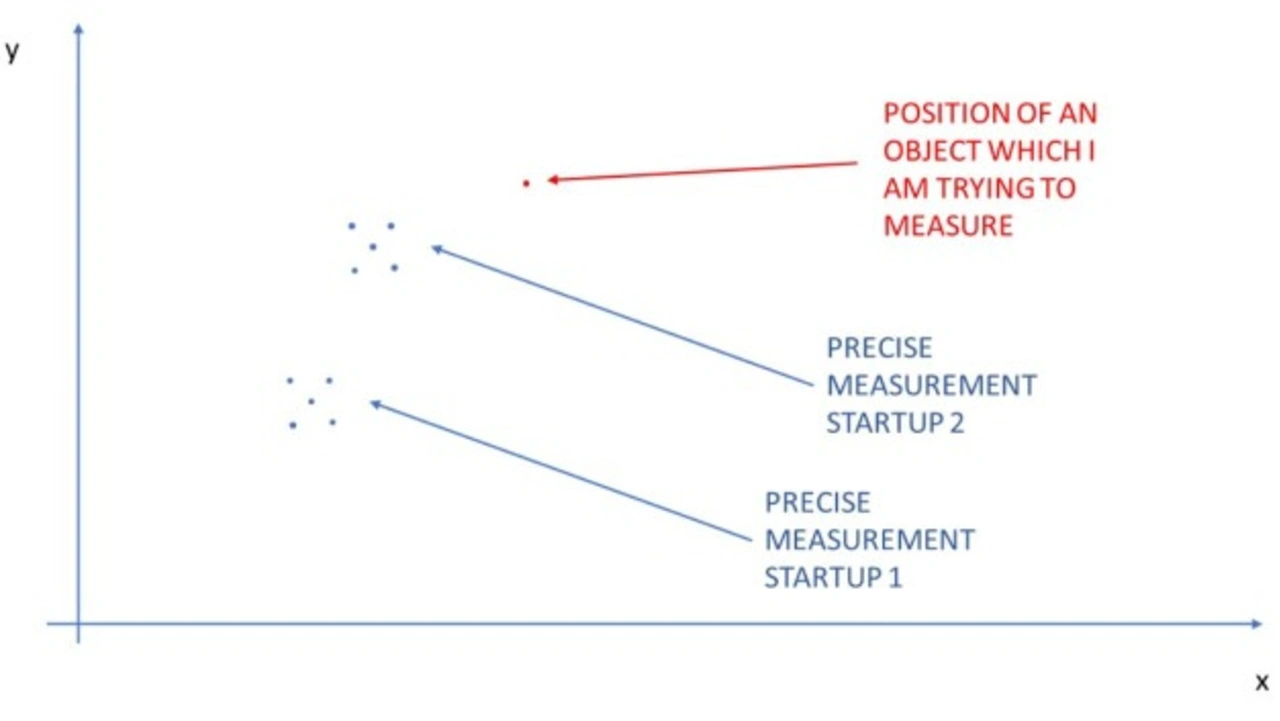

Der erst genannte beeinflusst die Genauigkeit direkt: Wenn ein Receiver und ein Transmitter beim Einschalten unterschiedliche Latenzen haben, kann der durch IEEE1588 gegebene Mechanismus dies nicht aufdecken. Jedwedes Ungleichgewicht beeinflusst unmittelbar die Genauigkeit. Auch eine Mittelwertbildung hilft da nicht weiter. Dieser Fall ist in Bild 3 graphisch dargestellt, wobei erkennbar ist, dass beide Messungen verzerrt sind.

Der zweite Effekt hat überraschenderweise keinen Einfluss auf die Genauigkeit. Tatsächlich wirken sich die Variationen der Latenz infolge von Umweltbedingungen (Spannung und Temperatur) sowohl auf den Receiver wie auf den Transmitter aus, und der IEEE1588 Mechanismus gleicht dies aus. Bevor wir weitergehen, sollten wir noch einige Details in diesem letzten Statement näher erläutern.

Impliziert es, dass der Zeitversatz nur einmal nach dem Einschalten erfolgt? Die Antwort ist: nein.

Wenn wir nur einmal kalibrieren, würde die Änderung der Latenz, obwohl symmetrisch zwischen, RX und TX, einen Fehler im Slave Takt erzeugen, der sich mit der Drift der Temperatur und der Spannungsversorgung immer weiter vergrößern würde. Die Gegenmaßnahme wäre eine Resynchronisierung, mit einem Tempo, das größer ist als die Änderungen in der Temperatur und Spannungsversorgung.

Kurzer Rückblick auf das bis jetzt Gesagte: Beitrag (Effekt) 1 erfordert die Kenntnis der Latenz beim Einschalten, und zwar unabhängig für RX und TX. Beitrag (Effekt) 2 erfordert eine hinreichend schnelle Resynchronisierung des Slaves über der Zeit.

Die Versal-Transceiver bieten mehrere alternative Möglichkeiten zur Messung und Kontrolle der Latenz, sowohl beim Einschalten als auch im Betrieb. Sie fallen unter die folgenden beiden Kategorien:

- Buffer Bypass (Umgehung des Puffers)

- FIFO-Latenzmessung

Jobangebote+ passend zum Thema

Buffer Bypassing erlaubt das Umgehen des FIFO in RX- und TX-Richtung, wobei ein komplexes Taktschema eingerichtet wird, um den Datentransfer zwischen den Domains ohne Timing-Fehler zu gewährleisten. Natürlich impliziert auch der Buffer Bypass eine minimale Latenz. Während dieser »Nebeneffekt« kaum relevant für Synchronisierungs-Applikationen sein mag, ist er eine Schlüsselgröße in anderen Industriesegmenten wie HFT (High Frequency Trading).

Währen der Buffer Bypass das Problem dadurch beseitigt, dass er die Transceiver-Latenz auf einen festen Wert setzt, fokussiert eine Reihe weiterer sehr interessanter Verfahren auf die Messung der Latenz selbst. Wenn die Latenz zu jedem Zeitpunkt bekannt ist, kann man sie leicht dazu benutzen, den Wert der Tageszeit (TOD, Time Of the Day) mathematisch zu korrigieren.

Diese Methode ist sehr interessant für Synchronisierungs-Applikationen, da sie einen natürlichen Upgrade-Pfad für alle IPs (insbesondere Ethernet) eröffnet, ohne relevante Änderungen in der Takt-Architektur des IP selbst.

Präzision wird mit beiden Methodensets erzielt, denn sie basiert auf fest kodiertem analogen Phasendetektor, eingebaut im Transceiver, und analogen Phasen-Interpolatoren, deren Taktphasen vom Nutzer aufwärts oder abwärts mit passenden Schritten im Pikosekundenbereich gesteuert werden können.

Wie steht es mit der Genauigkeit? Die typische Quelle der Ungenauigkeit ist die unterschiedliche Latenz beim wiederholten Einschalten, wegen der zufälligen Phasenbedingungen, die Teiler nach einem Reset aufweisen können.

Versal bietet nun die Möglichkeit, die Latenz entweder zu messen oder sie beim Einschalten einzustellen. Dieser anfängliche Kalibrierungsschritt stellt sicher, dass alle Quellen der Ungenauigkeit im Transceiver beseitigt werden.

Die Variation der Latenz, symmetrisch für RX und TX, die im Betrieb auftritt, lässt sich wie bereits gesagt durch den PTP-Mechanismus kompensieren. Es erscheint uns wichtig, auf dieses letzte Statement etwas näher einzugehen: Wenn PTP diese Art von Latenzänderungen kompensieren kann, worin besteht dann der Vorteil der Messung der Latenz über der Zeit?

Es gibt eine Reihe von Fällen, in denen die Änderung der Latenz nicht symmetrisch zwischen RX und TX aufgeteilt ist. Der Entwickler sollte also Protokolle beachten, die von Natur aus asymmetrisch sind, wie etwa PON.

In anderen Fällen können die RX- und TX-Pfade auf unterschiedlichen physischen Bausteinen residieren: Ein typischer Fall ist Test-Equipment. Diese unterschiedlichen Schaltungen arbeiten vielleicht in ihren spezifischen Umgebungen in Bezug auf Temperatur, Prozess und Versorgung. Alle diese Gründe dürften in ihrer Gesamtheit einen unterschiedlichen zeitlichen Verlauf der Latenz zwischen RX und TX bewirken, und damit zu einem Anstieg der Ungenauigkeit führen.

Versal-ACAP ist ein Game Changer bei der Kontrolle der Latenz und in der Latenzmessung: vom Nanosekundenbereich typischer schaltungsgebundener Taktgeber bis zum Pikosekundenbereich, wie sie analoge Phasen-Interpolatoren bieten, die in Versal fest kodiert sind.

In nur einem Siliziumbaustein

Unter »Synchronisierungs-Applikation« ist jede Applikation zu verstehen, die die Fähigkeit einsetzt, die Tageszeit (TOD) zwischen Netzwerkknoten zu transferieren. Nebenbei gesagt ist dieser Vorgang extrem anwenderspezifisch. Normalerweise erfordert dies Prozessoren mit proprietärer Software, eine Compute-Logik und eine ganze Reihe von Schnittstellen. In vielen Fällen erfordert es sogar schnelle ADCs oder DACs und/oder DSP-Engines. Versal ist eine Adaptive Compute Application Plattform (ACAP), in der alle erwähnten Systemelemente in demselben Package monolithisch integriert sind und es somit ermöglicht, dass eine komplette Applikation auf einem Chip läuft - mit genauer Synchronisierung.

- Genaue Synchronisierung in nur einem Chip

- Die Synchronisierungsmetrik in Versal

- Transceiver-FIFOs beeinflussen die Genauigkeit