Das Edge braucht neue FPGAs

Eine Evolution reicht nicht, eine Revolution ist notwendig

Für rechenintensive Anwendungen in Datenzentren sind die modernsten FPGAs, die mithilfe der kleinsten Prozessgeometrien gefertigt werden, hervorragend geeignet. In Edge-Anwendungen sind aber ganz andere Parameter entscheidend, die sich mit älteren FPGAs nicht immer abdecken lassen.

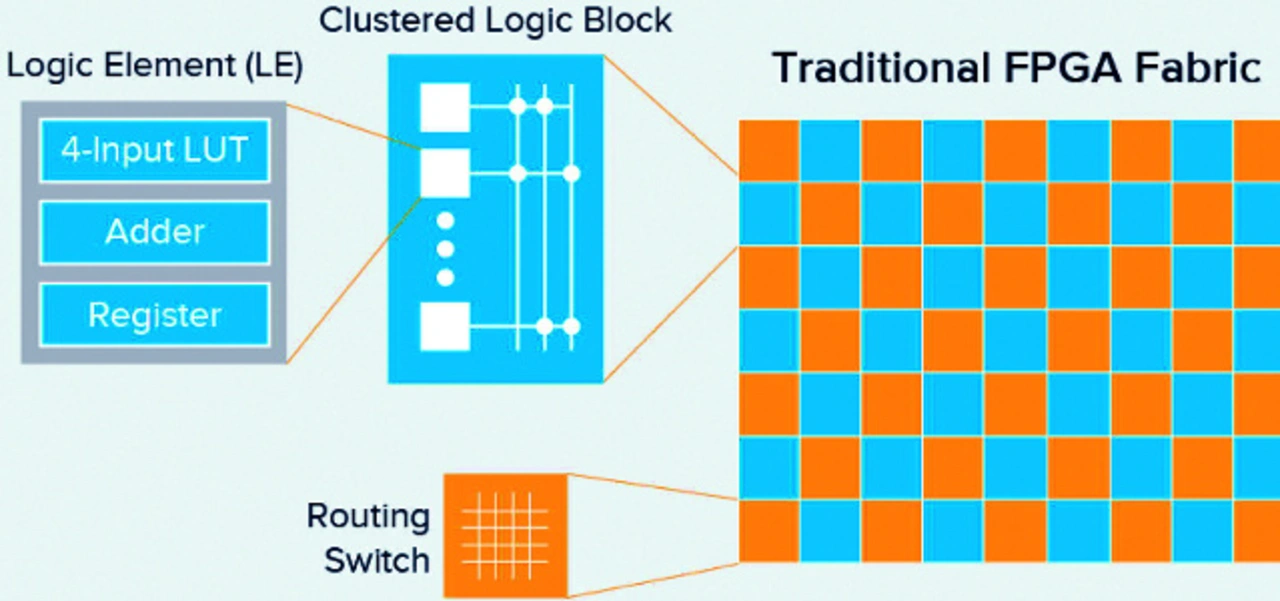

In Data-Center-Applikationen werden die größten und schnellsten FPGAs benötigt, um die Daten so schnell wie möglich verarbeiten zu können. Dafür sind sie optimal geeignet, da sie Prozesse parallel verarbeiten können. Deshalb setzen die etablierten PLD-Hersteller bei neuen FPGA-Familien immer auf kleinere Prozessstrukturen, um einerseits die Geschwindigkeit zu erhöhen und andererseits mehr Logik auf gleicher Fläche unterzubringen. Die eigentliche Struktur des FPGA ist aber seit Jahrzehnten die gleiche. Die vorhandenen Logikblöcke werden mit den zur Verfügung stehenden, festen Routing-Ressourcen verbunden. Hier findet also eine reine Evolution statt.

Im Edge wiederum sollen die Komponenten immer intelligenter werden. Denn nicht in allen Fällen ist es möglich, dass sich die Edge-Geräte mit der Cloud verbinden können oder wollen, sodass viele Edge-Applikationen vor Ort Daten auswerten, verarbeiten und Entscheidungen treffen müssen.

Im Gegensatz zu den Datenzentren sind bei Edge-Applikationen aber ganz andere Eigenschaften gefordert, wie beispielsweise ein geringer Platzbedarf, ein niedriger Stromverbrauch oder geringe Wärmeerzeugung.

Im Edge-Bereich werden heute meist Low-Density-FPGAs eingesetzt, die dieselbe Struktur wie die High-End-FPGAs aufweisen, nur mit weniger Routing-Ressourcen, da diese in den traditionellen FPGAs sehr viel Chipfläche in Anspruch nehmen. Das bedeutet, dass bei höherer Auslastung der Low-Density-FPGAs oder bei Designs mit vielen Verbindungen die heutigen Architekturen an ihre Grenzen stoßen.

Das Problem wird oft dadurch gelöst, dass der nächstgrößere Baustein gewählt wird, was sich negativ auf den Preis sowie den Stromverbrauch auswirkt.

Quantum-Architektur – ein revolutionärer Ansatz

Efinix hat eine vollkommen neue FPGA-Struktur entwickelt, die den Anforderungen im Edge-Bereich gerecht wird. Durch die neuartige XLR-Struktur (XLR: eXchangeable Logic and Routing) in der Quantum-Architektur können die Bausteine flexibler auf die verschiedenen Anforderungen hinsichtlich dem Routing reagieren.

Im Gegensatz zu den herkömmlichen FPGA-Architekturen kann in der Quantum-Architektur jedes Element als Logik (Look-up Table/Adder/Register) oder als Routing-Matrix benutzt werden. Das bedeutet: Dort, wo mehr Routing benötigt wird, werden mehr Elemente für die Routing-Matrix benutzt. Somit entstehen nicht die Verbindungsengpässe, wie es bei den herkömmlichen FPGAs üblich ist. Neben den flexiblen, kurzen Routing-Strukturen über die Elemente besitzt die Quantum-Architektur aber auch dedizierte Routing-Strukturen, um Taktsignale oder High-Fan-out-Signale (Clock Enable) mit geringem Skew auf dem kompletten Chip zu verteilen.

Jobangebote+ passend zum Thema

Darüber hinaus kann jedes Element für sich angesprochen werden, es gibt keine Zusammenfassung von Elementen, die nur das gleiche Steuersignal benutzen können. Die fein granulare Struktur gewährleistet eine höhere Auslastung der Bausteine, da hier keine Funktionen in Clustern zusammengefasst werden müssen. Die Quantum-Technologie ist so ausgelegt, dass die Bausteine auch mit einem Füllgrad von bis zu 90 Prozent noch problemlos geroutet werden können. Das Benutzen der Elemente als Routing-Matrix hat keinen Einfluss auf die zur Verfügung stehenden Logik-Ressourcen, da diese so ausgelegt sind, dass der Baustein bis zu 90 Prozent ausgelastet werden kann.

Diese neue revolutionäre, flexible Quantum-Technologie macht es möglich, die gleiche Logik auf der halben Fläche vergleichbarer FPGAs bei gleicher Siliziumstruktur zu packen.

Die flexible Routing-Struktur sorgt auch für höhere Systemgeschwindigkeiten, da das Routing optimiert erfolgt und die Verbindungen im Schnitt kürzer ausfallen. Und kürzere Verbindungen haben auch kleinere Kapazitäten zur Folge, was sich positiv auf die dynamische Verlustleistung auswirkt.

Die geringere Siliziumfläche sorgt außerdem für einen geringeren statischen Stromverbrauch, der in Edge-Applikationen sehr wichtig ist. Durch die Verwendung von Low-Power-Transistoren und die kleinere Fläche konnte der statische Stromverbrauch in der Trion-FPGA-Familie so optimiert werden, dass diese einen optimalen Mix zwischen Geschwindigkeit und Stromverbrauch bieten.

Die Trion-FPGA-Familie

Für batteriebetriebene Applikationen wurden die Bausteine der Trion-Familie mit 4k- und 8k-Logik-Elementen mit Ultra-Low-Power-Transistoren in einem Low-Power-Prozess mit 40-nm-Strukturen gefertigt. Diese besitzen eine statische Verlustleistung im 150-µW-Bereich. Die größeren FPGAs wurden mit Low-Power-Transistoren mit denselben Strukturgrößen produziert. Die statische Verlustleistung liegt in diesem Fall im unteren mW-Bereich.

- Eine Evolution reicht nicht, eine Revolution ist notwendig

- Anschluss von Kamerasensoren