RISC-V

Alternativen zu den Cores von SiFive

Fortsetzung des Artikels von Teil 1

Alleinstellungsmerkmal N22

Von allen angebotenen Andes-CPUs gibt es im absoluten Low-End ein konkurrenzloses Angebot im RISC-V-Universum: Der N22 ist ein winziger Mikrocontroller-Core mit nur zweistufiger Pipeline. In einem 28HPC+-Prozess braucht ein für geringe Energieaufnahme optimierter Chip, der mit 50 MHz läuft, 1,2 µW pro MHz und belegt nur 0,008 mm2 Siliziumfläche bei 15.000 Gattern. Eine leistungsoptimierte Version kann mit bis zu 800 MHz laufen, die Leistungsaufnahme steigt dann auf 3,5 µW/MHz und die Chipfläche wächst auf 0,013 mm2. Die Rechenleistung beträgt 3,97 CoreMarks pro MHz. Dieses Modell ist kompatibel zu dem RV32C-ISA, das komprimierte 16-bit-Befehle enthält.

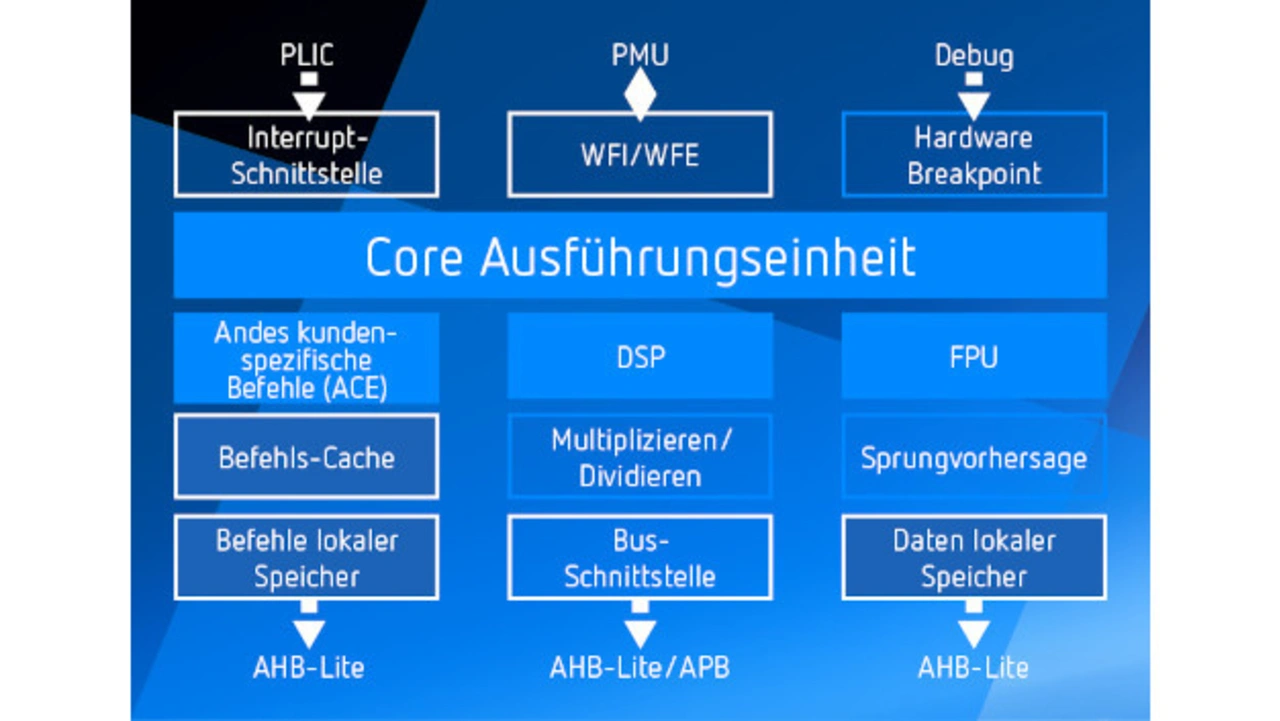

Entwickler können aus einer langen Liste von N22-Konfigurationsoptionen, einschließlich DSP-Erweiterung und FPU, wählen und den für sie besten Kompromiss zwischen Rechenleistung, Leistungsaufnahme und Chipfläche (PPA) wählen. Sie können 16 oder 32 Allzweck-Register (GPRs) instanziieren, und der Multiplizierer ist entweder in einer schnellen Version (1 Taktzyklus) oder einer kleineren Version (17 Taktzyklen) verfügbar.

Der N22 ermöglicht Entwicklern den Einsatz von 1 bis 32 KB L1-Befehlscaches, die als direkt gemappte oder Zwei-Wege-Caches konfigurierbar sind. Er kann lokale Befehls- und Datenspeichern von 1 KB bis 512 MB nutzen. Die PMP-Einheit (PMP: Physical-Memory-Protection) verwaltet 16 Speicherbereiche und die Sprungvorhersage bietet statische und dynamische Optionen.

Zur Behandlung von Interrupts können Entwickler den RISC-V-Standard Platform-Level-Interrupt-Controller (PLIC), den Core-Local-Interrupt-Controller (CLIC) oder beides verwenden. SiFive hat RISC-V International den CLIC als Ersatz für den ursprünglichen Core-Local-Interrupt-Block (CLINT) von RISC-V vorgeschlagen. Der CLIC unterstützt bis zu 256 Interrupt-Ebenen für jeden Privileg-Modus und 1.024 Interrupts pro Hardware-Thread, sowie selektives Vectoring und Prioritäts-Preemption. Der PLIC ist eher für Multicore-Prozessoren geeignet und bietet eine zentrale Steuerung und Interrupt-Weiterleitung an mehrere CPUs.

Für das Power-Management unterstützt der N22 die Andes PowerBrake-Technik, die eine digitale Steuerung der Leistungsdrosselung (Throttle) ermöglicht. Die Funktionen Wait-for-Interrupt (WFI) und Wait-for-Event (WFE) ermöglichen eine Software-basierte Steuerung von einer externen Power-Management-Einheit. Zu den weiteren Schnittstellenoptionen gehören ein 32-bit-AHB-Lite-Bus für die Systemintegration, eine schnelle E/A-Schnittstelle für den Zugriff mit geringer Latenz und APB für CPU-lokale Peripherie.

APB steht für Advanced Peripheral Bus. Sowohl der Advanced High-Performance Bus (AHB) als auch der APB sind Teil der Advanced Microprocessor Bus Architecture (AMBA). Obwohl sowohl der AHB als auch der APB zur AMBA gehören, unterscheiden sie sich in vielerlei Hinsicht: Der AHB verwendet eine parallele Vollduplex-Kommunikation, wogegen der APB massive Speicher-I/O-Zugriffe verwendet. Die APB wird hauptsächlich für die Verbindung mit einfacher Peripherie vorgeschlagen, weil er auf reduzierte Schnittstellenkomplexität und minimale Energieaufnahme zur Unterstützung von Peripheriefunktionen optimiert ist.

Das Debugging kann der Entwickler über einen 2-Draht-Serial-Debug-Port oder eine 4-Draht-JTAG-Debug-Schnittstelle vornehmen.

Erfolg von Andes bringt RISC-V-Architektur weiter nach vorne

Bei den Low-Power-Mikrocontrollern konkurriert der N22 mit dem Cortex-M3 von Arm. Ein leistungsoptimierter N22 ist etwa 20 Prozent kleiner ist als der M3 mit seiner dreistufigen Pipeline. Die Rechenleistung pro Taktzyklus des Andes-Cores ist 19 Prozent höher, in einem 28-nm-HPM-Design liefert er eine fast doppelt so hohe Rechenleistung/W ab.

Durch die Kombination von Open-Source-ISAs mit der ursprünglich für die AndeStar-CPUs entwickelten Technologie hat Andes die wachsende Popularität von RISC-V geschickt ausgenutzt. Es unterstützt die Standards der Foundation, aber seine Konfigurierbarkeit und seine kundenspezifischen Erweiterungen bieten zweifelsfrei einen Vorteil gegenüber anderen Anbietern.

SEGGER Microcontroller unterstützt das RISC-V-Ökosystem seit langem und zwar unter anderem mit dem Debugger J-Link, der alle Varianten von RV32 RISC-V Cores unterstützt, der IDE Embedded Studio für RISC-V (eine voll funktionsfähige Version von Embedded Studio), der Laufzeitbibliothek emRun und mit dem RTOS embOS.

Jobangebote+ passend zum Thema

- Alternativen zu den Cores von SiFive

- Alleinstellungsmerkmal N22