SiC-MOSFETs

Mythos Gate-Oxid-Zuverlässigkeit

Fortsetzung des Artikels von Teil 1

Bedeutung der t63-Lebendauer

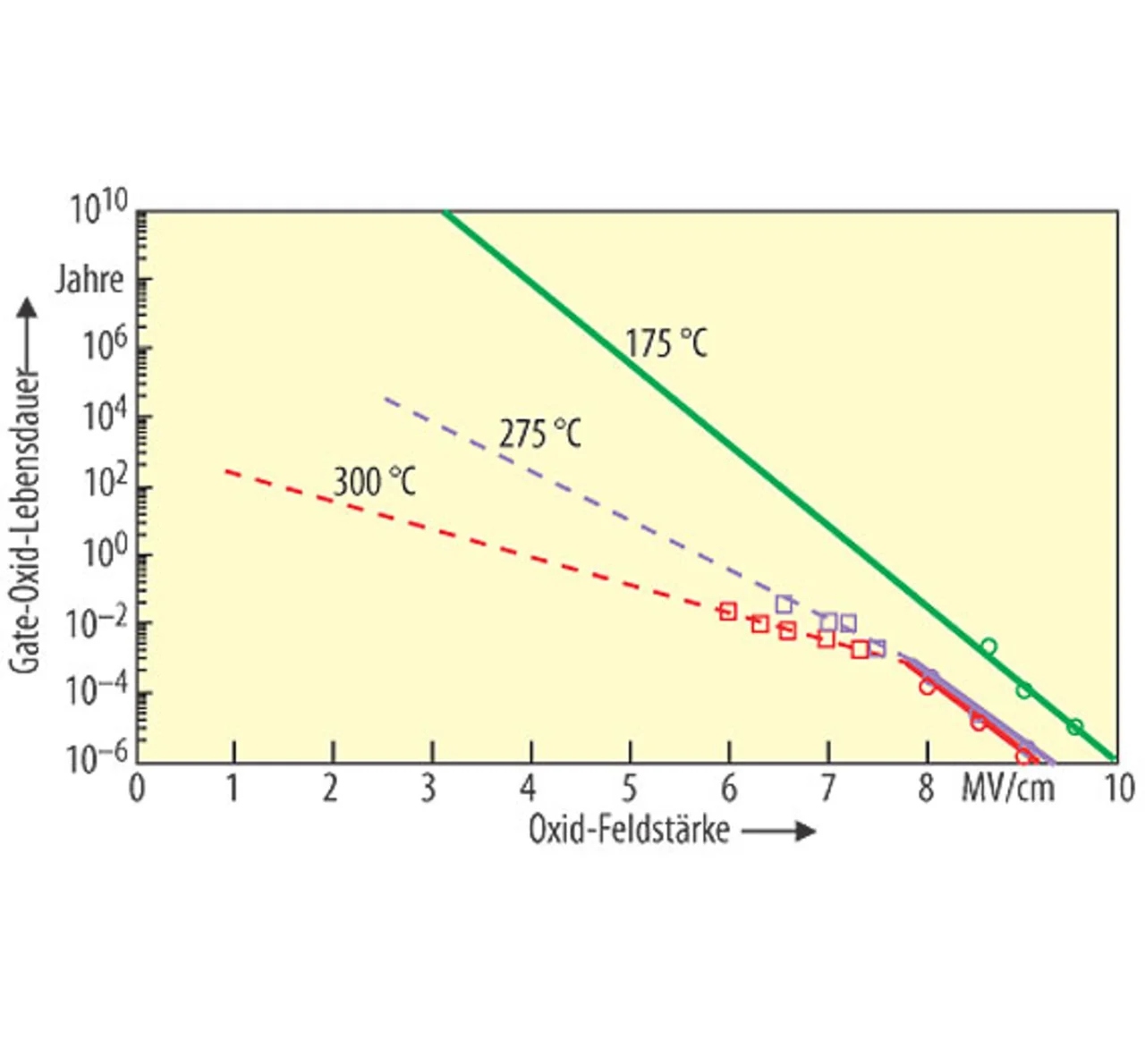

Die t63-Lebensdauer steht in exponentieller Beziehung zur elektrischen Feldstärke in der Oxidschicht. Sie kann einfach an die Datenpunkte bei den hohen Feldstärken angepasst und anschließend auf die Feldstärken im praktischen Einsatz extrapoliert werden.

Jobangebote+ passend zum Thema

Die TDDB-Statistiken von Z-FETs erweisen sich dabei als gut, wenn nicht sogar besser als die von Si-MOSFETs. Am wichtigsten ist jedoch die Aussage der Ausfallstatistik, dass bei 175 °C und der maximalen Oxidfeldstärke eine Lebensdauer von rund zehn Milliarden Jahren zu erwarten ist.

Zu den wichtigsten Fragen, die sich bei dieser Lebensdauerprojektion stellen, gehört die Genauigkeit der langen Extrapolation, die sich bei der Feldstärke immerhin über 5 MV/cm und bei der Lebensdauer über 12 Dekaden erstreckt. Leider ist die Lebensdauer bei Feldstärken unter 8 MV/cm so groß, dass sie sich einer Messung entziehen. Die einzige Möglichkeit, die Lebensdauern bei moderaten Feldstärken zu messen, besteht darin, die Temperatur anzuheben.

Die CVS-TDDB-Messung wird deshalb bei höheren Temperaturen wiederholt. Man geht dabei bis 300 °C, der zulässigen Höchsttemperatur der CVS-TDDB-Messanordnung von Cree. Bei 300 °C ist ein ungewöhnliches Phänomen zu beobachten: Die Ausfallstatistik wird nämlich bei Oxidfeld- stärken unter 7,5 MV/cm von einem zweiten Ausfall- mechanismus dominiert (Bild 4). Dieser sekundäre Ausfallmechanismus reduziert die 20-V-Lebensdauer um sechs Größenordnungen, mit potenziellen Auswirkungen auf die Gültigkeit der Extrapolation auf 175 °C.

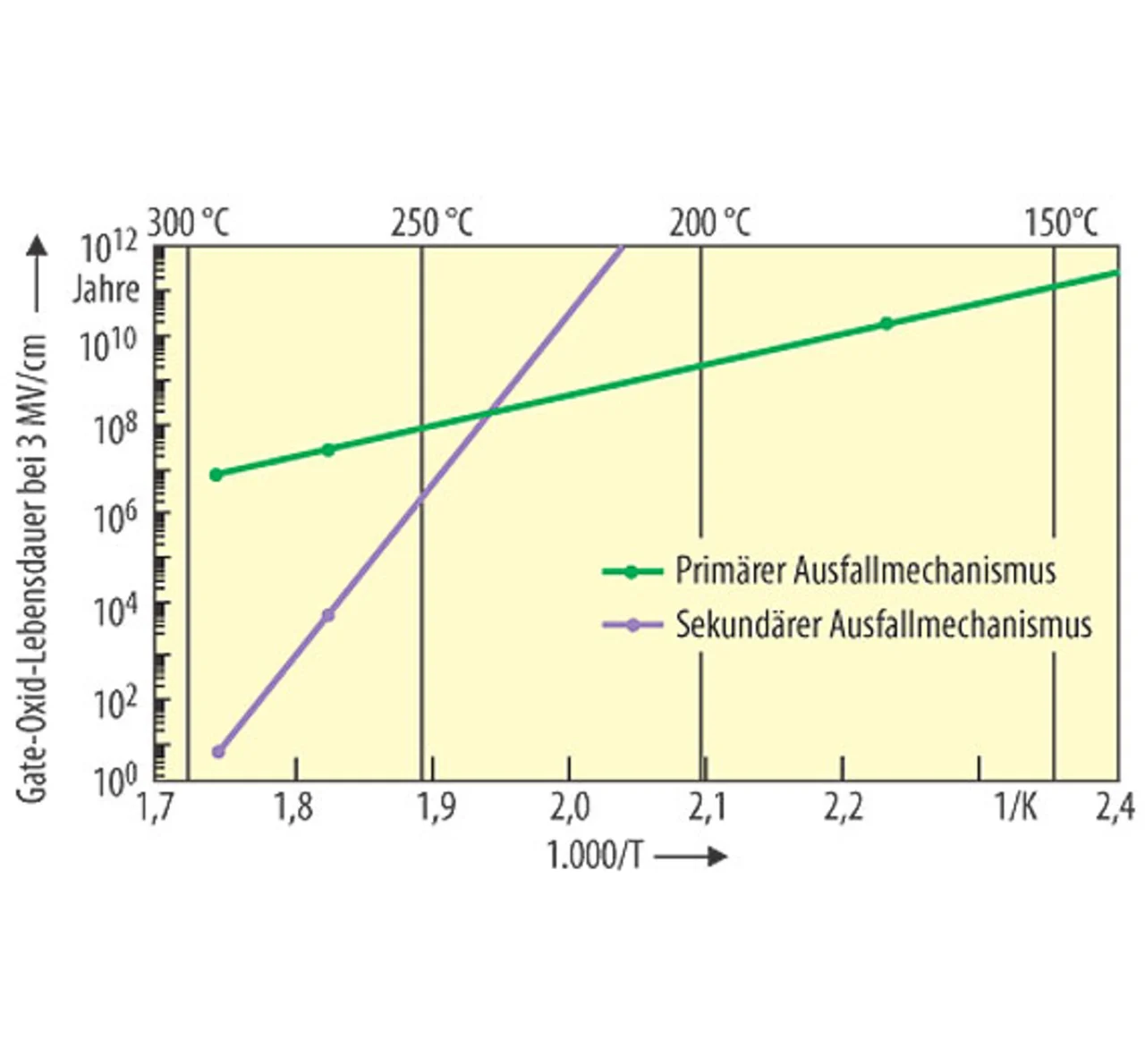

Die beste Möglichkeit, den sekundären Ausfallmechanismus zu berücksichtigen, besteht darin, die temperaturbedingte Beschleunigung zu überprüfen. Deshalb wird die Messung bei einer Temperatur von 275 °C wiederholt. Der sekundäre Ausfallmechanismus tritt auch hier auf, allerdings ungeachtet der lediglich um 25 °C abgesenkten Temperatur in deutlich geringerem Ausmaß. Dies deutet auf eine starke Temperaturabhängigkeit des sekundären Ausfall- mechanismus hin, während der primäre Ausfallmechanismus bei großen Feldstärken nur eine geringe Temperaturabhängigkeit an den Tag legt. Das Modellieren dieses Verhaltens als Arrhenius-Beziehung lässt erkennen, dass bei T > 240 °C der sekundäre Ausfallmechanismus dominiert (Bild 5).

Anders ausgedrückt: Es ist nicht zu erwarten, dass der sekundäre Ausfallmechanismus Auswirkungen auf die Extrapolation der 175-°C-Daten bei geringen Feldstärken hat.

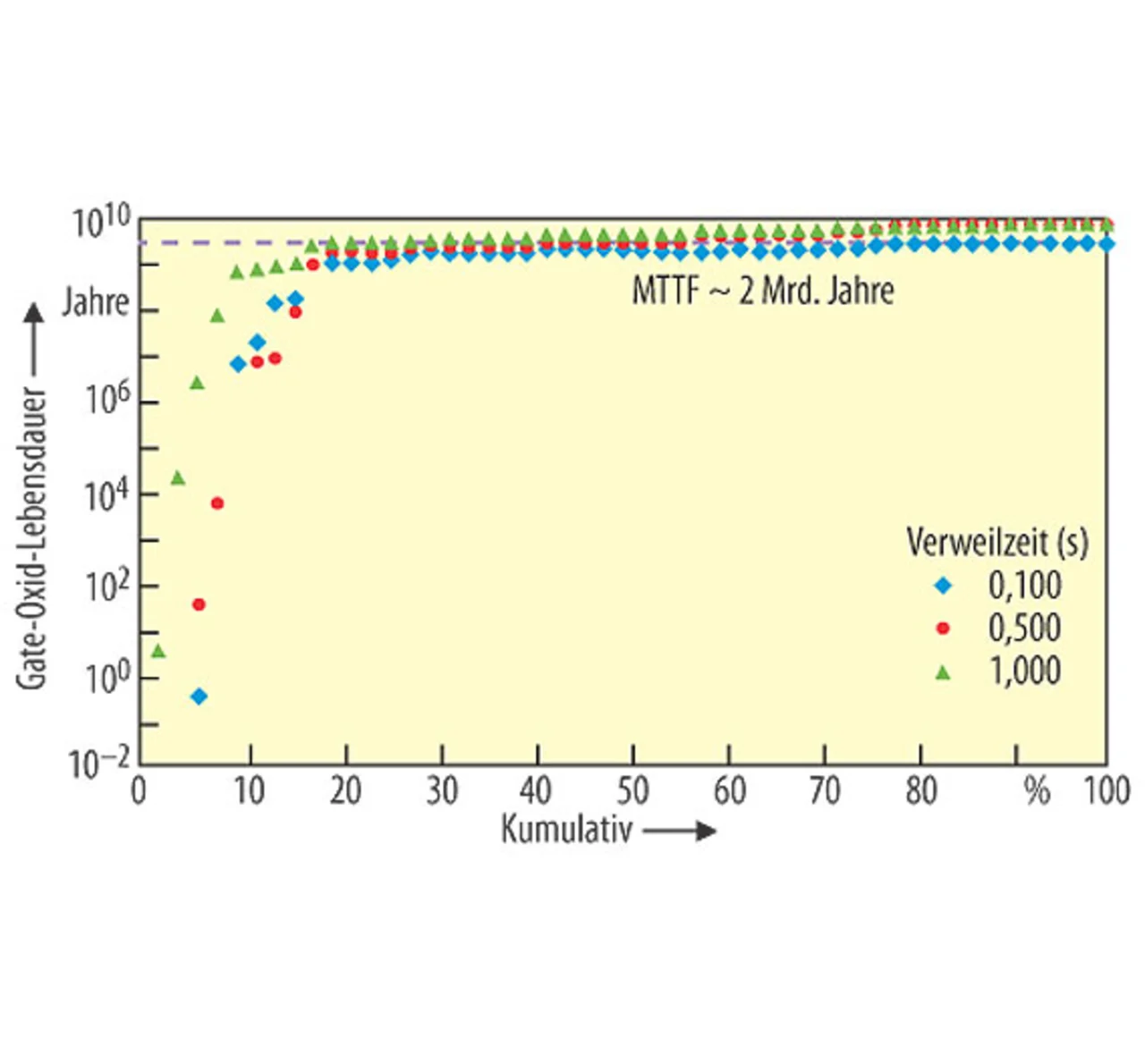

Die CVS-TDDB-Messung liefert eine Aussage über die spezifische Lebensdauer des SiC-MOSFET. Ebenso wichtig ist jedoch das Verständnis der Lebensdauer, die sich bei der Verteilung der Z-FETs aus der tatsächlichen Produktion ergibt. Für diese Betrachtung wurden ganze Wafer mit 1.200-V/80-mΩ-Z-FETs aus der laufenden Produktion bei 150 °C nach der Ramped-TDDB-Methode zum Totalausfall gebracht [3]. Die Ausfallstatistiken ergeben einen Feldbeschleunigungsfaktor von 5,2 MV/cm, was einen MTTF-Wert (Mean Time To Failure) von rund 400 Millionen Jahren bei einer Gate-Spannung von 20 V bedeutet (Bild 6). Auf der Grundlage dieser Ausfallstatistik wurde eine geeignete Screening-Methode entwickelt, mit der sich verhindern lässt, dass die wenigen Bauelemente mit Frühausfällen (Extrinsic Failure Mode) in den Verkauf gelangen.

Eine theoretisch vorhergesagte Durchschlagsfestigkeit des Dielektrikums, lange spezifische TDDB-Lebensdauern und effektive Screening-Prozeduren lassen gemeinsam die Aussage zu, dass es bei Z-FETs zu keinen dramatischen Gate-Ausfällen im Feld kommen wird. Hinzu kommt, dass die SiC-Gate-Oxide prinzipbedingt robuster sind als entsprechenden Si-Gate-Oxide. Dies zeigen die längere Lebensdauer beim CVS-TDDB-Test, die größere Immunität gegen -SEGR-Phänomene bei Neutronenbestrahlung [4] und die ESD-Beständigkeit der Klasse 2 nach dem Human-Body-Modell.

Stabilität der Bauelemente

Die JEDEC/AEC-Standards für die Qualifikation von Halbleiter-Bausteinen sehen vor, dass Bauelemente mit isolierten Gates, z.B. MOSFETs und IGBTs, einen HTGB-Stresstest (High Temperature Gate Bias) überstehen müssen. Dabei dürfen sich die Eigenschaften im On-Zustand um weniger als 20 % verändern, während sich der Leckstrom um 500 % ändern darf [5].

Bei Prüfungen nach der HTGB-Methode wird ein großer Bestand an 1.200-V/80-mΩ-Z-FETs (25 Prüflinge × 3 Fertigungslose) bei einem statischen Gate-Bias von 20 V für 1.000 Stunden einer Temperatur von 150 °C ausgesetzt. In periodischen Pausen werden dabei die elektrischen Eigenschaften bei Raumtemperatur gemessen.

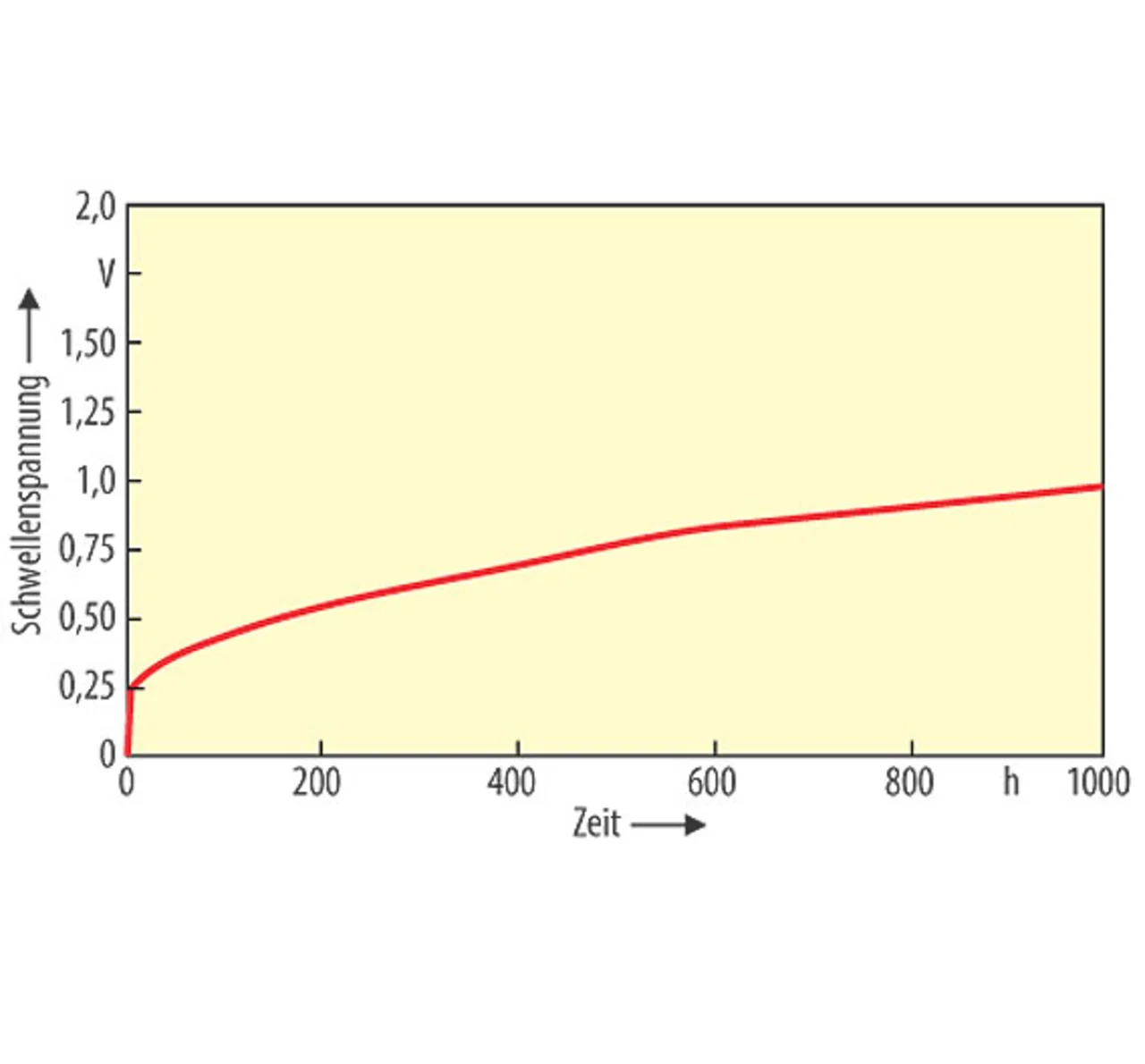

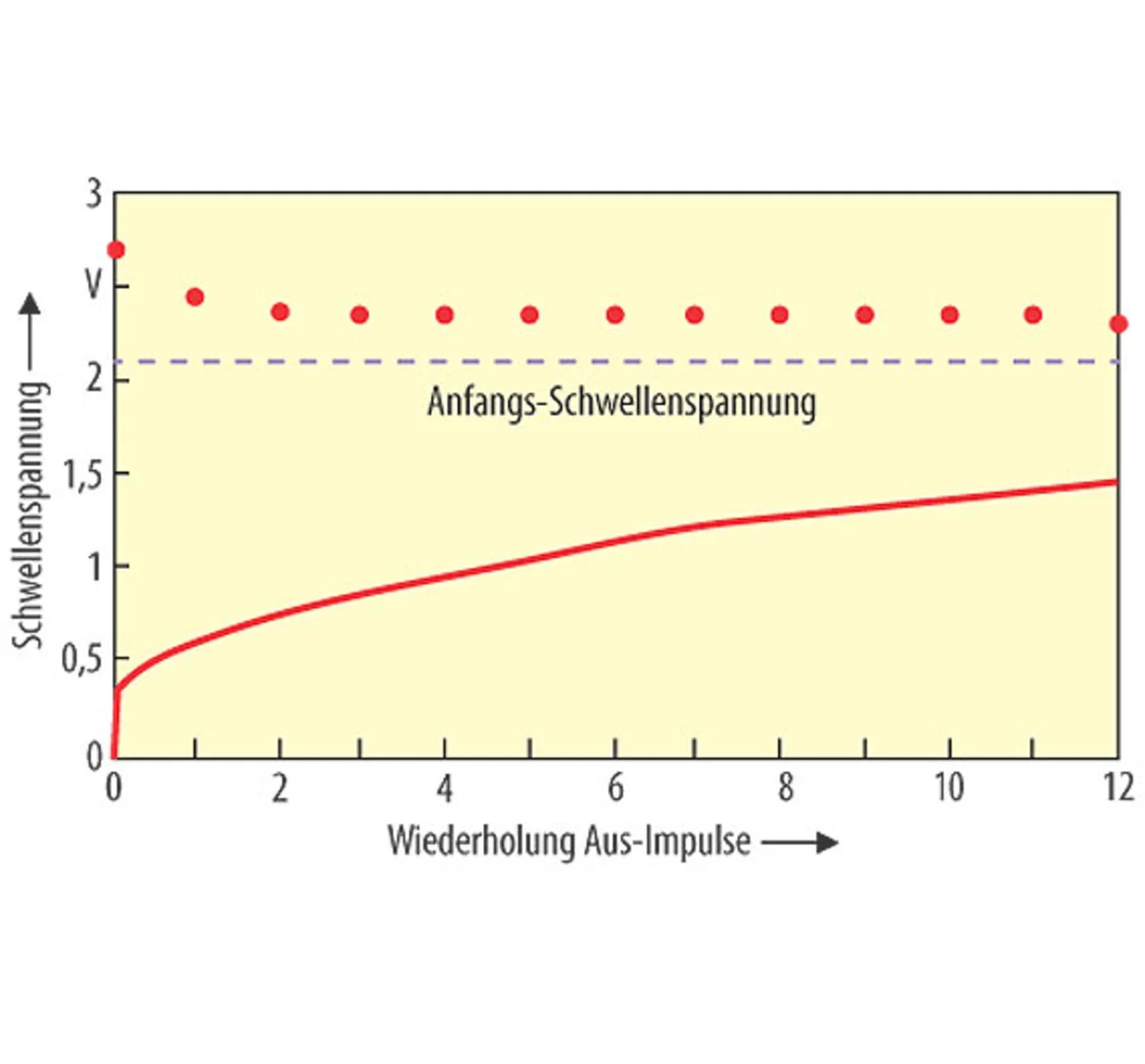

In Übereinstimmung mit den TDDB-Ergebnissen zeigt die HTGB-Prüfung, dass die Z-FETs den Test ohne einen einzigen Gate-Ausfall bestehen. Allerdings ist eine spürbare Änderung der elektrischen Eigenschaften zu verzeichnen, die sich aus einer erhöhten Schwellenspannung ergeben (Bild 7).

Die Werte des Bausteins selbst und der praktischen Applikation sind entsprechend umzurechnen, um die Auswirkungen dieses Phänomens korrekt auf das System des Endanwenders zu quantifizieren.

Im praktischen Einsatz dienen MOSFETs als Halbleiter-Schalter mit den beiden Schaltzuständen ‚ein‘ und ‚aus‘. Wenn im HTGB-Test eine positive Spannung am Gate liegt, was den Ein-Zustand des MOSFET simulieren soll, werden Elektronen von der SiO2/SiC-Grenzschicht angezogen. Dabei wird ein kleiner Teil der Elektronen in die Oxidschicht injiziert. Beim Durchqueren der Oxidschicht wird ein gewisser Prozentsatz der Elektronen von Haftstellen eingefangen, wodurch sich Bereiche mit konzentrierter negativer Ladung ausbilden. Diese Ansammlung zusätzlicher negativer Ladung im Oxid hat zur Folge, dass eine höhere Gate-Spannung angelegt werden muss, um den Baustein einzuschalten.

Diese höhere Schwellenspannung hat den Vorteil, dass der Leckstrom, der im Aus-Zustand beim Anlegen einer hohen Spannung fließt, geringer wird. Nachteilig ist dagegen der höhere spezifische Einschaltwiderstand RDS(on) des Bausteins. Im praktischen Einsatz ist der höhere RDS(on)-Wert allerdings nur dann kritisch, wenn der Baustein vom Aus- in den Ein-Zustand wechselt. Glücklicherweise sind die Energie-bänder der Oxidschicht im ausgeschalteten Zustand gegensinnig ausgerichtet, was das rasche Freisetzen der Elektronen erleichtert (Bild 8).

Ein nur 1 ms dauernder Aus-Impuls reicht bereits aus, um den Großteil der Ladung, die während eines 500-stündigen HTGB-Stresstests von den Haftstellen eingefangen wurde, freizusetzen. Die Schwellenspannung geht daraufhin rasch asymptotisch zurück. Die dann nur noch 0,25 V betragende Zunahme entspricht den bau-stein-immanenten Verschiebungen.

Das deutlich mehr als 99 % betragende Tastverhältnis in diesem Test - einer 500-stündigen Einschaltdauer stehen Aus-Phasen von wenigen Millisekunden gegenüber - lässt erkennen, dass aus diesem Phänomen keine Einschränkung des Tastverhältnisses resultiert. Als Antwort auf die weiteren Bedenken hinsichtlich der Frequenzbegrenzung entwickelte Cree ergänzend zur HTGB-Prüfung einen neuen Gate-Stresstest.

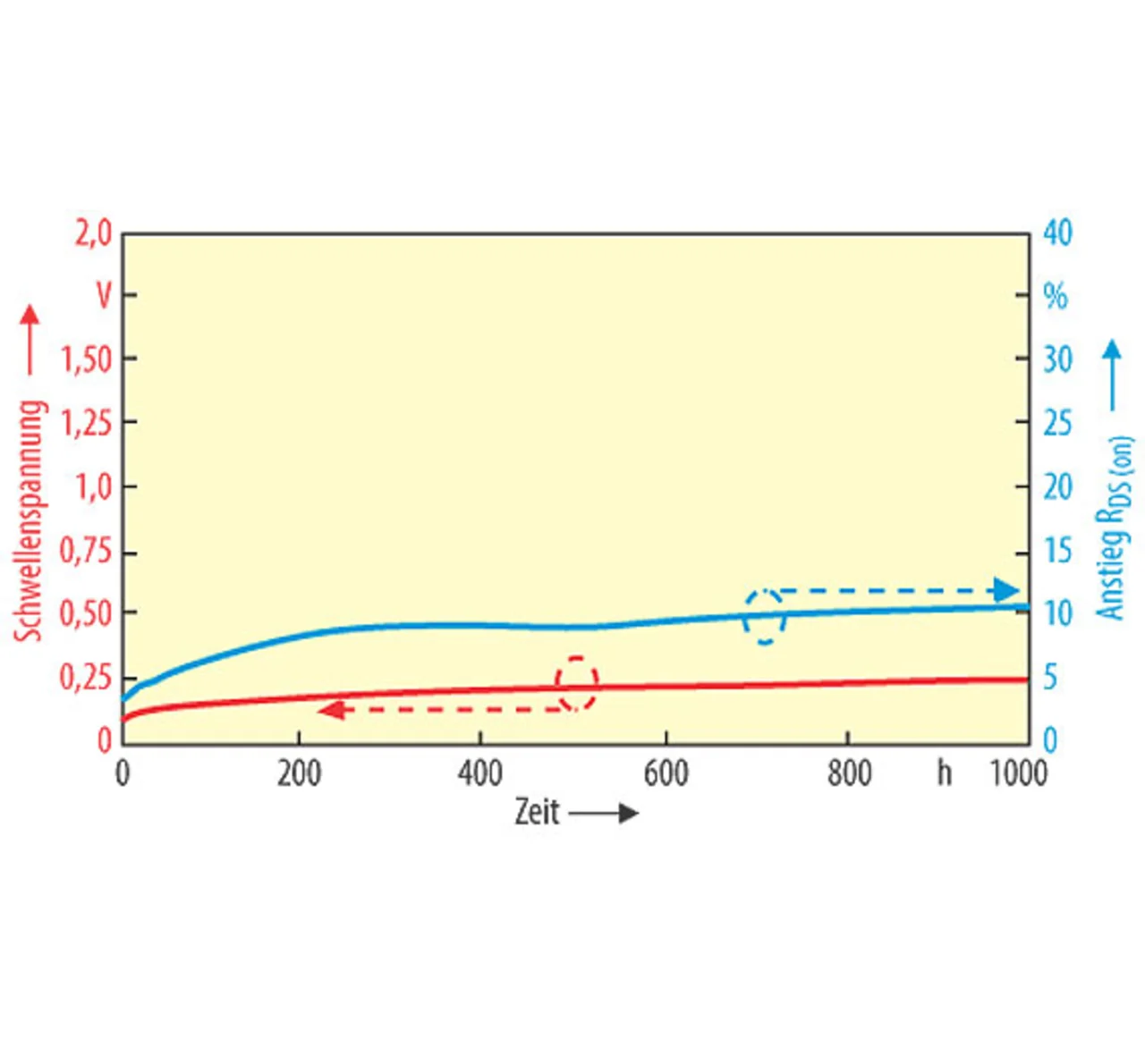

Die beste Aussage über die Stabilität des Bausteins lässt sich einholen, indem der Baustein einer ähnlichen Belastung wie im praktischen Einsatz ausgesetzt wird. Ein neu entwickelter Gate-Stresstest (High Temperature Gate Switching - HTGS), der die Verhältnisse im realen Einsatz besser widerspiegelt, soll die Stabilität des Bausteins mit einem Gate-Bias beurteilen. Die HTGS-Prüfanordnung ist identisch mit der des HTGB-Tests, nur wird die Gate-Spannung periodisch mit 20 kHz und 50 % Tastverhältnis zwischen 20 V und 0 V umgeschaltet, um realistischere Betriebsbedingungen zu simulieren. Im HTGS-Stresstest demonstrierte der Z-FET eine sehr gute Gate-Stabilität, mit einem Anstieg der Schwellenspannung von nur 0,25 V und einer 10-prozentigen Zunahme der Drain-Source-Spannung im Ein-Zustand. Dieser Wert liegt innerhalb der JEDEC/AEC-Akzeptanzgrenzen (Bild 9).

Entscheidender ist aber das Ergebnis des HTGS-Tests: Die einige zehn Kilohertz betragenden Schaltfrequenzen praktischer Applikationen stellen kein Problem dar, was das Phänomen des Einfangens und Freisetzens von Elektronen durch Haftstellen innerhalb der Oxidschicht angeht.

Zuverlässigkeit steigert Akzeptanz

Die Marktakzeptanz der SiC-MOSFET-Technologie wird nach wie vor durch negative Zuverlässigkeitsdaten beeinträchtigt. Der Z-FET wurde einer gründlichen Charakterisierung durch Cree unterzogen, wobei über die JEDEC-Mindeststandards hinausgehende Tests durchgeführt wurden. Dabei wurde eine hohe Zuverlässigkeit der Gate- und Drain-Elektroden unter Beweis gestellt. Durch unabhängige Tests staatlicher US-amerikanischer Labors wie dem National Institute of Standards and Technology und den Sandia National Labs gestützt, werden die aus dem Bereich der Si-MOSFETs auf die SiC-MOSFET-Technologie übertragenen Bedenken entkräftet.

- Mythos Gate-Oxid-Zuverlässigkeit

- Bedeutung der t63-Lebendauer

- Literatur & Autor