Halbbrücken-Durchflusswandler in ATX-Netzteilen

Die richtige Bauteil-Auswahl machts

Fortsetzung des Artikels von Teil 1

Verlustleistungsbetrachtung

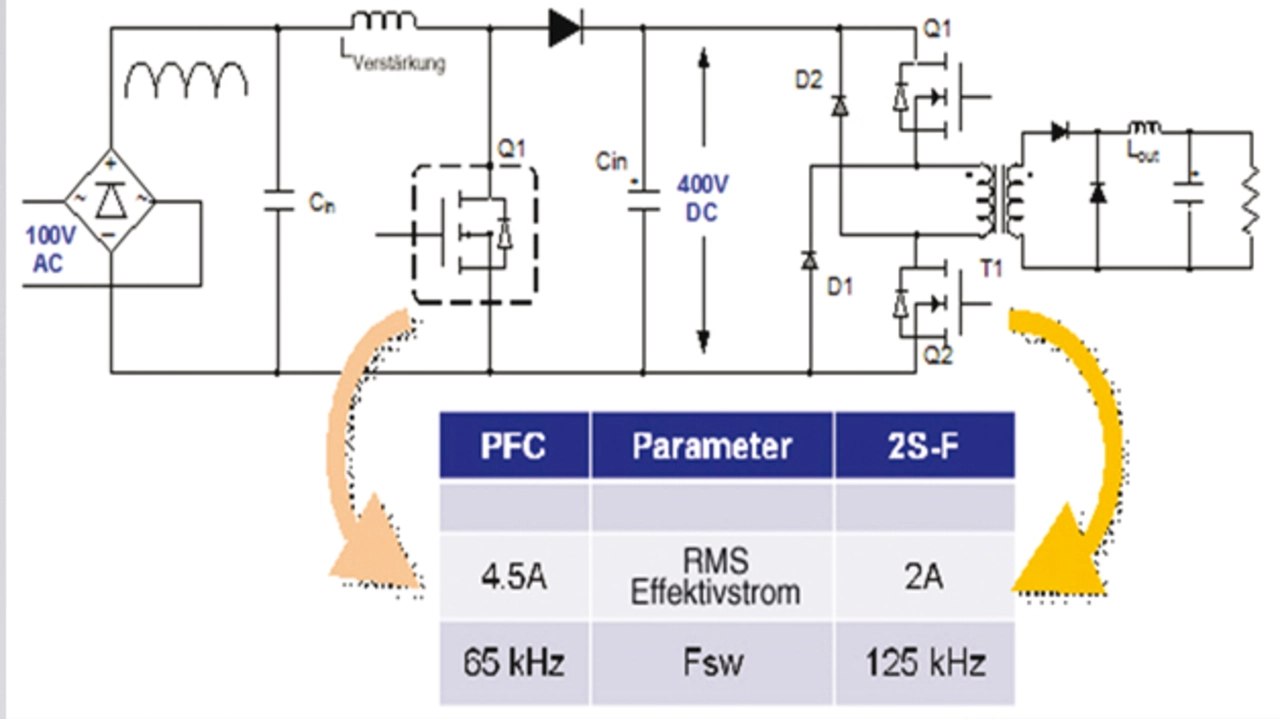

Bild 2 vergleicht die Verlustleistungen des Halbbrücken-Durchflusswandlers mit einem PFC-Eintaktflusswandler für ein 400-W-Netzteil. Die MOSFETs im Halbbrücken-Durchflusswandler tragen jeweils nur den halben Strom, während der Wandler doppelt so schnell taktet (125 kHz gegenüber 65 kHz, typisch). Wegen der Verdoppelung der Frequenz überwiegen beim Halbbrücken-Durchflusswandler die Schaltverluste.

Zur weiteren Veranschaulichung nehmen wir für den MOSFET in der PFC-Anwendung ein Bauteil im TO-220/TO-220F-Gehäuse mit einer maximalen Verlustleistung von 8 W. Im Idealfall betragen die Leitungsverluste zwischen 40% und 50% der Gesamtverluste bei Nennleistung. Wäre dies auch eine optimale Lösung für einen folgenden Halbbrücken-Durchflusswandler? Die Antwort ist ein klares Nein. In dieser Topologie würden Coss/Qoss und Qsw dazu führen, dass etwa 87% der Gesamtverluste auf die Schaltverluste entfielen. Die Leitungsverluste sind deswegen so gering, weil gegenüber dem MOSFET der PFC-Stufe nur der halbe Strom durch sie fließt. Ein solches Ungleichgewicht zwischen Leitungs- und Schaltverlusten ist für Effizienz und Kosten höchst unerwünscht.

In jedem Schaltkreis gibt es zwei Arten von Schaltverlusten. Die erste entsteht beim Ein- und Ausschalten durch das Produkt aus UDS und IDS. Diese Verluste werden auf Qsw umgerechnet, eine Kombination aus QGD und QGS, und repräsentieren die effektive Schaltlast des MOSFET. Diese Art der Schaltverluste hängt sowohl vom Verbraucher als auch von der Schaltfrequenz ab. Der zweite Art Schaltverluste tritt durch das Laden und Entladen der Ausgangskapazität des MOSFETs Coss zusammen. Bei ATX-Netzteilen folgt der beliebte Halbbrücken-Durchflusswandler dem PFC-Wandler mit einer Eingangsspannung von etwa 400 V. Dadurch kann diese Art Schaltverluste einen wesentlichen Teil der Gesamtverluste ausmachen. Dies gilt vor allem bei geringen Lasten, bei denen die Schaltverluste die Leitungsverluste übersteigen. Dieser Verlust ist im Wesentlichen unabhängig von der Last, und sowohl Qoss als auch Qsw müssen bei der Auswahl des entsprechenden MOSFETs berücksichtigt werden. Eine auf Verlustbeiträgen basierende anwendungsspezifische Figure-of-Merit (FoM) wäre: Leitungsverluste (RDS(on)) + Schaltverluste_1 (Qsw) + Schaltverluste_2 (Qoss).

Jobangebote+ passend zum Thema

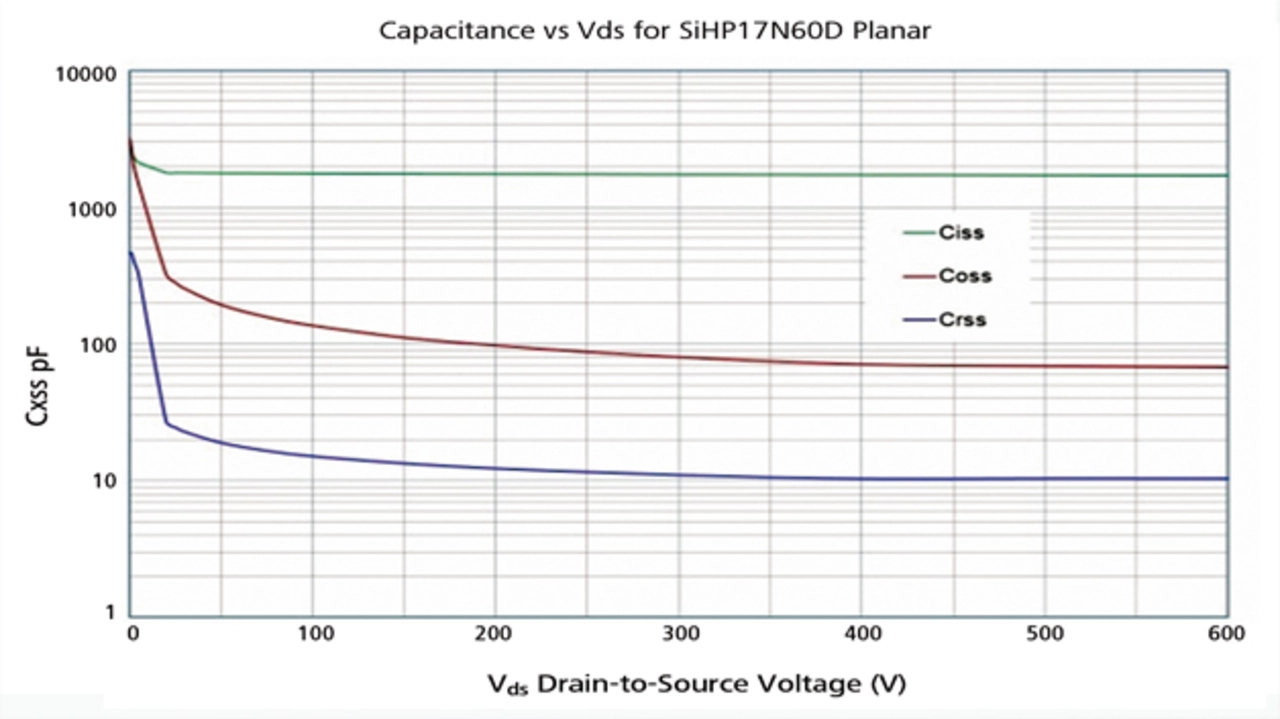

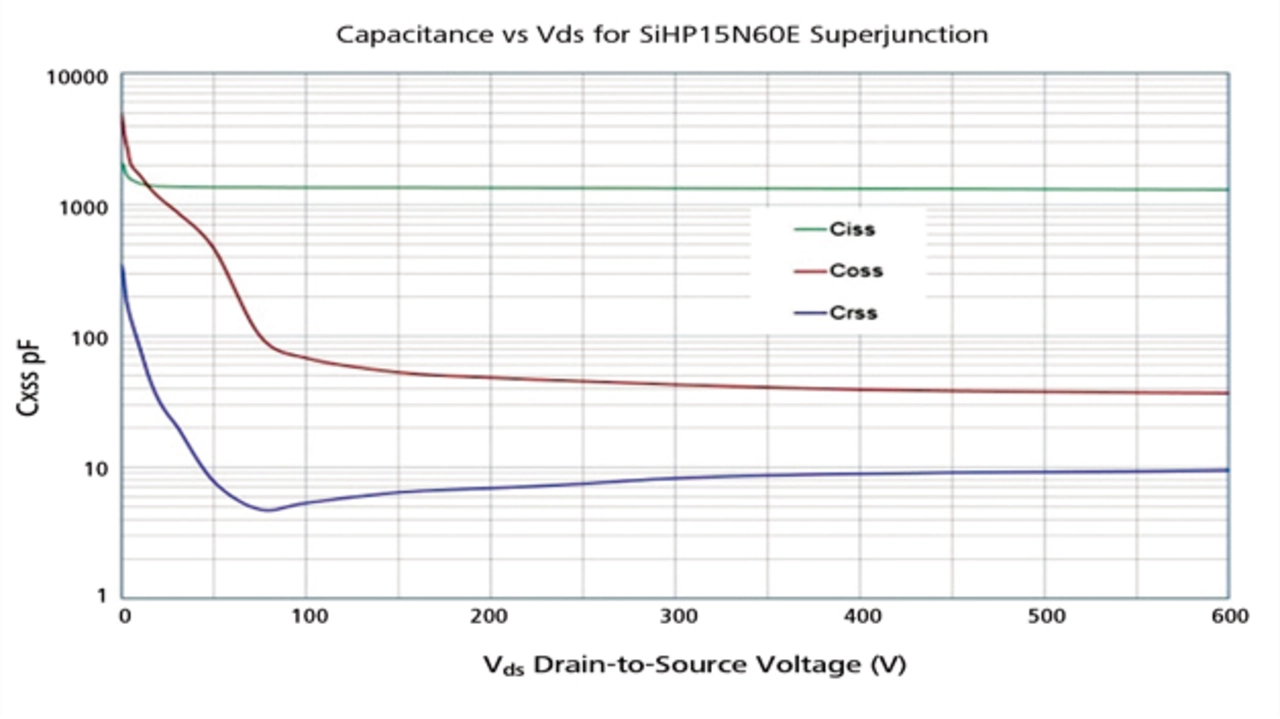

Die Coss eines Hochspannungs-MOSFETs variiert beträchtlich mit der angelegten Drain-Source-Spannung UDS. Diese Schwankungen sind bei Superjunction-MOSFETs viel größer als bei planaren Typen (Bild 3a und Bild 3b). Um die Nichtlinearität der parasitären Ausgangskapazität zu erklären, eignet sich folgende Näherungsgleichung: Poss = ½ ∙ Co(er) ∙ U² ∙ fsw. Die energiebezogene Kapazität Co(er) ist die effektive Kapazität, welche die gleiche gespeicherte Energie und die gleichen Verluste hat, wie die integrierte Coss des MOSFETs (0 V bis UDS) und ist in den Datenblättern angegeben. Es sei darauf hingewiesen, dass auf der parasitären Ausgangskapazität beruhende Verluste, die einen bedeutenden Teil der Gesamtverluste in jeder Hochspannungstopologie ausmachen, nicht in der Industriestandard-FoM (RDS(on) ∙ QG) berücksichtigt werden. Allerdings werden sie bei der anwendungsspezifischen Figure-of-Merit in dieser Analyse zur Bauteilauswahl integral verwendet.

- Die richtige Bauteil-Auswahl machts

- Verlustleistungsbetrachtung

- So wählt man die Bauteil richtig aus