Wichtig fürs Maschinenlernen

Hardware-Beschleuniger

Fortsetzung des Artikels von Teil 1

DNN-Beschleuniger mit variabler Genauigkeit

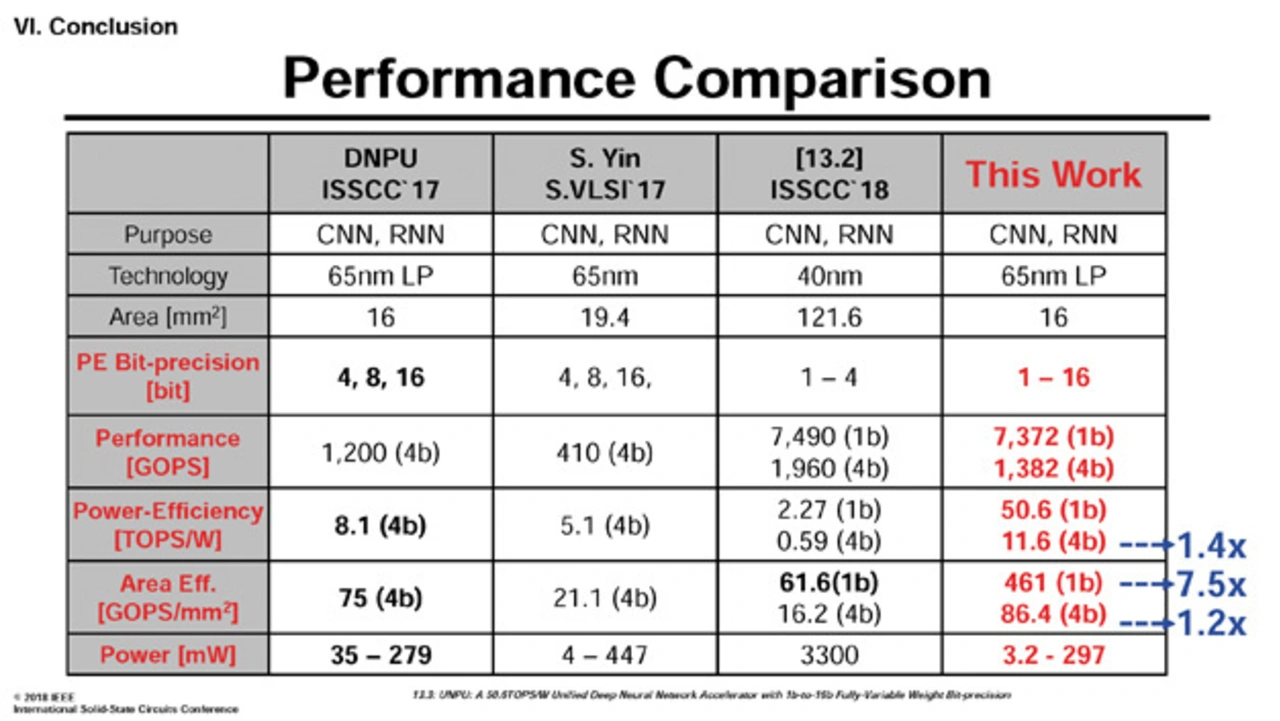

Wissenschaftler der südkoreanischen Universität KAIST wiederum haben mit UNPU (Unified Neural Processing Unit) einen DNN-Beschleuniger entwickelt, der CNN- (Convolutional Neural Network) und RNN-Ansätze (Recurrent Neural Network) mit einer einzigen programmierbaren Architektur unterstützt. Aus der Sicht von Jinmook Lee von KAIST sind die meisten bisherigen Beschleuniger lediglich in der Lage, entweder CLs (Convolutional Layers) oder FCLs (Fully Connected Layers) hardwareseitig zu beschleunigen; hybride DNNs, die beispielsweise auch RLs (Recurrent Layers) enthalten – wichtig für die Emotionserkennung – werden hingegen nicht über die Hardware unterstützt.

Bereits im letzten Jahr hatte das KAIST auf der ISSCC einen kombinierten CNN-RNN-Beschleuniger präsentiert, bei dem die rechenintensiven CLs und die speicherintensiven RLs oder FCLs separat optimiert und mit eigenen Core-Architekturen implementiert waren. Aber in diesem Fall sei die Zahl der Verarbeitungselemente (Processing Elements: PEs) für CLs und RLs begrenzt gewesen, wodurch die Gesamtleistung in Szenarien, in denen nur CLs oder nur RLs gebraucht wurden, suboptimal war. Zwar war bei dieser Entwicklung vorgesehen, dass die PEs für RLs in PEs für CLs oder umgekehrt konfiguriert werden konnten, aber die Rekonfiguration war nur teilweise möglich, was schlussendlich nur zu marginalen Leistungsverbesserungen führt. Außerdem habe dieses nur einen begrenzten Satz von Gewichte-Genauigkeiten unterstützt, entweder 8 oder 16 bit.

Eine geringere Genauigkeit der Gewichte kann den Durchsatz und die Energieeffizienz erhöhen; also ist es wünschenswert, die Genauigkeit der Gewichte den Anforderungen anpassen zu können. Und genau das haben die Wissenschaftler bei UNPU (Unified Neural Processing Unit) realisiert: UNPU unterstützt CLs, RLs und FCLs mit einer vollständig variablen Genauigkeit der Gewichte, und zwar zwischen 1 und 16 bit.

Jobangebote+ passend zum Thema

Darüber hinaus setzen die Wissenschaftler darauf, die IFs (Input Features) wiederzuverwenden, weil das bei einer geringen Genauigkeit effizienter ist als die Gewichte-Wiederverwendung. Die Operationen von CLs werden identisch mit denen von RLs und FCLs, wenn die IFs der CLs in einen eindimensionalen Vektor vektorisiert werden.

Zudem werden LBPEs genutzt (LUT-based Bit-Serial PEs), weil damit laut Lee im Vergleich zu Festkomma-MACs energieeffizientere DNN-Operationen möglich sind. Wird mit einer 16-bit-Genauigkeit gearbeitet, liegt die Leistungsaufnahme (pJ/MAC) von LBPE-MACs um 23,1 Prozent niedriger als mit Fixed-Point-MACs, bei einer 1-bit-Genauigkeit beträgt der Unterschied sogar 53,6 Prozent. Und sie nutzen einen AFL (Aligned Feature Loader), um Zugriffe auf externen Speicher zu minimieren.

Der UNPU kann mit Versorgungsspannungen von 0,63 bis 1,1 V arbeiten; die maximale Taktfrequenz ist mit 200 MHz angegeben. Die Leistungsaufnahme bei 0,63 V beziffert Lee mit 3,2 mW, bei 1,1 V mit 297 mW. Die Leistungseffizienz, mit CLs (5 x 5 Kernel) in Hinblick auf die PE-Auslastung gemessen, beträgt bei einer 16-bit-Genauigkeit 3,08, bei einer 4-bit-Genauigkeit 11,6 und bei 1 bit 50,6 TOPS/W. UNPU wurde mit Hilfe eines 65-nm-Prozesses gefertigt; Fläche: 16 mm².

- Hardware-Beschleuniger

- DNN-Beschleuniger mit variabler Genauigkeit